Fターム[5F140CB02]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | 素子分離構造 (5,334) | チャネルストッパ (158)

Fターム[5F140CB02]の下位に属するFターム

不純物分布 (19)

Fターム[5F140CB02]に分類される特許

1 - 20 / 139

半導体装置とその製造方法

【課題】ゲート高さが低いため製造容易で、ゲート−コンタクト間の容量を抑制し、ゲート−コンタクト間の短絡を抑制した半導体装置を提供する。

【解決手段】半導体装置の製造方法は基板上にFin型半導体層を形成する。Fin型半導体層に交差するダミーゲートが形成される。Fin型半導体層にソースおよびドレインが形成される。ダミーゲート上に層間絶縁膜を堆積した後、ダミーゲートの上面を露出させる。ダミーゲートを除去してゲートトレンチを形成する。ゲートトレンチ内のFin型半導体層の上部をリセスする。ゲートトレンチ内のFin型半導体層の表面にゲート絶縁膜を形成する。ゲート電極をゲートトレンチ内に充填する。ゲート電極をエッチングバックすることによってゲート電極を形成する。ゲート電極の上面の高さはソースおよびドレインにおけるFin型半導体層の上面の高さ以下かつゲートトレンチ内のFin型半導体層の上面の高さ以上である。

(もっと読む)

半導体装置とその製造方法

【課題】製造プロセスが容易であり、かつ、Fin型FETおよび従来型トランジスタを混載した半導体記憶装置を提供することである。

【解決手段】半導体記憶装置は第1の領域および第2の領域を備える。メモリ部のトランジスタは第1導電型のFin型半導体層を備える。第1導電型の第1のソース層および第1のドレイン層はFin型半導体層の両端に設けられる。第1のゲート電極はFin型半導体層の両側面に設けられる。第2導電型のパンチスルーストッパ層は第1のゲート電極およびFin型半導体層の下に設けられている。パンチスルーストッパ層の不純物濃度は第1のソース層および第1のドレイン層の下の不純物濃度よりも高い。周辺回路部のトランジスタは、第2のゲートトレンチを備える。第1導電型の第2のソース層および第1導電型の第2のドレイン層は、第2のゲートトレンチの両側に設けられる。第2のゲート電極は、第2のゲートトレンチ内に充填される。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】高電圧動作時においても電流コラプス現象を十分に抑制し、高耐圧及び高出力を実現する信頼性の高い化合物半導体装置を得る。

【解決手段】HEMTは、化合物半導体層2と、開口を有し、化合物半導体層2上を覆う保護膜と、開口を埋め込み、化合物半導体層2上に乗り上げる形状のゲート電極7とを有しており、保護膜は、酸素非含有の下層絶縁膜5と、酸素含有の上層絶縁膜6との積層構造を有しており、開口は、下層絶縁膜5に形成された第1の開口5aと、上層絶縁膜6に形成された第1の開口5aよりも幅広の第2の開口6aとが連通してなる。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】ノーマリオフ動作を実現しながら良好な伝導性能を得ることができる化合物半導体装置及びその製造方法を提供する。

【解決手段】化合物半導体装置の一態様には、基板1と、基板1上方に形成された電子走行層3及び電子供給層5と、電子供給層5上方に形成されたゲート電極11g、ソース電極11s及びドレイン電極11dと、電子供給層5とゲート電極11gとの間に形成されたp型半導体層8と、電子供給層5とp型半導体層8との間に形成され、電子供給層5よりもバンドギャップが大きい正孔障壁層6と、が設けられている。

(もっと読む)

スイッチ装置

【課題】GaNトランジスタを理想的な還流ダイオードとして動作させ、低損失のスイッチ装置を実現できるようにする。

【解決手段】スイッチ装置は、窒化物半導体素子301と、窒化物半導体素子301を駆動する駆動部302とを備えている。窒化物半導体素子301は、第1のオーミック電極、第2のオーミック電極及び第1のゲート電極を有している。駆動部302は、第1のゲート電極にバイアス電圧を印加するゲート回路311と、第1のゲート電極と第1のオーミック電極との間に接続され、双方向に電流を流すスイッチ素子312とを有している。駆動部302は、第1のオーミック電極から第2のオーミック電極への電流を通電し且つ第2のオーミック電極から第1のオーミック電極への電流を遮断する動作を行う場合には、スイッチ素子312をオン状態とする。

(もっと読む)

GaN系半導体装置

【課題】p型のGaN系半導体装置を提供する。

【解決手段】第1導電型のキャリアガスが発生した第1チャネル層106と、第1チャネル層106上に、第1チャネル層106よりバンドギャップが大きいGaN系半導体で形成されたバリア層110と、バリア層110上に、バリア層110よりバンドギャップが小さいGaN系半導体で形成され、第2導電型のキャリアガスが発生した第2チャネル層112と、第2チャネル層112にオーミック接続する第1ソース電極118と、第2チャネル層にオーミック接続する第1ドレイン電極120と、第1ソース電極118及び第1ドレイン電極120の間に形成された第1ゲート電極122と、を備え、第2導電型のキャリアガスのキャリア濃度が、第1ゲート電極122の下の領域で、第1ソース電極118及び第1ドレイン電極120の間の他の領域より低く、かつ、第1ゲート電極122により制御されるGaN系半導体装置。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】ゲート電極によるチャネルのポテンシャル制御性を大幅に向上させ、信頼性の高い所期の高耐圧及び高出力を得ることのできる化合物半導体装置を実現する。

【解決手段】AlGaN/GaN・HEMTは、Si基板1と、Si基板1の上方に形成された電子走行層2bと、電子走行層2bの上方に形成された電子供給層2cと、電子供給層2cの上方に形成されたソース電極4、ドレイン電極5及びゲート電極6とを含み構成されており、電子走行層2cは、平面視でソース電極4とドレイン電極5とを結ぶ方向と交差する方向に並ぶ複数の段差、例えば第1の段差2ca、第2の段差2cb、第3の段差2ccを有する。

(もっと読む)

半導体装置およびその製造方法

【課題】第1のトランジスタと第2のトランジスタが、ぞれぞれのドレイン領域とソース領域を共有して同一の半導体基板上に形成される構成の半導体装置の製造において、それぞれのトランジスタのソース領域およびドレイン領域の直下に埋め込み絶縁膜を効率的に形成できる製造方法を提供する。

【解決手段】半導体基板上にそれぞれのトランジスタのソース領域およびドレイン領域に対応してトレンチを形成し、前記トレンチをSiGe混晶層と半導体層を順次形成することにより充填し、さらに第1のトランジスタのソース領域および第2のトランジスタのドレイン領域直下のSiGe混晶層を、素子分離溝を介して選択エッチングにより除去し、第1のトランジスタのドレイン領域および第2のトランジスタのソース領域として共有される拡散領域直下のSiGe混晶層を、前記拡散領域に形成した孔を介して選択エッチングし、除去する。

(もっと読む)

半導体装置

【課題】横型構造のパワートランジスタにおいて、寄生サイリスタのラッチアップ耐量を改善するとともに、ターンオフ時間を短縮する。

【解決手段】エミッタ電極(21)下部に設けられるn+エミッタ層(6)を、所定の間隔で互いに離れて配置される単位領域(60)で構成する。単位領域においてエミッタ電極とのコンタクトを取るとともに、pベース層(5)よりも高濃度でp+層(45)を少なくともエミッタ層の下方に設ける。

(もっと読む)

半導体装置およびその製造方法

【課題】ゲート動作に関与する結晶表面における表面電荷蓄積を大幅に低減し、ピンチオフ特性が得られる、高性能のInN系FETを提供すること。

【解決手段】チャネル層としてInN系半導体を含む電界効果トランジスタである半導体装置であって、InN系半導体でなるチャネル層2の表面(c面)に、段差を形成して窒化物半導体の六方晶結晶のa面もしくはm面でなる側壁面2aを形成し、この側壁面2aにゲート電極6が配置され、ゲート電極6を挟むようにソース電極3とドレイン電極4がc面上に形成されている。

(もっと読む)

半導体装置の製造方法

【課題】500keV〜3000keVのエネルギーイオン注入を行っても、目的とする領域に精度良く、不純物拡散領域を形成することができる半導体装置の製造方法を提供すること。

【解決手段】半導体基板10の表面に、イオン注入を行うための開口部42Aを持つレジストパターン42を形成する工程であって、開口部42Aの縁部42Bがイオン注入予定領域50の外縁部50Aよりも内側に位置するようにして、レジストパターン42を形成する工程と、レジストパターン42から露出した半導体基板10の表面の少なくとも一部に対して、ウエットエッチングを施す工程と、レジストパターン42をマスクとし、500keV〜3000keVのエネルギーイオン注入により、半導体基板10の深部に不純物拡散領域(例えばN−型不純物拡散領域12)を形成する工程と、を有する半導体装置の製造方法。

(もっと読む)

半導体装置及びその製造方法

【課題】本発明の実施形態は、電気抵抗を低減させることができる半導体装置及びその製造方法を提供する。

【解決手段】実施形態によれば、第1導電型のチャネル形成領域と、第2導電型の第1オフセット領域と、前記第1オフセット領域の表面に埋め込まれている第1絶縁膜領域と、前記第1オフセット領域と前記第1絶縁膜領域との間に設けられた第1ライナ層と、前記第1絶縁膜領域を挟んで前記チャネル形成領域とは反対側に形成され、前記第1オフセット領域よりも不純物濃度の高い第2導電型の第1半導体領域と、前記チャネル形成領域を挟んで前記第1半導体領域とは反対側に形成され、前記第1オフセット領域よりも不純物濃度の高い第2導電型の第2半導体領域と、前記チャネル形成領域上及び前記第1オフセット領域上に形成されたゲート絶縁膜と、前記ゲート絶縁膜上に形成されたゲート電極と、を備えたことを特徴とする半導体装置が提供される。

(もっと読む)

半導体装置

【課題】LDMOSトランジスタのESD耐量の改善を図る。

【解決手段】ゲート電極5とレジストマスクによりP型ベース層2に、中心部に複数の開口部7を有するラダー形状のN+型ソース層3を形成する。開口部7に該開口部7を埋設するP+型コンタクト層4を形成する。このとき、開口部7の端部、即ちP+型コンタクト層4の端部からN+型ソース層3の端部までの距離を所定の距離にする。所定の距離とは該距離の増加と共に増大するLDMOSトランジスタのHBM+耐量が飽和し始める距離である。

(もっと読む)

半導体装置の製造方法

【課題】 トランジスタの深さ方向の濃度プロファイルが均一化され、閾値電圧ばらつきを改善した半導体装置の製造方法を提供する。

【解決手段】MOS型トランジスタを備えた半導体装置の製造方法において、MOS型トランジスタは、第1導電型の第1シリコン基板と、第1シリコン基板に対して積層された第2導電型の第2シリコン基板と、ウェル領域と、ソース・ドレイン領域と、チャネル領域と、ゲート電極と、からなるMOS型トランジスタであって、第1シリコン基板と第2シリコン基板とを貼り合せる工程と、第2シリコン基板をチャネル領域の深さまで研磨する工程と、第2シリコン基板に対して不純物イオン注入することによりソース・ドレイン領域を形成する工程と、チャネル領域上にゲート電極を形成する工程と、を含む。

(もっと読む)

半導体装置

【課題】ドレインオフセット領域を有する高周波増幅用MOSFETにおいて、微細化およびオン抵抗低減を図る。

【解決手段】ソース領域10、ドレイン領域9およびリーチスルー層3(4)上に電極引き出し用の導体プラグ13(p1)が設けられている。その導体プラグ13(p1)にそれぞれ第1層配線11s、11d(M1)が接続され、さらにそれら第1層配線11s、11d(M1)に対して、導体プラグ13(p1)上で裏打ち用の第2層配線12s、12dが接続されている。

(もっと読む)

半導体装置

【課題】ドレインオフセット領域を有する高周波増幅用MOSFETにおいて、微細化およびオン抵抗低減を図る。

【解決手段】ソース領域10、ドレイン領域9およびリーチスルー層3(4)上に電極引き出し用の導体プラグ13(p1)が設けられている。その導体プラグ13(p1)にそれぞれ第1層配線11s、11d(M1)が接続され、さらにそれら第1層配線11s、11d(M1)に対して、導体プラグ13(p1)上で裏打ち用の第2層配線12s、12dが接続されている。

(もっと読む)

半導体装置の製造方法

【課題】不純物イオン注入時に形成されたフレンケル型結晶欠陥を終端させ、ボロンの増速拡散を抑制することで、逆短チャンネル効果を改善した半導体装置の製造方法を提供する。

【解決手段】MOS型トランジスタを備えた半導体装置の製造方法において、MOSトランジスタは、P型ウェル領域と、N型ソース・ドレイン領域と、チャネル領域と、ゲート電極と、からなるNMOSトランジスタであって、N型ソース・ドレイン領域を不純物イオン注入により形成する工程と、ソース・ドレイン領域と同一領域に、ハロゲン元素をイオン注入する工程と、ソース・ドレイン領域を活性化させるための活性化熱処理工程とを含む。

(もっと読む)

半導体集積装置の製造方法及び半導体集積装置

【目的】製造工程数を増加させることなく、高い耐圧の半導体集積装置を製造することが可能な半導体集積装置の製造方法、及び半導体集積装置を提供することを目的とする。

【構成】半導体基板の表面に形成されている拡散領域に接するボディ領域と、埋込拡散層との間に、半導体基板よりも電気抵抗が低いシンカー層を設ける。又、かかるシンカー層を形成すべく半導体基板表面に設けるレジスト膜に対して、その側面と半導体基板の底面との交叉角が90度未満となるテーパー加工処理を施す。

(もっと読む)

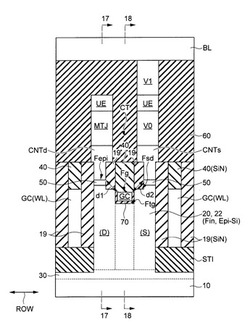

チャネルが埋込み誘電体層を通り抜けているメモリセル

【課題】浮動チャネルまたは浮動ゲートを持つFET(Field Effect Transistor(電界効果トランジスタ))により形成されたメモリセル、複数のメモリセルから成るメモリアレイの提供。

【解決手段】絶縁層BOXによってベース基板から隔てられた半導体材料の薄層を含むセミコンダクタ・オン・インシュレータ基板と、少なくとも基本的にセミコンダクタ・オン・インシュレータ基板の薄層中に配列されたソース領域S、ドレイン領域D、トレンチがその中に作られているチャネルC、トレンチ中のゲート領域Gを含むFETトランジスタを備え、トレンチが、絶縁層BOXを越えベース基板の深さの中に延びていること、チャネルが、絶縁層の下でソース領域とドレイン領域の間に延びていることを特徴とするメモリセル。複数のメモリセルを備えるメモリアレイ、およびメモリセルを製作するプロセス。

(もっと読む)

半導体装置およびその製造方法

【課題】素子面積が小さくしかも素子の耐圧の高い半導体装置およびその製造方法を提供する。

【解決手段】基板11と、基板上に設けられた一導電型の第1の半導体層13と、第1の半導体層上に設けられた一導電型で低不純物濃度の第2の半導体層15と、アイソレーション領域50によって分離された素子領域71内に形成されたMOSトランジスタ75と、素子領域内に一主面から第1の半導体層に達して設けられた一導電型で高不純物濃度の領域17と、領域17とMOSトランジスタのドレイン領域35との間に設けられた絶縁領域60であって、一主面10から第1の半導体層13に達し、基板11に達していない絶縁領域60とを備える。

(もっと読む)

1 - 20 / 139

[ Back to top ]