Fターム[5F140CB04]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | 素子分離構造 (5,334) | 溝掘り構造 (2,469)

Fターム[5F140CB04]に分類される特許

1 - 20 / 2,469

化合物半導体装置及びその製造方法

半導体装置及び半導体装置の製造方法

半導体装置の製造方法

半導体装置の製造方法

化合物半導体装置及びその製造方法

半導体装置およびその製造方法

半導体装置

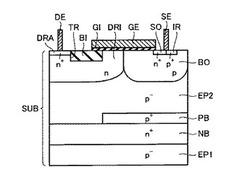

【課題】ハイサイド素子として用いても誤動作が少なく、かつオン耐圧およびオフ耐圧の双方を高く維持することのできる半導体装置を提供する。

【解決手段】主表面を有する半導体基板SUBの内部には、p-エピタキシャル領域EP1が、その主表面側にはp-エピタキシャル領域EP2が、その主表面側にはn型ドリフト領域DRIとp型ボディ領域BOとが形成されている。p-エピタキシャル領域EP1とp-エピタキシャル領域EP2との間には、これらの領域を電気的に分離するためにn+埋め込み領域NBが形成されている。n+埋め込み領域NBとp-エピタキシャル領域EP2との間には、p-エピタキシャル領域EP2よりも高いp型不純物濃度を有するp+埋め込み領域PBが形成されている。p+埋め込み領域PBは、n型ドリフト領域DRIとp型ボディ領域BOとの接合部の少なくとも直下に位置し、かつn型ドリフト領域DRIと接するドレイン領域DRAの直下を避けて配置されている。

(もっと読む)

半導体装置とその製造方法

【課題】ゲート高さが低いため製造容易で、ゲート−コンタクト間の容量を抑制し、ゲート−コンタクト間の短絡を抑制した半導体装置を提供する。

【解決手段】半導体装置の製造方法は基板上にFin型半導体層を形成する。Fin型半導体層に交差するダミーゲートが形成される。Fin型半導体層にソースおよびドレインが形成される。ダミーゲート上に層間絶縁膜を堆積した後、ダミーゲートの上面を露出させる。ダミーゲートを除去してゲートトレンチを形成する。ゲートトレンチ内のFin型半導体層の上部をリセスする。ゲートトレンチ内のFin型半導体層の表面にゲート絶縁膜を形成する。ゲート電極をゲートトレンチ内に充填する。ゲート電極をエッチングバックすることによってゲート電極を形成する。ゲート電極の上面の高さはソースおよびドレインにおけるFin型半導体層の上面の高さ以下かつゲートトレンチ内のFin型半導体層の上面の高さ以上である。

(もっと読む)

半導体装置およびその製造方法

【課題】トンネルFETのオン電流の劣化を抑制しつつ、オフ電流を低減することが可能な半導体装置を提供する。

【解決手段】実施形態によれば、半導体装置は、溝が形成された基板と、前記基板上の前記溝に隣接する位置にゲート絶縁膜を介して形成され、前記溝の反対側に位置する第1側面と、前記溝側に位置する第2側面とを有するゲート電極とを備える。さらに、前記装置は、前記ゲート電極の前記第1側面に形成された第1の側壁絶縁膜と、前記ゲート電極の前記第2側面と前記溝の側面に形成された第2の側壁絶縁膜とを備える。さらに、前記装置は、前記基板内において、前記ゲート電極の前記第1側面に対し前記第1の側壁絶縁膜側に形成された、第1導電型のソース領域と、前記基板内において、前記ゲート電極の前記第2側面と前記溝の側面に対し前記第2の側壁絶縁膜側に形成された、第2導電型のドレイン領域とを備える。

(もっと読む)

化合物半導体装置の製造方法、基板評価装置及び基板評価方法

【課題】化合物半導体層を形成する前の基板の状態で非接触のスクリーニングを行うことで、事前に化合物半導体層の不良発生を認識してこれを防止することができ、歩留まりの向上及び製造コストの削減を可能とする信頼性の高い化合物半導体装置を得る。

【解決手段】偏光レーザ12によりSiC基板1の基板面に偏光レーザ光を照射し、検出部13によりSiC基板1からの発光を検出し、表示部14によりSiC基板1の発光強度の面内分布を得て、SiC基板1の窒素混入量を評価した後、SiC基板1の上方に化合物半導体積層構造2を形成する。

(もっと読む)

半導体装置の製造方法

【課題】微細化に対応した半導体装置を提供する。

【解決手段】半導体基板の第1の領域内に第1の方向に沿って交互に配置されるように第1及び第2の素子分離領域を形成する。この際、第1及び第2の素子分離領域のうち少なくとも一方の素子分離領域の側面は半導体基板の主面に対して垂直とならないように第1及び第2の素子分離領域を形成する。この後、第1及び第2の素子分離領域の上部を除去して、第1の素子分離領域と第2の素子分離領域の間の半導体基板をフィンとして形成する。

(もっと読む)

半導体装置の製造方法

【課題】電界効果トランジスタを有する半導体装置のトランジスタ性能を向上させることのできる技術を提供する。

【解決手段】ゲート絶縁膜5およびゲート電極6n,6pの側面にサイドウォール9を形成した後、サイドウォール9の両側の半導体基板1に不純物をイオン注入して不純物領域を形成する。続いて、半導体基板1の主面上に第1絶縁膜14、第2絶縁膜15、および第3絶縁膜16を順次形成した後、イオン注入された上記不純物を活性化する熱処理を行う。ここで、第1絶縁膜14は、第2絶縁膜15よりも被覆性のよい膜であり、かつ、第2絶縁膜15とエッチング選択比が異なる膜である。第2絶縁膜15は、第1絶縁膜14よりも水素の拡散を阻止する機能が高い膜である。第3絶縁膜16は、第1絶縁膜14および第2絶縁膜15よりも内部応力の変化が大きい膜である。

(もっと読む)

半導体装置とその製造方法

【課題】製造プロセスが容易であり、かつ、Fin型FETおよび従来型トランジスタを混載した半導体記憶装置を提供することである。

【解決手段】半導体記憶装置は第1の領域および第2の領域を備える。メモリ部のトランジスタは第1導電型のFin型半導体層を備える。第1導電型の第1のソース層および第1のドレイン層はFin型半導体層の両端に設けられる。第1のゲート電極はFin型半導体層の両側面に設けられる。第2導電型のパンチスルーストッパ層は第1のゲート電極およびFin型半導体層の下に設けられている。パンチスルーストッパ層の不純物濃度は第1のソース層および第1のドレイン層の下の不純物濃度よりも高い。周辺回路部のトランジスタは、第2のゲートトレンチを備える。第1導電型の第2のソース層および第1導電型の第2のドレイン層は、第2のゲートトレンチの両側に設けられる。第2のゲート電極は、第2のゲートトレンチ内に充填される。

(もっと読む)

半導体装置およびその製造方法

【課題】トンネルトランジスタのトンネルオフリーク電流を低減することが可能な半導体装置を提供する。

【解決手段】実施形態によれば、半導体装置は、基板と、前記基板上にゲート絶縁膜を介して形成されたゲート電極とを備える。さらに、前記装置は、前記基板内に前記ゲート電極を挟むように形成された第1導電型のソース領域、および前記第1導電型とは逆導電型の第2導電型のドレイン領域を備える。さらに、前記ゲート電極は、前記ゲート電極内の前記ソース領域側に形成された前記第1導電型の第1領域と、前記ゲート電極内の前記ドレイン領域側に形成され、前記第1領域に比べて、前記第1導電型の不純物濃度から前記第2導電型の不純物濃度を引いた値が低い第2領域とを有する。

(もっと読む)

半導体装置とその製造方法

【課題】製造プロセスが容易であり、かつ、電流駆動能力の高い半導体基板およびその製造方法を提供することである。

【解決手段】本実施形態による半導体装置は、半導体基板を備える。第1導電型のFin型半導体層は、半導体基板上に形成されている。第1導電型のソース層および第1導電型のドレイン層は、Fin型半導体層の長手方向の両端に設けられている。ゲート絶縁膜は、Fin型半導体層の両側面に設けられている。ゲート電極は、Fin型半導体層の両側面にゲート絶縁膜を介して設けられている。第2導電型のパンチスルーストッパ層は、ゲート電極およびFin型半導体層の下に設けられている。パンチスルーストッパ層の不純物濃度は、ソース層およびドレイン層の下にある半導体基板の不純物濃度よりも高い。

(もっと読む)

半導体装置およびその製造方法

【課題】ゲート電極の断線による縦型トランジスタの故障を改善すること。

【解決手段】半導体装置は、第1の方向(Y)に互いに隙間を空けて形成された複数の半導体ピラー(5A1〜5A5)から成る半導体ピラー群(5)を含む。半導体ピラー群(5)の内、両端部を除く中間部に位置する半導体ピラー(5A2〜5A4)のいずれか1つである特定の半導体ピラー(5A3)と隣接して、ダミーピラー(6)が第1の方向(Y)と直交する第2の方向(X)に設けられている。ゲート絶縁膜(10)が、複数の半導体ピラー(5A1〜5A5)の各々の外周面とダミーピラー(6)の外周面の一部とに形成されている。ゲート絶縁膜(10)を介して、複数の半導体ピラー(5A1〜5A5)の間の隙間と特定の半導体ピラー(5A3)とダミーピラー(6)との間の隙間とを埋めるように、ゲート電極(11)が、複数の半導体ピラーの側面とダミーピラーの側面とに形成されている。

(もっと読む)

ポリメタルゲート電極を持つ半導体素子の製造方法

【課題】TiN膜及びバッファ層から形成されるバリアー膜を備えるポリメタルゲート電極を持つ半導体素子及びその製造方法を提供する。

【解決手段】半導体基板上に形成されたゲート絶縁膜と、ゲート絶縁膜上に半導体基板側から順に積層された導電性ポリシリコン膜、第1金属シリサイド膜、バリアー膜、及び金属膜から形成されるポリメタルゲート電極と、を備える半導体素子である。バリアー膜は、第1金属シリサイド膜上に形成されるTiN膜と、TiN膜と金属膜との間に介在されるバッファ層と、を備える。

(もっと読む)

半導体装置

【課題】複数のチャネルを有する窒化物半導体装置において、ノーマリオフかつ低オン抵抗を実現する技術を提供する。

【解決手段】第1の窒化物半導体層3,5,7と、第1の窒化物半導体層よりも禁制帯幅が大きい第2の窒化物半導体層5,6,8とが積層されたヘテロ接合体を少なくとも2つ以上有する窒化物半導体積層体10を備え、窒化物半導体積層体10に設けられたドレイン電極14と、ソース電極13と、ドレイン電極14とソース電極13の両者に対向して設けられたゲート電極15,16とを有し、ドレイン電極14とソース電極13は、窒化物半導体積層体10の表面または側面に配置され、ゲート電極15,16は、窒化物半導体積層体10の深さ方向に設けられた第1ゲート電極15と、該第1ゲート電極15と窒化物半導体積層体10の深さ方向の配置深さが異なる第2ゲート電極16とを有する。

(もっと読む)

半導体装置およびその製造方法

【課題】窒化ガリウム(GaN)系のHEMTを保護するダイオード構造を備えた半導体装置とその製造方法を提供する。

【解決手段】基板10のうちGaN層13に2次元電子ガスが生成される領域が活性層領域40とされ、基板10のうち活性層領域40を除いた領域にイオン注入が施されていることにより活性層領域40とは電気的に分離された領域が素子分離領域50とされている。そして、ダイオード60は素子分離領域50の層間絶縁膜20の上に配置されている。このように、基板10のうちHEMTが動作する活性層領域40とは異なる素子分離領域50を設けているので、1つの基板10にGaN−HEMTとダイオード60の両方を備えた構造とすることができる。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】電界が局所的に集中することを抑制して、高耐圧化した半導体装置を提供する。

【解決手段】ソース領域110は、溝部300側面の第2面32に面し、一部が面31と面32の交線と平行な方向に延在する。ドリフト領域140は、溝部300のうち面32と反対の面33に面し、一部が面31および面33の交線と平行な方向に延在して設けられ、ソース領域110よりも低濃度に形成される。ドレイン領域120は、ドリフト領域140を介し溝部300の反対側に位置し、ドリフト領域140と接するように設けられ、ドリフト領域140よりも高濃度に形成される。第1ゲート絶縁層200は、溝部300の側面のうち面32と面33に交わる方向の面である面34と接するとともに、面31上のうち少なくともチャネル領域130と接する。ゲート電極400は、第1ゲート絶縁層200上に設けられ。溝部300はドリフト領域140よりも深い。

(もっと読む)

1 - 20 / 2,469

[ Back to top ]