Fターム[5F140CC00]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | 層間膜、保護膜 (4,863)

Fターム[5F140CC00]の下位に属するFターム

Fターム[5F140CC00]に分類される特許

1 - 20 / 33

MOSトランジスタおよび半導体集積回路装置の製造方法

【課題】埋込絶縁膜によりゲート絶縁膜の実効的膜厚がドレイン端近傍において増大される構成の高電圧MOSトランジスタにおいて、耐圧特性を劣化させずにオン抵抗を低減させる。

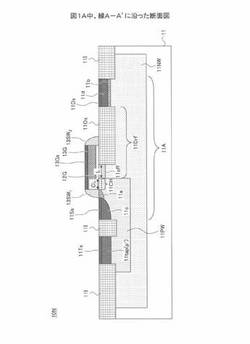

【解決手段】第1導電型の第1のウェル11NW第2導電型の第2のウェル11PWとが形成された半導体基板11と、チャネル領域11CHと、ソースエクステンション領域11aと、第1のウェル11NW中に形成された埋込絶縁膜11Oxと、第2のウェル11PWと埋込絶縁膜11Oxの間に形成されたオフセット領域11offと、埋込絶縁膜11Oxに対してオフセット領域11offとは反対の側に形成された、第1導電型を有するドレインエクステンション領域11bと、チャネル領域11CHとオフセット領域11offおよび埋込絶縁膜11Oxを覆って、ゲート絶縁膜12Gとn+型のポリシリコンゲート電極13Gよりなるゲート電極構造と、を備える。

(もっと読む)

半導体装置およびその製造方法

【課題】チャネル形成時のひずみ緩和の抑制を可能にすると共に、更にひずみを印加することを可能にする。

【解決手段】基板1と、基板上に形成されひずみを有する第1半導体層3と、第1半導体層3上に離間して設けられ、第1半導体層3と格子定数が異なる第2および第3半導体層8と、第2半導体層と第3半導体層8との間の第1半導体層3上に設けられたゲート絶縁膜4と、ゲート絶縁膜4上に設けられたゲート電極5と、を備え、第2半導体層および第3半導体層8直下の第1半導体層3の外表面領域をシリサイド3a、8aとする。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】縦型トランジスタの特性を悪化させることなく縦型トランジスタの設置面積を削減できる高集積化に適した半導体装置およびその製造方法を提供する。

【解決手段】一定の間隔を空けて配置された複数のピラー30が備えられ、複数のピラー30が、縦型トランジスタTのチャネルとして機能する半導体層からなるチャネルピラー1と、不純物拡散層からなり、前記チャネルピラー1の下部に接続されて縦型トランジスタTの一方のソースドレインとして機能する下部拡散層4に電気的に接続された引き上げコンタクトプラグ2とを含む半導体装置とする。

(もっと読む)

半導体装置およびその製造方法

【課題】特性を劣化させることなく、微細化することができる半導体装置およびその製造方法を提供する。

【解決手段】半導体装置は、主表面を有する半導体基板SBと、主表面に互いに間隔をおいて形成されたソース領域SRおよびドレイン領域DRと、ソース領域SRとドレイン領域DRとに挟まれる主表面上に形成されたゲート電極層GEと、ソース領域SRの表面に接するように形成された第1導電層PL1と、ドレイン領域DRの表面に接するように形成された第2導電層PL2とを備え、第1導電層PL1とソース領域SRとの接触領域CR1からゲート電極層GEの下側を通って第2導電層PL2とドレイン領域DRとの接触領域CR2まで延びるように溝REが主表面に形成されている。

(もっと読む)

半導体製造装置

【課題】内部応力を有する膜を基板の裏面にのみ形成することにより、基板の反り量を抑制し、その際に基板の表面にダメージを与えず、裏面に対する成膜と表面に対するパターン形成とを一貫して行う半導体製造装置を得られるようにする。

【解決手段】基板に薬液を塗布する薬液塗布部102と、基板を加熱する加熱処理部104と、基板の表面にレジストを塗布するレジスト塗布部107と、そのレジストに所定のパターンを露光する露光部105と、そのレジストを現像することにより所定のパターンを得る現像部108とを備えている。薬液塗布部102は、基板を浮遊した状態で、基板を回転させながら基板の裏面にのみ薬液を塗布する薬液塗布手段を有し、加熱処理部104は、基板に熱処理を行うことにより、内部応力を有する応力印加膜を成膜する熱処理手段を有し、裏面に応力印加膜の成膜を行うことと、表面に所定のパターンを形成する処理とを一貫して行う。

(もっと読む)

半導体装置及びその製造方法

【課題】前記従来のエアーギャップを有するMISトランジスタ及びその製造方法では、ゲート電極の周囲にエアーギャップを設けるため、ゲート電極に近接して応力絶縁膜を形成することができない。

【解決手段】半導体装置は、ゲート絶縁膜13と、ゲート電極14と、ソースドレイン領域19と、コンタクトプラグ22と、応力絶縁膜23とを備えている。ゲート電極14の側方のうちゲート電極14とコンタクトプラグ22との間に位置する領域のみに空洞24が形成されており、応力絶縁膜23は半導体基板10上にゲート電極14を覆うように形成されており、半導体基板10におけるゲート電極14の直下に位置するチャネル領域に対して応力を生じさせる。

(もっと読む)

半導体装置及びその製造方法

【課題】ゲート電極中のシリコン混晶層の形成を制御することにより、キャップ膜の形成を不要とし、シリサイド層を精度良く形成する。

【解決手段】第1導電型の半導体領域10x上に形成されたゲート絶縁膜13と、ゲート絶縁膜13上に形成され、第2導電型のポリシリコン膜28Aとポリシリコン膜28A上に形成された炭素を含む第1のシリコン混晶層25とを有するゲート電極25Aと、第1のシリコン混晶層25上に形成された第1のシリサイド層29と、半導体領域10xにおけるゲート電極25Aの側方下の領域に形成された第2導電型の不純物拡散領域24と、不純物拡散領域24の上部領域に形成された炭素を含む第2のシリコン混晶層26と、第2のシリコン混晶層26上に形成された第2のシリサイド層30とを備えている。

(もっと読む)

半導体装置の製造方法

【課題】MOSFETのゲート絶縁膜が薄膜化しゲート構造が複雑化した場合においても、動作速度に優れ、高信頼性を安定して確保できるMOSFETを実現する。

【解決手段】半導体装置の製造方法は、半導体基板3に、nチャネル型電界効果トランジスタ及びpチャネル型電界効果トランジスタを形成する工程(a)と、nチャネル型電界効果トランジスタ上及びpチャネル型電界効果トランジスタ上を覆うように応力膜11を形成する工程(b)と、応力膜11上に、pチャネル型電界効果トランジスタの上方を覆い且つnチャネル型電界効果トランジスタの上方に開口を有する遮光膜12を形成する工程(c)と、工程(c)の後に、半導体基板3上の全面に紫外線を照射する工程(d)とを備える。

(もっと読む)

半導体装置の製造方法

【課題】MISトランジスタを備える半導体装置の性能を向上させる。

【解決手段】シリコン基板1の主面s1上のうち、nMIS領域RnにnMIS用ゲート電極GEnを形成し、pMIS領域RpにpMIS用ゲート電極GEpを形成し、それらの側方下部に、それぞれ、n型ソース・ドレイン領域sdnおよびp型ソース・ドレイン領域sdpを形成する。続いて、シリコン基板1の主面s1と両ゲート電極GEn,GEpとを覆うようにして、引張応力を持つ第1応力膜N1aを形成する。その後、pMIS領域Rpの第1応力膜N1aにイオン注入300を施すことで応力を緩和させる。その後、熱処理を施すことで両ゲート電極GEn,GEpを結晶化してから、第1応力膜N1aを除去する。両ゲート電極GEn,GEpを結晶化する工程では、第1応力膜N1aの引張応力をnMIS用ゲート電極GEnに記憶させる。

(もっと読む)

半導体装置の製造方法、半導体装置

【課題】半導体装置に適用される比較的膜厚の厚い絶縁膜中の水素濃度を大幅に低減する。

【解決手段】半導体装置70には、半導体基板1上に複数のメモリセルトランジスタが設けられる。n型拡散層7、シャロートレンチアイソレーション(STI)2、及び絶縁膜6上と、側壁絶縁膜8の側面とには積層シリコン窒化膜9が形成される。メモリセルトランジスタのゲートの周囲に積層シリコン窒化膜9が設けられる。積層シリコン窒化膜9は、例えば膜厚が略100nmであり、n層のシリコン窒化膜から構成される。n層のシリコン窒化膜の膜厚は、それぞれ3nm以下に設定される。n層のシリコン窒化膜は、それぞれ膜中の水素結合がプラズマ処理で置換され、水素が離脱され、膜中の水素濃度が大幅に低減されたシリコン窒化膜である。

(もっと読む)

半導体装置及びその製造方法

【課題】低い閾値電圧のnチャネル型MISトランジスタを含む半導体装置を実現する。

【解決手段】半導体装置は、半導体基板と、半導体基板の主面に形成されたn型半導体領域とp型半導体領域と、半導体基板上に形成され、n型半導体領域とp型半導体領域を露出するように形成された第1と第2のトレンチを有する第1の絶縁層と、第1と第2のトレンチの側壁と底部に沿って形成されたゲート絶縁膜と、第1のトレンチの側壁と底部に沿って形成されゲート絶縁膜を介して内張りされた第1の金属層と、第2のトレンチの側壁と底部に沿って形成されゲート絶縁膜を介して1モノレイヤー以上で1.5nm以下の厚さに内張りされた第2の金属層と、第2の金属層上に内張りされたアルカリ土類金属元素、III族金属元素の単体、窒化物、炭化物、酸化物の内の少なくとも1つの金属元素を含む第3の金属層と、第1と第2のソース/ドレイン領域を具備することを特徴とする。

(もっと読む)

半導体装置

【課題】層間絶縁膜を厚くしなくてもソース配線の外にドレイン配線を引き出せ、かつ、LOCOS酸化膜や層間絶縁膜などの絶縁膜の絶縁破壊を防止できるようにする。

【解決手段】素子部8から配線引出し部9に延設されるようにn-型ドリフト層4の裏面に裏面電極19を備え、この裏面電極19とソース配線18との間に電流が流れるような構造、つまりn-型ドリフト層4の表裏を貫通して縦方向に電流を流す構造にする。そして、裏面電極19を配線引出し部9まで延設し、n+型コンタクト領域21、配線引出し部9のn-型ドリフト層4、nウェル領域20およびn+型コンタクト領域21を通じてドレイン配線23と接続する。すなわち、裏面電極19を通じて電流が流れるようにすることにより、ドレイン配線23を素子部8の外に引き出した構造とする。

(もっと読む)

半導体装置及びその製造方法

【課題】所望の厚さで制御良くエピタキシャル成長され、良好な特性を示すシリコン混晶層を備えた半導体装置及びその製造方法を提供する。

【解決手段】半導体装置は、半導体基板10内に形成された素子分離領域11aと、素子分離領域11aに囲まれた半導体基板10からなり、トレンチ部を有する活性領域と、活性領域上に形成されたゲート電極13、ゲート電極13の側面上であって、平面的に見てゲート電極13とトレンチ部との間に形成された第1のサイドウォール19、及びトレンチ部内に充填された第1導電型のシリコン混晶層21を有する第1導電型のMISトランジスタと、トレンチ部と素子分離領域11a、11bとの間に設けられ、半導体基板10からなる基板領域と、基板領域に形成された第1導電型の不純物領域22とを備えている。シリコン混晶層21は、活性領域のチャネル領域に対して応力を生じさせる。

(もっと読む)

シリコン含有膜を選択的に堆積する方法

1つの実施形態は、単結晶膜を選択的に堆積するための方法を提供する。この方法は、第1の表面形態を有する第1の表面およびこの第1の表面形態とは異なる第2の表面形態を有する第2の表面を含む基体を準備する工程を含む。シリコン前駆体[108]およびBCl3[134]は相互混合され、これにより供給ガスが形成される。この供給ガスは、化学気相成長条件[122]下でこの基体へ導入される。Si含有層は、供給ガス[120]を導入することにより、第2の表面上に堆積することなく、第1の表面上に選択的に堆積される。 (もっと読む)

半導体装置及びその製造方法

【課題】 製造工程で発生したダストによるコンタクト不良の発生を抑制する。

【解決手段】 半導体基板10上に形成されたゲート電極12と、基板内に形成されたソース、ドレイン拡散層13と、ソース、ドレイン拡散層上に形成され、断面形状が略三角形状のエピタキシャルシリコン層14と、全面上に形成された層間絶縁膜15と、層間絶縁膜に開口されたコンタクトホール18内に形成され、ゲート電極12と電気的に接続されたコンタクト層16と、層間絶縁膜に開口されたコンタクトホール18内に形成され、エピタキシャルシリコン層14層と電気的に接続されたコンタクト層17を具備する。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】構造を工夫することにより、ストレスライナー膜がチャネルに印加する応力を高め、電流駆動力が向上した半導体装置を得ることを目的とする。

【解決手段】本発明の半導体装置では、半導体基板1と、この半導体基板1に形成された素子分離絶縁膜2と、半導体基板1上から素子分離絶縁膜2上にかけて形成されたゲート電極4とを備えている。素子分離絶縁膜2は、ゲート電極4下以外の該素子分離絶縁膜2の上部を掘り下げることによって上段部と下段部の段差構造を有している。この半導体装置1は、ゲート電極4の両側の半導体基板1に形成されたソースあるいはドレインとなる半導体領域と、半導体領域、素子分離絶縁膜2の下段部、およびゲート電極4を覆って形成されたストレスライナー膜3とをさらに備えている。

(もっと読む)

半導体装置およびその製造方法

【課題】P型FETとN型FETとを半導体基板に形成された半導体装置において、ゲート電極をフルシリサイド化して、P型FETの移動度を高め、N型FETのオン電流を増やすことを可能とする。

【解決手段】半導体基板11にN型FETとP型FETとが形成され、前記N型FETのゲート電極14NとP型FETのゲート電極14Pとがフルシリサイド化されている半導体装置1において、前記P型FETのゲート電極14Pは、ゲート長方向の断面形状が前記半導体基板11表面より上方に行くに従いゲート長が短くなる形状に形成されていて、前記N型FETのゲート電極14Nは、ゲート長方向の断面形状が前記半導体基板11表面より上方に行くに従いゲート長が長くなる形状に形成されていることを特徴とする。

(もっと読む)

半導体素子およびその製造方法

【課題】MOSトランジスタに十分な応力(ストレス)が加える半導体素子およびその製造方法を提供する。

【解決手段】半導体素子は、半導体基板100と、半導体基板100上に備えられたゲート電極114およびゲート電極114の側壁面に備えられたスペーサ116を含むゲート構造物110と、ゲート構造物110の両側の半導体基板100内に形成されたソース/ドレーン領域102と、ゲート構造物110上エッチング停止膜130と、を含み、エッチング停止膜130は、スペーサ116上の第1領域130_1およびゲート電極の上面上の第2領域130_2を含み、第1領域130_1の厚さは、第2領域130_2の厚さの85%以下である。

(もっと読む)

半導体装置及びその製造方法

【課題】ゲート絶縁膜に用いられるLa−Hf−O膜系は、成膜時にシリコン基板との間に低誘電率層が出現し、これ排除する公知な技術による半導体装置及びその製造方法は提案されていなかった。

【解決手段】本発明に従う実施形態は、非晶質状態でSiが添加されたLa−Hf−O膜をゲート絶縁膜として用いる半導体装置及びその製造方法である。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】用途に応じてゲート幅を設計変更することが可能なフィン型FETを含む半導体装置及びその製造方法を実現する。

【解決手段】半導体基板11上面に、第1高さを有するフィン12aと、第1高さよりも低い第2高さを有するフィン12bとを形成する工程と、フィン12a及び12bそれぞれの上面及び側面にシリコン酸化膜を形成する工程と、シリコン酸化膜上に導電性を有するポリシリコン膜を形成する工程と、シリコン酸化膜及びポリシリコン膜をパターニングすることで、フィン12a及び12bそれぞれの上面から側面にかけてゲート絶縁膜15及びゲート電極16を形成する工程と、フィン12a及び12bそれぞれにおけるゲート電極16下を挟む2つの領域に一対の拡散領域14を形成する工程とを備えた。

(もっと読む)

1 - 20 / 33

[ Back to top ]