Fターム[5F140CD08]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | その他の領域、その他の素子構造及び製造 (630) | フィールドプレート(内部電界の緩和以外) (252)

Fターム[5F140CD08]の下位に属するFターム

内部電界の緩和 (186)

Fターム[5F140CD08]に分類される特許

1 - 20 / 66

半導体装置及びその製造方法

【課題】柱状半導体層の幅を広く維持することができる半導体装置を提供すること。

【解決手段】半導体装置は、一つの直線上に順に形成された、第1、第2及び第3の柱状半導体層と、第2及び第3の柱状半導体層の間の空間であって第2及び第3の柱状半導体層の側面に夫々設けられた第1及び第2のゲート電極と、第1及び第2の柱状半導体層の間の空間及び第2及び第3の柱状半導体層の空間に埋め込まれた層間絶縁膜とを有する。層間絶縁膜は、第1及び第2の柱状半導体層の間の空間内であってゲート電極を介することなく第1及び第2の柱状半導体層の側面に形成され、第2及び第3の柱状半導体層の間の空間内であって第1及び第2のゲート電極を介して第2及び第3の柱状半導体層の側面に形成されている。

(もっと読む)

窒化物系半導体装置

【課題】ダイオード部とトランジスタ部の面積比率を自由に設定することが可能な窒化物系半導体装置を提供することを目的とする。

【解決手段】第1HEMT部30及び第2HEMT部31から成るトランジスタ部1と、第1電極24と電気的に短絡された第1ショットキー電極28及び第1ゲート電極26と電気的に第2ショットキー電極29から成るダイオード部2と、を備えて構成されている。また、第1電極24と第2電極25との間の領域に第1電極24に沿って、第1ゲート電極26及び第1ショットキー電極28が交互に形成され、かつ、第2電極25に沿って、第2ゲート電極27及び第2ショットキー電極29が交互に形成されている。さらに、第1ゲート電極26と第2ゲート電極27とは、対向して形成されており、第1ショットキー電極28と第2ショットキー電極29とは対向して形成されている。

(もっと読む)

横型半導体装置

【課題】抵抗性フィールドプレート部のレイアウトの自由度を高める技術を提供すること。

【解決手段】コーナー範囲に設けられている中間抵抗性フィールドプレート部34は、カソード領域28とアノード領域23の間で往復を繰返して形成されている。直線範囲に設けられている中間抵抗性フィールドプレート部34も、カソード領域28とアノード領域23の間で往復を繰返して形成されている。コーナ範囲に設けられている中間抵抗性フィールドプレート部34と直線範囲に設けられている中間抵抗性フィールドプレート部34は接していない。

(もっと読む)

半導体装置

【課題】オン抵抗が低く、かつ、Vthが高い半導体装置を提供する。

【解決手段】基板102の上方に、III−V族化合物半導体で形成されたバックバリア層106と、バックバリア層106上に、バックバリア層106よりバンドギャップエネルギーが小さいIII−V族化合物半導体で形成され、バックバリア層106の上方の少なくとも一部に設けられたリセス部122において、他の部分より膜厚が薄いチャネル層108と、チャネル層108にオーミック接合された第1の電極116,118と、少なくともリセス部においてチャネル層の上方に形成された第2の電極120と、を備える半導体装置を提供する。

(もっと読む)

窒化物半導体素子及びその製造方法

【課題】FETのソース領域にショットキー電極を形成し、ゲート電極をソース電極の一部領域と窒化物半導体領域の一部に形成し、ドレイン電極と該ソース電極との間にフローティングガードリングを設けることによって、ノーマリ−オフで動作する半導体素子を提供する。

【解決手段】内部に2次元電子ガス(2DEG)チャネルを形成する窒化物半導体層30と、窒化物半導体層30にオーミック接合されたドレイン電極50と、ショットキー接合されたソース電極60と、ドレイン電極50とソース電極60との間で窒化物半導体層30にショットキー接合されたフローティングガードリング75と、ドレイン電極50とソース電極60との間及びソース電極60の少なくとも一部上にかけて形成された誘電層40と、誘電層40上に形成され、一部が、誘電層40を挟んでソース電極60のドレイン方向のエッジ部分上に形成されたゲート電極70とを含む。

(もっと読む)

半導体装置

【課題】オン抵抗が低く、かつ、耐圧が高いノーマリーオフの半導体装置を提供する。

【解決手段】基板102の上方に形成された、III−V族化合物半導体からなるバックバリア層106と、バックバリア層106上に形成され、バックバリア層よりバンドギャップエネルギーが小さいIII−V族化合物半導体からなるチャネル層と108、チャネル層108にオーミック接続された第1の電極116,118と、チャネル層の上方に形成された第2の電極120と、を備え、バックバリア層106は第2の電極120の下方に設けられ、かつ、第2の電極120の下方から第1の電極の116,118下方まで連続して設けられていない半導体装置を提供する。

(もっと読む)

半導体装置の製造方法

【課題】トレンチ横型パワーMOSFETにおいて、装置の信頼性を高めること。

【解決手段】半導体基板1の表面層にトレンチ5を形成する。トレンチ5は、半導体基板1の表面層を第1メサ領域41と第2メサ領域42に分割し、かつ第1メサ領域41と第2メサ領域42を交互に配置させる。第1メサ領域41および第2メサ領域42は、それぞれソース電流およびドレイン電流の引き出しをおこなう。第2メサ領域42は、半導体基板1からの深さが、第1メサ領域41よりも深くなっている。

(もっと読む)

半導体素子およびその駆動方法

【課題】双方向で電流の流れを制御(ON/OFF制御)することができる半導体素子を提供すること。

【解決手段】チャネル層8と障壁層10が積層された半導体へテロ接合と、前記半導体へテロ接合の上方に設けられたゲート12と、前記ゲートの両側に設けられた第1および第2のソースドレイン端子14a,14bと、前記第1のソースドレイン端子と前記ゲートの間に設けられた第1のフィールプレート16aと、前記第2のソースドレイン端子と前記ゲートの間に設けられた第2のフィールドプレート16bとを有すること。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】ゲート電極の電界集中を緩和して耐圧の更なる向上を実現することに加え、デバイス動作速度を向上させ、アバランシェ耐量が大きく、サージに対して強く、例えばインバータ回路等に適用する場合に外部のダイオードを接続することを要せず、ホールが発生しても安定動作を得ることができる信頼性の高い高耐圧の化合物半導体装置を実現する。

【解決手段】化合物半導体積層構造2に形成された電極用リセス2Cを、ゲート絶縁膜6を介して電極材料で埋め込むようにゲート電極7を形成すると共に、化合物半導体積層構造2に形成されたフィールドプレート用リセス2Dをp型半導体で埋め込み、化合物半導体積層構造2とp型半導体層8aで接触するフィールドプレート8を形成する。

(もっと読む)

トランジスタの制御回路、トランジスタの制御システム、およびトランジスタの制御方法

【課題】ゲートとフィールドプレートとを有するトランジスタのスイッチング速度を速くする。

【解決手段】ゲートとフィールドプレートとを有するトランジスタ4を制御する制御回路2であって、トランジスタを駆動するタイミングを検出する検出回路38と、駆動するタイミングに応答してゲートを駆動する第1の駆動タイミングとフィールドプレートを駆動する第2の駆動タイミングとを制御するタイミング制御回路40と、第1の駆動タイミングに応答してゲートを駆動し第2の駆動タイミングに応答してフィールドプレートを駆動する駆動回路42とを有する。

(もっと読む)

半導体装置

【課題】オン抵抗の低減を実現できる、高耐圧のLDMOSトランジスタを有する半導体装置を提供する。

【解決手段】半導体基板上に配置された第2導電型の第1半導体領域と、第1半導体領域の上面の一部に埋め込まれた第1導電型の第2半導体領域と、第2半導体領域の上面の一部に埋め込まれた第2導電型のソース領域と、第2半導体領域と離間して第1半導体領域の上面の一部に埋め込まれた第2の導電型のドレイン領域と、ソース領域とドレイン領域間で第2半導体領域上に配置されたゲート電極と、第2半導体領域とドレイン領域間で第1半導体領域上に配置された絶縁膜と、絶縁膜上に配置されてゲート電極とドレイン領域間の電圧を分圧する分圧素子と、分圧素子とドレイン領域との間に接続された電荷移動制限素子とを備える。

(もっと読む)

半導体装置及びその製造方法

【課題】特性バラツキを低減することができるような半導体装置及びその製造方法を提供する。

【解決手段】本発明の実施形態にかかる半導体装置は、ゲート絶縁膜を介して基板の表面を第1導電型チャネル領域から酸化膜の一部までを覆い、且つ、第1導電型チャネル領域と酸化膜との間に開口部を有するゲート電極と、この開口部下の基板に形成された第2導電型ドリフト領域の第2の部分とを有する。

(もっと読む)

半導体製造方法および半導体装置

【課題】ウェーハテスト後のウェーハ状態において所望の回路を印刷処理により容易に形成することが可能な半導体製造方法および半導体装置を提供することを課題する。

【解決手段】本発明に係る半導体製造方法は、ウェーハの被描画パターン形成領域に所定の深さを有する溝部を形成する工程、ウェーハに対してトリミング要否の検査を行う工程、前記ウェーハにおけるトリミング必要なウェーハの前記溝部に導電性溶剤を射出し描画パターンを描画する工程、描画パターンを描画した後、脱気および低温アニールする工程、脱気および低温アニールした成膜後、当該成膜表面を平坦化する工程、および平坦化した後、高温アニールする工程、を有する。

(もっと読む)

半導体装置及びその製造方法

【課題】3次元構造のパワーMOSトランジスタやIBGTの破壊耐量を改善する。

【解決手段】一つの実施形態の半導体装置には、N+基板1に溝21が設けられ、溝21に積層形成されるN層2、N−層3、P層4、及びN+層5が溝21を覆うように設けられる。N+層5に、N+基板1に対して垂直方向では一部がN+層5を貫通してP層4表面が露呈され、N+基板1に対して水平方向では一部がN+層5を貫通してP層4側面が露呈するように溝22が設けられ、溝22にP+層6が溝22を覆うように設けられる。N+基板1に対して垂直方向では、N+層5を貫通してP層4表面が露呈され、N+基板1に対して水平方向では、P層4を貫通して一端でN−層3側面が露呈し、他端でN+層5側面が露呈し、P+層6の間及び側面と離間して配置形成される溝23が設けられる。溝23に、トレンチゲート11が溝23を覆うように設けられる。

(もっと読む)

歪チャネルを有するMOSトランジスタを製造する方法

【課題】歪チャネルを有するMOS トランジスタを製造するための比較的簡単な方法を提供する。

【解決手段】歪チャネルを有するMOS トランジスタ(M) を製造する方法は、(a) 半導体基板(10)の表面に、ソース領域及びドレイン領域とMOS トランジスタを囲む絶縁領域(22)に部分的に延びる絶縁された犠牲ゲートとを備えたMOS トランジスタを形成するステップと、(b) 犠牲ゲートの上面と略同一の高さの上面を有する絶縁層を形成するステップと、(c) 犠牲ゲートを除去するステップと、(d) 露出した絶縁領域(22)の少なくとも上部分をエッチングしてトレンチを形成するステップと、(e) 半導体基板(10)を歪ませることが可能な材料(24)をトレンチに充填するステップと、(f) 犠牲ゲートの除去によって空いた空間にMOS トランジスタの絶縁ゲート(12)を形成するステップとを有する。

(もっと読む)

半導体装置

【課題】ドレインオフセット領域を有する高周波増幅用MOSFETにおいて、微細化およびオン抵抗低減を図る。

【解決手段】ソース領域10、ドレイン領域9およびリーチスルー層3(4)上に電極引き出し用の導体プラグ13(p1)が設けられている。その導体プラグ13(p1)にそれぞれ第1層配線11s、11d(M1)が接続され、さらにそれら第1層配線11s、11d(M1)に対して、導体プラグ13(p1)上で裏打ち用の第2層配線12s、12dが接続されている。

(もっと読む)

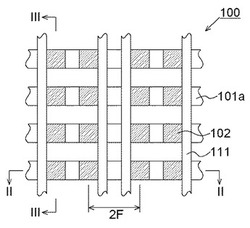

多勾配ドレインドーピング特性を持つ高電圧縦型トランジスタ

【課題】デバイスのオン状態及びオフ状態の両方の破壊電圧を同時に最適化する高電圧トランジスタ構造。

【解決手段】高電圧トランジスタは、半導体基板のメサを定める第一及び第二の溝を含む。第一及び第二のフィールドプレート部材は、それぞれ、第一及び第二の溝に配置され、第一及び第二のフィールドプレート部材の各々は、誘電体層でメサから分離されている。メサは複数の部分を含み、各部分は、実質的に一定のドーピング濃度勾配を持ち、一の部分の勾配は、他の部分の勾配よりも少なくとも10%大きい。

(もっと読む)

可動ゲート型電界効果トランジスタ

【課題】可動ゲート電極の変位を制御可能な可動ゲート型電界効果トランジスタを提供する。

【解決手段】ソース電極17とドレイン電極18との上に導電シールド電極20が配置される可動ゲート型電界効果トランジスタ1とした。そして導電シールド電極20の電位を固定することとした。導電シールド電極20が配置されることにより、可動ゲート15とドレイン電極18またはソース電極17との間に発生する静電力を抑制することができる。

(もっと読む)

窒化物半導体装置

【課題】エンハンメント型GaN系HFETの閾値電圧のバラツキを低減する。

【解決手段】窒化物半導体装置80では、第2のリセスエッチングによりアンドープGaN層3の上部に突起部51が設けられる。突起部51上には、上部が第1のリセスエッチングにより形成されたアンドープAlGaN層4aが設けられる。積層部7は、アンドープGaN層3の突起部51、アンドープAlGaN層4a、及び絶縁膜5から構成される。トレンチ部8は、絶縁膜5、アンドープAlGaN層4a、及びアンドープGaN層3表面がリセスエッチングされたものである。積層部7及びトレンチ部8上にはゲート絶縁膜6が設けられる。ゲート絶縁膜6上には、トレンチ部8を覆うようにゲート電極33が設けられる。絶縁膜5はゲート絶縁膜6よりも膜厚が厚く設定されている。

(もっと読む)

BiCMOSプロセス技術における高電圧SCRMOS

集積回路が、ドレイン領域(1010)及びSCR端子(1012)の周りに、低減された表面フィールド(RESURF)領域(1024)と共に形成されるSCRMOSトランジスタを含む。RESURF領域は、ドリフト領域(1014)と同じ導電型であり、ドリフト領域(1014)より一層重くドープされる。  (もっと読む)

(もっと読む)

1 - 20 / 66

[ Back to top ]