Fターム[5F140CE10]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | 製造工程一般 (2,583) | 同一真空処理 (148)

Fターム[5F140CE10]に分類される特許

1 - 20 / 148

半導体装置の製造方法

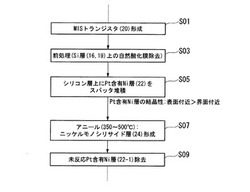

【課題】本発明は、シリコン層上に、抵抗値が低く、かつ平坦性の良好なニッケルモノシリサイド層を形成可能な半導体装置の製造方法を提供することを課題とする。

【解決手段】基板に形成されたシリコン層を覆ように白金を含むニッケル層を堆積する工程であって、シリコン層に近い部分では遠い部分と比較して結晶性が低くなるように、白金を含むニッケル層を堆積する工程S05と、基板を加熱することで、シリコン層と白金を含むニッケル層との界面にニッケルモノシリサイド層を形成する工程S07と、を有する。

(もっと読む)

半導体装置の製造方法

【課題】金属シリサイド層の異常成長を防止する。

【解決手段】半導体基板1にゲート絶縁膜5、ゲート電極6a,6b、ソース・ドレイン用のn+型半導体領域7bおよびp+型半導体領域8bを形成する。それから、サリサイド技術によりゲート電極6a,6bおよびソース・ドレイン領域上に金属シリサイド層13を形成する。そして、金属シリサイド層13の表面を還元性ガスのプラズマで処理してから、半導体基板1を大気中にさらすことなく、金属シリサイド層13上を含む半導体基板1上に窒化シリコンからなる絶縁膜21をプラズマCVD法で堆積させる。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体装置のトランジスタのシリコンピラー上部に活性領域を設ける際に、エピタキシャル成長により前記シリコンピラー上部に形成されるシリコン膜の高さが、前記トランジスタ毎にばらつくことを防ぎ、前記シリコン膜への導電型ドーパントの注入深さを均一にする半導体装置の製造方法を提供する。

【解決手段】基板の主面に柱状のシリコンピラーを形成するシリコンピラー形成工程と、前記シリコンピラーを覆うように第1の絶縁膜を形成する第1絶縁膜形成工程と、前記第1の絶縁膜を上面から除去し、前記シリコンピラー上部の上面及び側面を露出させる第1絶縁膜除去工程と、前記シリコンピラー上部の上面及び側面にエピタキシャル成長法によりシリコン膜を形成するシリコン膜形成工程とを有する。

(もっと読む)

半導体装置の製造方法

【課題】ヒ素(As)を高濃度にドーピングした状態でエクステンション領域のエピタキシャル成長膜表面に凹凸を発生させることなく、平滑な面に形成することを可能とする。

【解決手段】半導体基板11上にゲート絶縁膜12を介してゲート電極13を備え、前記ゲート電極13の両側の前記半導体基板11上に形成された不純物を含有してなるエクステンション領域17、18を備えた半導体装置1であって、前記エクステンション領域17、18は、シリコンゲルマニウムにヒ素を含む状態でエピタキシャル成長されたエピタキシャル成長膜からなり、このエピタキシャル成長膜は、ヒ素をドーピングしながらシリコンとゲルマニウムとを前記半導体基板11上に選択的にエピタキシャル成長させて形成される。

(もっと読む)

基板処理方法および基板処理装置

【課題】シリコン酸化膜の除去後、シリコンゲルマニウム膜の形成までのQタイムを長くするとともに、シリコンゲルマニウム膜の形成におけるプリベイクの温度を低くする。

【解決手段】基板処理装置1では、酸化膜除去部4にて基板9の一の主面上のシリコン酸化膜が除去された後、シリル化処理部6にてシリル化材料を付与して、当該主面に対してシリル化処理が施される。これにより、シリコン酸化膜の除去後、シリコンゲルマニウム膜の形成までのQタイムを長くするとともに、シリコンゲルマニウム膜の形成におけるプリベイクの温度を低くすることができる。

(もっと読む)

代用ソース/ドレインフィンFET加工

【課題】finFETにおける高集積化可能な、高濃度ソースドレインの形成方法の提供。

【解決手段】ソース領域、ドレイン領域およびソース領域とドレイン領域の間のチャネル領域を有するフィンを形成する。チャネル領域にダイレクトコンタクトする絶縁層と、絶縁層にダイレクトコンタクトする伝導性のゲート物質とを有するゲートスタックを形成する。チャネル領域を残したまま、ソース領域およびドレイン領域をエッチング除去する。ソース領域およびドレイン領域に隣接したチャネル領域の両側にソースエピタキシー領域およびドレインエピタキシー領域を形成する。ソースエピタキシー領域およびドレインエピタキシー領域は、エピタキシャル半導体を成長させながら、その場ドープされる。

(もっと読む)

半導体装置およびその製造方法

【課題】第1の領域のゲート絶縁膜への酸化剤の進入を防止しつつ、第2の領域の複数の第1の配線間に設けられた酸化アルミニウム膜を選択的に除去する。

【解決手段】第1の領域において第1の積層体の側壁を覆い、第2の領域において複数の第1の配線を覆うように形成した第1の絶縁膜をマスクとして、第1の領域に第1のイオン注入を施す。その後、第1の領域において第1の積層体の側壁を覆い、第2の領域において複数の第1の配線間を埋設するように形成した、酸化アルミニウムを主体とする第2の絶縁膜をマスクとして、第1の領域に第2のイオン注入を施す。第2の絶縁膜を、第1の絶縁膜に対して選択的に除去する。

(もっと読む)

コーナートランジスターとその製作方法

【課題】改善された性能を有し、かつ縮小されたサイズを有することのできるコーナートランジスターを提供する。また、コーナートランジスターを製作する方法を提供し、それがトランジスターの性能を改善するとともに、簡単なプロセスを介して、そのサイズを縮小することができる。

【解決手段】この発明のコーナートランジスターを製作する方法を以下に記述する。分離構造(isolation structure)が基板中に形成されて能動エリア(active area)を定義する。処理プロセスが実施されて、能動エリア中の基板がそのトップエッジに鋭いコーナーを有するようにする。能動エリア中の基板がゲート誘電層により被覆される。ゲート導体がゲート誘電層上に形成される。ソース領域およびドレイン領域がゲート導体両側の基板中に形成される。

(もっと読む)

高有効仕事関数で電極を堆積する方法

【課題】半導体処理の方法が提供される。

【解決手段】いくつかの実施形態によれば、高い有効仕事関数を有する電極が形成される。この電極は、トランジスタのゲート電極であってもよく、導電材料の第1の層を堆積し、第1の層を水素含有ガスに露出し、第1の層に導電材料の第2の層を堆積することにより、high−kゲート誘電体に形成されてもよい。第1の層は、基板がプラズマ又はプラズマ発生ラジカルに露出されないプラズマ無しプロセス(non−plasma process)を用いて堆積される。第1の層が露出される水素含有ガスは、励起された水素種を含んでもよく、これは水素含有プラズマの一つであってもよく、水素含有ラジカルであってもよい。第2の層を堆積する前に、第1の層もまた、酸素に露出されてもよい。ゲートスタックのゲート電極の仕事関数は、いくつかの実施形態において約5eV又はそれ以上であってもよい。

(もっと読む)

プラズマ窒化ゲート誘電層における窒素プロフィルを改善する方法

【課題】プラズマ窒化ゲート誘電層における窒素プロファイルを改善する為の方法を提供する。

【解決手段】基板を処理する方法において:基板が、あるシステム10の窒化用チャンバ20B内に置かれている間に、前記基板上に形成されたゲート誘電層に窒素(N)を導入するステップと;前記システム10から前記基板を外に搬送することなく、前記基板を前記システム10のアニール用チャンバ20Cに搬送するステップと;前記窒化用チャンバ20B内の前記基板の温度を超える温度まで、前記アニール用チャンバ20C内で前記基板を加熱することにより、前記ゲート誘電層をアニールするステップと;を備え、前記アニールの間、前記アニール用チャンバ20C内の圧力は、少なくとも50トルであり、前記基板を、前記窒素が導入された後、5分以内にアニールする、前記方法。

(もっと読む)

CVDエッチングおよび堆積シーケンスにより形成されるCMOSトランジスタ接合領域

【課題】CMOSトランジスタのソース−ドレイン置換技術に関し、装置一式を利用して基板材料に窪みをエッチングして、その後、応力を有する異なる材料を堆積することに関し、大気に曝すことなく、エッチングとその後の堆積とを行う方法の提供。

【解決手段】エッチングおよびデポジションによりCMOSトランジスタの接合領域を形成する方法であって、

第1接合領域270を形成すべくゲート電極190の隣の基板120の第1箇所と、前記基板120に第2接合領域280を形成すべく前記ゲート電極190を介して前記第1箇所とは反対側に位置する前記基板120の第2箇所とを除去する工程と、前記第1接合領域270と前記第2接合領域280とに結晶質材料のエピタキシャル厚みを有する層を形成する工程とを含み、前記除去する工程と前記形成する工程は同一のチャンバ内で前記チャンバの封止を破ることなく行う。

(もっと読む)

TiC膜を含む半導体構造を形成する方法

【課題】 TiC膜を含む半導体構造を形成する方法を提供する。

【解決手段】 高誘電率(k)の誘電体14および界面層12を含む積層体を基板10の表面上に設けるステップと、Heによって希釈された炭素(C)源およびArを含む雰囲気において、Tiターゲットをスパッタすることにより、前記積層体上にTiC膜16を形成するステップとを含む、半導体構造を形成する方法である。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】特性の良好な半導体装置を形成する。

【解決手段】本発明は、pチャネル型MISFETをpMIS形成領域1Aに有し、nチャネル型MISFETをnMIS形成領域1Bに有する半導体装置の製造方法であって、HfON膜5上にAl膜8aを形成する工程と、Al膜上にTiリッチなTiN膜7aを形成する工程と、を有する。さらに、nMIS形成領域1BのTiN膜およびAl膜を除去する工程と、nMIS形成領域1BのHfON膜5上およびpMIS形成領域1AのTiN膜7a上にLa膜8bを形成する工程と、La膜8b上にNリッチなTiN膜7bを形成する工程と、熱処理を施す工程とを有する。かかる工程によれば、pMIS形成領域1Aにおいては、HfAlON膜のN含有量を少なくでき、nMIS形成領域1Bにおいては、HfLaON膜のN含有量を多くできる。よって、eWFを改善できる。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】窒化金属膜から放出される窒素がゲート絶縁膜に到達することを抑制する。

【解決手段】この半導体装置は、半導体基板100、第1ゲート絶縁膜110、シリコン含有第2ゲート絶縁膜122、及び第1ゲート電極を備えている。第1ゲート絶縁膜110は半導体基板100上に形成されており、酸化シリコン又は酸窒化シリコンよりも比誘電率が高い材料から構成されている。シリコン含有第2ゲート絶縁膜122は、第1ゲート絶縁膜110上に形成されている。第1ゲート電極はシリコン含有第2ゲート絶縁膜122上に形成されており、窒化金属層124を有している。第1ゲート絶縁膜110、シリコン含有第2ゲート絶縁膜122、及び窒化金属層124は、pMOSFETの一部を構成している。

(もっと読む)

窒化物半導体装置及びその製造方法

【課題】特性の安定化を達成できる窒化物半導体装置及びその製造方法を提供する。

【解決手段】窒化物半導体装置110は、第1半導体層3、第2半導体層4、第3半導体層5、第4半導体層6、第1電極10、第2電極8及び第3電極9を備える。第1半導体層3、第2半導体層4、第3半導体層5及び第4半導体層6は、窒化物半導体を含む。第2半導体層4は、第1半導体層3の禁制帯幅以上の禁制帯幅を有する。第3半導体層5は、GaNである。第4半導体層6は、第3半導体層5の上において一部に隙間を有して設けられ、第2半導体層4の禁制帯幅以上の禁制帯幅を有する。第1電極10は、第3半導体層5の上において第4半導体層6が設けられていない部分に設けられる。第2電極8及び第3電極9は、第4半導体層6の上において、第1電極10の一方側及び他方側にそれぞれ設けられ、第4半導体層6とオーミック接合している。

(もっと読む)

シリサイド化金属ゲートの形成のための方法

【課題】シリサイド化金属ゲートと、シリサイド化ソース領域およびドレイン領域とを備える進歩したゲート構造物と、同ゲート構造物を製造する方法と、を提供する。

【解決手段】シリサイド化金属ゲートと、シリサイド化金属ゲートに接するシリサイド化ソース領域およびドレイン領域とを備える進歩したゲート構造物を提供する。詳しくは、広義に、第一の厚さを有する第一のシリサイド金属のシリサイド化金属ゲートと、隣接する第二の厚さを有する第二の金属のシリサイド化ソース領域およびドレイン領域とを含み、第二の厚さは第一の厚さより薄く、シリサイド化ソース領域およびドレイン領域は少なくともシリサイド化金属ゲートを含むゲート領域の端に位置合わせした半導体構造物を提供する。さらに、シリサイド化金属ゲートと、シリサイド化金属ゲートに接するシリサイド化ソース領域およびドレイン領域とを備える進歩したゲート構造物を製造する方法も提供する。

(もっと読む)

絶縁膜の改質方法

【課題】 プラズマ窒化処理によって形成した酸化窒化珪素膜からのN抜けによる膜中窒素濃度の低下を抑制し、被処理体間・ロット間での窒素濃度のばらつきを最小限にする。

【解決手段】 絶縁膜の改質方法は、被処理体の表面に露出した酸化珪素膜をプラズマ窒化処理し、酸化窒化珪素膜を形成する窒化処理工程と、前記酸化窒化珪素膜の表面を酸化処理する改質工程とを行い、窒化処理工程の終了から前記改質工程の開始までの間、真空雰囲気を維持する。また、プラズマ窒化処理は、窒化処理工程直後の酸化窒化珪素膜の膜中窒素濃度をNC0とし、改質工程後の酸化窒化珪素膜の膜中窒素濃度の目標値をNCTとしたとき、NC0>NCTとなるように行う。

(もっと読む)

半導体装置の製造方法

【課題】 チャネル領域に応力を印加するよう作用する階段状のソース/ドレイン・エピタキシャル領域を、製造プロセスを有意に複雑あるいは冗長とすることなく形成する。

【解決手段】 ゲート電極をマスクとしてドーパントを注入し、半導体基板内にドーパント注入領域を形成する(S2)。サイドウォールの形成(S3)後、ゲート電極及びサイドウォールをマスクとして半導体基板内に第1のリセスを形成する(S4)。このとき、第1のリセスの内壁の一部からドーパント注入領域が露出される。その後、上記ドーパント注入領域を選択エッチングにより除去し、第1のリセスに連通し且つ第1のリセスより浅い第2のリセスを形成する(S5)。それにより、階段状のリセスが形成される。そして、第1のリセス及び第2のリセス内に、チャネル領域へのストレッサとして作用する半導体材料を成長させてソース/ドレイン領域を形成する(S6)。

(もっと読む)

炭化珪素半導体装置の製造方法および炭化珪素半導体装置の製造装置

【課題】特性を向上できるSiC半導体装置の製造方法およびSiC半導体装置の製造装置を提供する。

【解決手段】SiC半導体装置の製造方法は、SiC半導体の第1の表面に第1の酸化膜を形成する工程(ステップS4)と、第1の酸化膜を除去する工程(ステップS5)と、SiC半導体において第1の酸化膜が除去されることにより露出した第2の表面に、SiC半導体装置を構成する第2の酸化膜を形成する工程(ステップS6)とを備える。第1の酸化膜を除去する工程(ステップS4)と、第2の酸化膜を形成する工程(ステップS6)との間において、SiC半導体は大気が遮断された雰囲気内に配置される。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の性能を向上させる。

【解決手段】半導体基板1の主面にゲート絶縁膜用のHf含有膜4、Al含有膜5及びマスク層6を形成してから、nチャネル型MISFET形成予定領域であるnMIS形成領域1Aのマスク層6とAl含有膜5を選択的に除去する。それから、nMIS形成領域1AのHf含有膜4上とpチャネル型MISFET形成予定領域であるpMIS形成領域1Bのマスク層6上に希土類含有膜7を形成し、熱処理を行って、nMIS形成領域1AのHf含有膜4を希土類含有膜7と反応させ、pMIS形成領域1BのHf含有膜4をAl含有膜5と反応させる。その後、未反応の希土類含有膜7とマスク層6を除去してから、メタルゲート電極を形成する。マスク層6は、窒化チタン又は窒化タンタルからなる窒化金属膜6aと、その上のチタン又はタンタルからなる金属膜6bとの積層構造を有する。

(もっと読む)

1 - 20 / 148

[ Back to top ]