Fターム[5F140CE18]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | 製造工程一般 (2,583) | 局所的アニール (144)

Fターム[5F140CE18]に分類される特許

1 - 20 / 144

半導体装置の製造方法

【課題】高いオン電流を得つつ、オフリーク電流を抑制することができる半導体装置を簡単に製造することができる方法を提供する。

【解決手段】半導体装置の製造方法は、半導体基板上にゲート絶縁膜を形成する。ゲート絶縁膜上にゲート電極を形成する。ドレイン層形成領域に第1導電型の不純物を導入する。次に、熱処理を行うことによってドレイン層形成領域の第1導電型の不純物を活性化する。次に、ソース層形成領域に不活性不純物を導入することによって該ソース層形成領域の半導体基板の単結晶をアモルファス化する。次に、ソース層形成領域に第2導電型の不純物を導入する。次に、半導体基板にマイクロ波を照射することによって少なくともソース層形成領域のアモルファス半導体を単結晶化し、かつ、ソース層形成領域の第2導電型の不純物を活性化する。ソース層形成領域における第2導電型の不純物の深さは、ドレイン層形成領域における第1導電型の不純物の深さよりも浅い。

(もっと読む)

半導体装置、電気光学装置、電力変換装置及び電子機器

【課題】素子特性の低下を抑制することが可能な半導体装置を提供する。

【解決手段】シリコン基板11と、シリコン基板11の表面に形成された炭化シリコン膜12と、炭化シリコン膜12の表面に形成された、開口部13hを有するマスク材13と、開口部13hにおいて露出した炭化シリコン膜12を基点としてエピタキシャル成長された、炭化シリコン膜12及びマスク材13を覆う単結晶炭化シリコン膜14と、単結晶炭化シリコン膜14の表面に形成された半導体素子20と、を含み、マスク材13の上には、単結晶炭化シリコン膜14が会合して形成された会合部12Sbが存在しており、半導体素子20はボディコンタクト領域21を有しており、ボディコンタクト領域21は、シリコン基板11の表面と直交する方向から見て会合部12Sbと重なる位置に配置されている。

(もっと読む)

半導体装置の製造方法、半導体装置

【課題】SiCが用いられる半導体層中において、簡易な工程で再現性よく埋め込み絶縁層を形成する。

【解決手段】単結晶のSiC12の表面の温度を局所的に急激に上昇させ、その後で急激に冷却することによって、単結晶を局所的に非晶質化層30を形成することができる。この非晶質層30は、元の単結晶SiCの導電型や抵抗率に関わらず、高抵抗層(絶縁層)となる。このため、こうした非晶質層を埋め込み絶縁層と同様に使用することができる。このためには、(1)レーザー光を効率的に吸収する層100を局所的に半導体層の上に形成してからレーザー光を照射する、(2)レーザー光を局所的に半導体層に照射する、という2つの手段のいずれかを用いることができる。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】歩留まりを向上可能な半導体装置の製造方法および半導体装置を提供すること。

【解決手段】実施形態によれば、半導体装置の製造方法が提供される。半導体装置の製造方法は、半導体基板上に形成される検査用トランジスタおよび製品用トランジスタのソースおよびドレインを活性化させるアニール処理を行うアニール工程と、アニール工程後における検査用トランジスタのゲート、ソースおよびドレインをシリサイド化させる検査用サリサイド工程と、検査用サリサイド工程後における検査用トランジスタの特性を測定する測定工程と、測定工程によって測定された特性と所望の特性との差分とに基づいて製品用トランジスタの特性を所望の特性へ近付ける特性調整アニール処理を行う特性調整アニール工程と、特性調整アニール工程後における製品用トランジスタのゲート、ソースおよびドレインをシリサイド化させる本サリサイド工程とを含む。

(もっと読む)

半導体装置の製造方法

【課題】王水を用いることなくニッケルプラチナ膜の未反応部分を選択的に除去しうるとともに、プラチナの残滓が半導体基板上に付着するのを防止しうる半導体装置の製造方法を提供する。

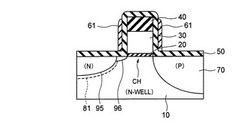

【解決手段】シリコン基板10上に、ゲート電極16と、ゲート電極16の両側のシリコン基板10内に形成されたソース/ドレイン拡散層24とを有するMOSトランジスタ26を形成し、シリコン基板10上に、ゲート電極16及びソース/ドレイン拡散層24を覆うようにNiPt膜28を形成し、熱処理を行うことにより、NiPt膜28とソース/ドレイン拡散層24の上部とを反応させ、ソース/ドレイン拡散層24上に、Ni(Pt)Si膜34a、34bを形成し、過酸化水素を含む71℃以上の薬液を用いて、NiPt膜28のうちの未反応の部分を選択的に除去するとともに、Ni(Pt)Si膜34a、34bの表面に酸化膜を形成する。

(もっと読む)

窒化物半導体装置および窒化物半導体装置の製造方法

【課題】オン抵抗が低く、かつ、Vth(閾値電圧)が高い窒化物半導体装置の提供。

【解決手段】アクセプタになるアクセプタ元素を含み、窒化物半導体で形成されたバックバリア層106と、バックバリア層106上に窒化物半導体で形成されたチャネル層108と、チャネル層108の上方に、チャネル層よりバンドギャップが大きい窒化物半導体で形成された電子供給層112と、チャネル層108と電気的に接続された第1主電極116、118と、チャネル層108の上方に形成された制御電極120と、を備え、バックバリア層106は、制御電極120の下側の領域の少なくとも一部に、アクセプタの濃度がバックバリア層の他の一部の領域より高い高アクセプタ領域126を有する窒化物半導体装置100。

(もっと読む)

半導体装置の製造方法

【課題】王水を用いることなくニッケルプラチナ膜の未反応部分を選択的に除去しうるとともに、プラチナの残滓が半導体基板上に付着するのを防止しうる半導体装置の製造方法を提供する。

【解決手段】シリコン基板10上に、ゲート電極16と、ゲート電極16の両側のシリコン基板10内に形成されたソース/ドレイン拡散層24とを有するMOSトランジスタ26を形成し、シリコン基板10上に、ゲート電極16及びソース/ドレイン拡散層24を覆うようにNiPt膜28を形成し、熱処理を行うことにより、NiPt膜28とソース/ドレイン拡散層24の上部とを反応させ、ソース/ドレイン拡散層24上に、Ni(Pt)Si膜34a、34bを形成し、過酸化水素を含む71℃以上の薬液を用いて、NiPt膜28のうちの未反応の部分を選択的に除去するとともに、Ni(Pt)Si膜34a、34bの表面に酸化膜を形成する。

(もっと読む)

半導体シリコン膜及び半導体デバイス、並びにそれらの製造方法

【課題】本発明の目的は、新規な半導体シリコン膜及びそのような半導体シリコン膜を有する半導体デバイス、並びにそれらの製造方法を提供することである。

【解決手段】本発明の半導体シリコン膜(160)は、複数の細長シリコン粒子(22)が短軸方向に隣接してなる半導体シリコン膜である。ここでは、細長シリコン粒子(22)は、複数のシリコン粒子の焼結体である。また、このような半導体シリコン膜(160)を製造する本発明の方法は、第1のシリコン粒子分散体を、基材(100)上に塗布し、乾燥し、光(200)を照射して、第1の半導体シリコン膜(130)を形成する工程、第2のシリコン粒子分散体を、第1の半導体シリコン膜(130)に塗布し、乾燥し、光(200)を照射する工程を含む。ここで、この方法では、第1のシリコン粒子分散体の第1のシリコン粒子の分散が5nm2以上である。

(もっと読む)

半導体集積回路装置の製造方法

【課題】高誘電率ゲート絶縁膜を用いたCMIS型半導体集積回路において、短チャネル長、且つ狭チャネル幅のデバイス領域では、ソースドレイン領域の活性化アニールによって、高誘電率ゲート絶縁膜とシリコン系基板部との界面膜であるILの膜厚が増加することによって、閾値電圧の絶対値が増加するという問題がある。

【解決手段】本願の一つの発明は、MISFETを有する半導体集積回路装置の製造方法において、MISFETのゲートスタック及びその周辺構造を形成した後、半導体基板表面を酸素吸収膜で覆い、その状態でソースドレインの不純物を活性化するためのアニールを実行し、その後、当該酸素吸収膜を除去するものである。

(もっと読む)

トランジスタ及びその製造方法

【課題】駆動電流を向上したnMOSトランジスタを備えた半導体装置を実現できるようにする。

【解決手段】半導体装置は、半導体基板の素子領域101の上にゲート絶縁膜111を介在させて形成されたゲート電極112と、素子領域101におけるゲート電極112の両側方に形成され、n型不純物及び炭素を含むソースドレイン領域122とを備えている。ソースドレイン領域122を構成するシリコン及びソースドレイン領域122に含まれる炭素の少なくとも一方は、主同位体よりも質量数が大きい安定同位体の存在比が、天然存在比よりも高い。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の特性を劣化させることなく、浅い接合の半導体装置を提供する。

【解決手段】まず、半導体基板上に、ゲート絶縁膜を形成する(s100)。次いで、ゲート絶縁膜上にゲート電極を形成する(s200)。次いで、ゲート電極を形成する工程(s200)の後、第一アニール工程を行う(s300)。次いで、第一アニール工程(s300)の後、ゲート電極の両側における半導体基板に、ポケット領域およびエクステンション領域を構成する不純物注入を行う(s400)。その不純物注入を行う工程(s400)の後、第二アニール工程として、最高アニール温度が1000℃以上で、アニール時間が100ミリ秒以下であるアニールを行う(s700)。

(もっと読む)

半導体装置の製造方法

【課題】レーザ光の照射を利用したエッチング加工による半導体装置の製造方法であって、複雑形状や深くて大きい除去領域等のエッチング加工が必要な広範囲の半導体装置の製造に適用可能で、高いエッチング速度が得られる半導体装置の製造方法を提供する。

【解決手段】単結晶シリコンからなる基板10に対して、焦点位置を移動させてレーザ光Lをパルス照射し、前記単結晶シリコンを部分的に多結晶化して、前記単結晶シリコン中に連続した改質層11を形成する改質層形成工程と、前記改質層11をエッチングして除去するエッチング工程と、を備える半導体装置の製造方法とする。

(もっと読む)

MOSゲート型炭化珪素半導体装置の製造方法

【目的】チャネル移動度を大きくし、チャネル抵抗を低減できるMOSゲート型炭化珪素半導体装置の提供。

【構成】トレンチの側壁に接するゲート酸化膜とチャネル反転層表面との間に他導電型シリコン半導体層が形成されるMOSゲート型炭化珪素半導体装置であって、他導電型シリコン半導体層がアモルファスシリコン層で形成し、レーザー光を前記アモルファスシリコン層に対して前記MOSゲート型炭化珪素半導体装置のチャネル電流が流れる方向と交差しない方向へスキャンしてアモルファスシリコン層をポリシリコンに変換する。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の製造歩留りを向上させる。

【解決手段】ウエハ(半導体ウエハ)WHの主面1a側に、周縁領域1dからデバイス領域1cを経由して前記周縁領域に至る走査軌道15に沿ってレーザ光LZを照射し、ウエハWHの主面1a側を加熱するレーザアニール処理工程を以下のように行う。ウエハWHの周縁領域1dには、第1出力PW1でレーザ光LZを照射し、ウエハWHのデバイス領域1cには、第1出力PW1よりも高い第2出力PW2でレーザ光LZを照射する。そして、半導体基板1の線膨張係数をα1、絶縁膜の残存膜2の線膨張係数をα2、レーザ光LZが照射された時の半導体基板1の温度をT1、レーザ光LZが照射された時の残存膜2の温度をT2とした時、α1×T1≧α2×T2とする。

(もっと読む)

半導体装置及びその製造方法

【課題】High-kゲート絶縁膜を用いたMOSFETにおいて、信頼性劣化、チャネル移動度低下及びEOTの増加を抑制する方法を提供する。

【解決手段】半導体装置の製造方法は、半導体基板101上に、シリコン酸化物を含む第1絶縁層104を形成する工程(a)と、第1絶縁層104上に第1金属層105を形成する工程(b)と、第1金属層105上にゲート電極108を形成する工程(c)とを備える。第1絶縁層104及び第1金属層105からゲート絶縁膜を形成する。

(もっと読む)

半導体素子、及び半導体装置

【課題】半導体素子の微細化に伴うゲート電極サイズの微細化においても、ゲート電極とチャネル形成領域間のリーク電流が抑制された半導体素子を提供することを課題の一とする。また、小型かつ高性能な半導体装置を提供することを課題の一とする

【解決手段】チャネル形成領域として機能する半導体層上に、ゲート絶縁膜として比誘電率が10以上の酸化ガリウムを含む絶縁膜を形成し、前記酸化ガリウム上にゲート電極が形成された構造を有する半導体素子を作製することにより、課題の一を解決する。また、前記半導体素子を用いて半導体装置を作製することにより、課題の一を解決する。

(もっと読む)

半導体装置

【課題】導電膜を有する半導体装置は、導電膜の内部応力の影響を受ける。内部応力について検討する。

【解決手段】絶縁表面上に設けられたnチャネル型TFTを有する半導体装置は、半導体膜が引っ張り応力を受けるように、導電膜、例えばゲート電極に不純物元素が導入され、絶縁表面上に設けられたpチャネル型TFTを有する半導体装置は、半導体膜が圧縮応力を受けるように、導電膜、例えばゲート電極に不純物が導入されている。

(もっと読む)

半導体装置およびその製造方法

【課題】微細化が進んだ場合であっても、適切なしきい値電圧を有するpチャネルMOSFETを含む半導体装置を製造する。

【解決手段】本発明に係る半導体装置の製造方法は、半導体基板101上に、SiO2またはSiONを含む第1ゲート絶縁層104を形成する第1ゲート絶縁層形成ステップと、第1ゲート絶縁層104上に、金属酸化物を含む第2ゲート絶縁層105を形成する第2ゲート絶縁層形成ステップと、第2ゲート絶縁層105上に、金属を含む第1電極106aを形成する第1電極形成ステップと、形成された積層構造に、複数回のミリセカンドアニール処理を行うことで、第2ゲート絶縁層105および第1電極106aの少なくとも一方に含まれる4族、5族または13族の元素を、第1ゲート絶縁層104と第2ゲート絶縁層105との界面に拡散させるアニールステップとを含む。

(もっと読む)

半導体装置の製造方法

【課題】不純物拡散領域の抵抗値のばらつきを抑制しうる半導体装置の製造方法を提供する。

【解決手段】半導体層にドーパント不純物を添加し、0.1秒〜10秒の活性化熱処理を行う。次いで、半導体層にイオン注入を行い、半導体層のドーパント不純物が添加された領域をアモルファス化する。次いで、0.1ミリ秒〜100ミリ秒の活性化熱処理を行い、アモルファス化した半導体層を再結晶化することにより、半導体層にドーパント不純物の拡散領域を形成する。

(もっと読む)

半導体装置

【課題】メタルゲート電極内に基板面に対して平行な金属とシリコンなどとの境界又はシリサイドとシリコンなどとの境界を含むメタルゲート電極において、トランジスタの接続抵抗が小さく、高速動作時のトランジスタの遅延又はトランジスタ特性のばらつきなどの特性劣化の懸念がなく、且つ、低コストな構造を有する半導体装置を提供する。

【解決手段】半導体装置は、半導体基板101上に、ゲート絶縁膜105と、pMIS用金属材料109又はnMIS用金属材料111と、ゲート電極材料112と、ゲート側壁メタル層122とを備えている。

(もっと読む)

1 - 20 / 144

[ Back to top ]