Fターム[5F140CF00]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | 同時工程 (1,387)

Fターム[5F140CF00]の下位に属するFターム

配線とゲート電極 (16)

抵抗とゲート電極 (10)

多結晶と単結晶の同時成長 (13)

SD上とゲート電極上のシリサイド (873)

SD上とゲート電極上のプラグ (157)

SD拡散領域とゲート電極への拡散・注入 (182)

チャネルとパンチスルーストッパ (1)

Fターム[5F140CF00]に分類される特許

1 - 20 / 135

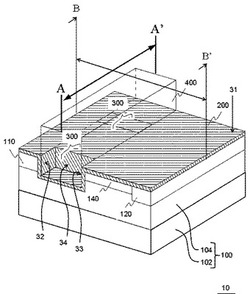

半導体装置および半導体装置の製造方法

【課題】電界が局所的に集中することを抑制して、高耐圧化した半導体装置を提供する。

【解決手段】ソース領域110は、溝部300側面の第2面32に面し、一部が面31と面32の交線と平行な方向に延在する。ドリフト領域140は、溝部300のうち面32と反対の面33に面し、一部が面31および面33の交線と平行な方向に延在して設けられ、ソース領域110よりも低濃度に形成される。ドレイン領域120は、ドリフト領域140を介し溝部300の反対側に位置し、ドリフト領域140と接するように設けられ、ドリフト領域140よりも高濃度に形成される。第1ゲート絶縁層200は、溝部300の側面のうち面32と面33に交わる方向の面である面34と接するとともに、面31上のうち少なくともチャネル領域130と接する。ゲート電極400は、第1ゲート絶縁層200上に設けられ。溝部300はドリフト領域140よりも深い。

(もっと読む)

高電子移動度トランジスタとその製造方法

【課題】高電子移動度トランジスタにおいて、ゲート部のドレイン側端部における電界集中を緩和する。

【解決手段】高電子移動度トランジスタ10は、導電体部23と第1抵抗部R1と第2抵抗部R2を備えている。導電体部23は、ドレイン電極21とゲート部26の間に設けられている。第1抵抗部R1は、一端がドレイン電極21に電気的に接続されており、他端が導電体部23に電気的に接続されている。第2抵抗部R2は、一端がソース電極28に電気的に接続されており、他端が導電体部23に電気的に接続されている。

(もっと読む)

半導体装置およびその製造方法

【課題】仕事関数の異なる複数の電極層を有し、ゲート抵抗が低く、作製が容易なゲート電極を備える半導体装置を提供する。

【解決手段】実施形態によれば、半導体装置は、基板と、前記基板上に形成されたゲート絶縁膜とを備える。さらに、前記装置は、前記ゲート絶縁膜の上面に形成され、第1の仕事関数を有する第1の電極層と、前記ゲート絶縁膜の上面と前記第1の電極層の上面に連続して形成され、前記第1の仕事関数と異なる第2の仕事関数を有する第2の電極層と、を有するゲート電極と、前記ゲート電極の側面に形成された側壁絶縁膜とを備える。さらに、前記装置では、前記第1の電極層の上面の高さは、前記側壁絶縁膜の上面の高さよりも低い。

(もっと読む)

半導体装置及びその製造方法

【課題】高耐圧トランジスタの低濃度不純物拡散層がコンタミネーションから保護されて、半導体装置の特性を安定化できるようにする。

【解決手段】基板1の上に、ゲート絶縁膜3a及びゲート電極4aを順次形成し、ゲート電極4aをマスクとして基板1に不純物注入を行うことにより、基板1の上部におけるゲート電極4aの側方に低濃度不純物拡散層5aを形成する。続いて、ゲート電極4aの上から該ゲート電極4aの側方を通って低濃度不純物拡散層5aの上の一部までを連続して覆うように不純物拡散抑制膜7aを形成する。続いて、ゲート電極4a及び不純物拡散抑制膜7aをマスクとして基板1に不純物注入を行うことにより、基板1の上部におけるゲート電極4aの側方に、低濃度不純物拡散層5aよりも不純物濃度が高い高濃度不純物拡散層8aを形成する。その後に、不純物拡散抑制膜7aを残存させた状態で基板1に対して加熱処理を行う。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】高耐圧トランジスタ形成に適した半導体装置の新規な製造方法を提供する。

【解決手段】

半導体装置の製造方法は、シリコン基板に第1導電型第1領域と、第1領域に接する第2導電型第2領域を形成し、ゲート絶縁膜を形成し、第1領域と第2領域とに跨がるゲート電極を形成し、ゲート電極上から第2領域上に延在する絶縁膜を形成し、ゲート電極をマスクとし第2導電型不純物を注入してソース領域およびドレイン領域を形成し、ゲート電極および絶縁膜を覆って金属層を形成し熱処理を行って、ソース領域、ドレイン領域及びゲート電極にシリサイドを形成し、層間絶縁膜にソース領域、ドレイン領域、ゲート電極に達する第1、第2、第3コンタクトホール、及び絶縁膜に達する孔を形成し、第1〜第3コンタクトホール及び孔に導電材料を埋め込み、第1〜第3導電ビアと、孔の内部に配置された導電部材とを形成する。

(もっと読む)

半導体装置の製造方法

【課題】トレンチ横型パワーMOSFETにおいて、装置の信頼性を高めること。

【解決手段】半導体基板1の表面層にトレンチ5を形成する。トレンチ5は、半導体基板1の表面層を第1メサ領域41と第2メサ領域42に分割し、かつ第1メサ領域41と第2メサ領域42を交互に配置させる。第1メサ領域41および第2メサ領域42は、それぞれソース電流およびドレイン電流の引き出しをおこなう。第2メサ領域42は、半導体基板1からの深さが、第1メサ領域41よりも深くなっている。

(もっと読む)

半導体装置およびその製造方法

【課題】消費電力が低く、かつ、動作時の電流値が高い半導体装置およびその製造方法を提供する。

【解決手段】実施形態の半導体装置は、第1導電型の基板上のソース領域に形成された第2導電型の第1の不純物拡散層と、前記基板上のポケット領域に形成された第1導電型の第2の不純物拡散層と、前記基板上のドレイン領域に形成された第1導電型の第3の不純物拡散層と、前記第1乃至第3の不純物拡散層の表面上に形成されたゲート絶縁膜と、前記ゲート絶縁膜上に形成されたゲートと、を含む。前記ポケット領域は前記ソース領域に隣接し、リセスを有するように形成される。前記ゲートは、前記ゲート絶縁膜を介して前記リセスを埋め込むように前記ゲート絶縁膜上に形成される。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】良好なノーマリ・オフ動作を可能とすることに加え、アバランシェ耐量が大きく、外部のダイオードを接続することを要せず、確実に安定動作を得ることができる信頼性の高い高耐圧のHEMTを得る。

【解決手段】化合物半導体積層構造2に形成された電極用リセス2Cを、ゲート絶縁膜6を介して電極材料で埋め込むようにゲート電極7を形成すると共に、化合物半導体積層構造2に形成された電極用リセス2Dを、少なくとも電極用リセス2Dの底面で化合物半導体積層構造2と直接的に接するように電極材料で埋め込み、化合物半導体積層構造2とショットキー接触するフィールドプレート電極8を形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】素子分離用ゲート電極のみのしきい値電圧を高くすることができ、素子分離用ゲート電極の底部にチャネルが形成されない半導体装置を提供する。

【解決手段】半導体基板1に形成された複数の活性領域と、これら活性領域同士を区画する素子分離領域と、活性領域内を複数の素子領域に区画する第1素子分離用トレンチ32Aと、隣接する第1素子分離用トレンチ32A間に設けられ、第1素子分離用トレンチ32Aの深さよりも浅く形成されたゲートトレンチ31Aと、絶縁膜25を介して第1素子分離用トレンチ32A内に形成された素子分離用電極32と、ゲート絶縁膜26Aを介してゲートトレンチ31A内に形成されたゲート電極31と、を具備してなり、素子分離用電極32底部に成膜されている絶縁膜25の膜厚が、ゲート電極31の底部に成膜されているゲート絶縁膜26Aの膜厚よりも厚いことを特徴とする。

(もっと読む)

半導体装置の製造方法

【課題】MOSトランジスタの形成工程を利用して、トレンチアイソレーションを形成できるようにした半導体装置の製造方法を提供する。

【解決手段】シリコン基板1にDTI層20とMOSトランジスタとを有する半導体装置の製造方法であって、シリコン基板1に深いトレンチを形成し、トレンチが形成されたシリコン基板1に熱酸化を施して、PMOSトランジスタ50のゲート酸化膜13を形成すると同時に、トレンチの内側面にSiO2膜14を形成する。次に、トレンチを埋め込むようにシリコン基板1上にポリシリコン膜15を堆積し、このポリシリコン膜15をパターニングする。これにより、PMOSトランジスタ50のゲート電極17を形成すると同時に、トレンチ内にSiO2膜14とポリシリコン膜18とを含むDTI層20を形成する。

(もっと読む)

半導体装置の製造方法

【課題】半導体基板の主面上の洗浄効果を低下させることなく、電界効果トランジスタのゲート電極の側面上に形成されたオフセットスペーサ膜の除去を抑制する。

【解決手段】ゲート電極部Gn,Gpを覆うように、半導体基板1の主面上に薬液に対するエッチング速度が互いに異なる第1OSS膜10および第2OSS膜12を順次形成した後、異方性エッチングにより、ゲート電極部Gn,Gpの側面上に位置する第2OSS膜12を残して、他の部分に位置する第2OSS膜12を除去する。そして、ゲート電極部Gn,Gpと、ゲート電極部Gn,Gpの側面上に位置する第1OSS膜10および第2OSS膜12と、をマスクにして、半導体基板1に不純物をイオン注入した後、半導体基板1を薬液により洗浄して、露出している第1OSS膜10を除去する。

(もっと読む)

半導体装置の製造方法

【課題】製造工程を簡略化することの可能な半導体装置の製造方法を提供する。

【解決手段】半導体基板11上に、ダミーゲート電極及びダミーコンタクトプラグの側面を覆う層間絶縁膜16を形成後、ダミーゲート電極、ダミーコンタクトプラグを選択的に除去して、ゲート電極形成用溝17及びコンタクト孔18を同時に形成し、次いで、ゲート電極形成用溝17内、コンタクト孔18内、及び層間絶縁膜16の上面を覆う高誘電率絶縁膜42を成膜し、次いで、斜めイオン注入法により、ゲート電極形成用溝17の下部17Aに形成された高誘電率絶縁膜42にイオン注入しないように、高誘電率絶縁膜42を介して、半導体基板に不純物拡散領域15を形成し、次いで、イオン注入された高誘電率絶縁膜42を選択的に除去することで、ゲート電極形成用溝の下部にゲート絶縁膜を形成し、かつコンタクト孔から不純物拡散領域15の上面を露出させる。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】オン抵抗を低減した半導体装置の製造方法及び半導体装置を提供する。

【解決手段】実施形態によれば、半導体装置の製造方法は、半導体層の表面側に、第1のフィールド絶縁膜と前記第1のフィールド絶縁膜に対して離間し且つ前記第1のフィールド絶縁膜よりも浅い少なくとも1つの第2のフィールド絶縁膜とを同時に形成する工程を備えた。さらに、前記半導体層における前記第1のフィールド絶縁膜及び前記第2のフィールド絶縁膜が形成された領域に第1導電形のドリフト領域を形成する工程を備えた。さらに、前記半導体層における前記第1のフィールド絶縁膜側の表面に、前記ドリフト領域よりも第1導電形不純物濃度が高い第1導電形のドレイン領域を形成する工程を備えた。さらに、前記半導体層における前記第2のフィールド絶縁膜側の表面に、第1導電形のソース領域を形成する工程を備えた。

(もっと読む)

半導体装置

【課題】ドレインオフセット領域を有する高周波増幅用MOSFETにおいて、微細化およびオン抵抗低減を図る。

【解決手段】ソース領域10、ドレイン領域9およびリーチスルー層3(4)上に電極引き出し用の導体プラグ13(p1)が設けられている。その導体プラグ13(p1)にそれぞれ第1層配線11s、11d(M1)が接続され、さらにそれら第1層配線11s、11d(M1)に対して、導体プラグ13(p1)上で裏打ち用の第2層配線12s、12dが接続されている。

(もっと読む)

半導体装置およびその製造方法

【課題】オフトラ型ESD保護素子のESD耐量を増加する。

【解決手段】第2導電型ドレイン高濃度拡散層となる領域にトレンチを備え、トレンチ内に第2導電型の多結晶シリコン膜を埋め込むことで、第2導電型ドレイン高濃度拡散層の実効的な体積を増加することを実現する。これより、ゲート電極からドレインコンタクト孔の距離を大きくしたことと同じ効果が得られ、本発明の半導体装置はオフトラ型ESD保護素子として、素子サイズを変更しなくてもESD耐量の増加が可能となる。

(もっと読む)

半導体装置及びその製造方法

【課題】耐圧性の維持と低オン抵抗化との両立が可能なLDMOSトランジスタを提供する。

【解決手段】半導体装置は、第1導電型のドリフト拡散領域10と、第2導電型のボディ拡散領域2と、第1導電型のソース拡散領域6と、ドリフト拡散領域10の上部に形成されたトレンチ内に埋め込まれ、ボディ拡散領域2とは離間した位置に形成された絶縁膜14と、ドリフト拡散領域10の上部に形成され、絶縁膜14から見てソース拡散領域6と逆の方向に隣接する第1導電型のドレイン拡散領域7と、ボディ拡散領域2上からドリフト拡散領域10上を越えて絶縁膜14上にまで形成されたゲート電極5とを備えている。また、ドリフト拡散領域10は、基板内部領域11と、基板内部領域11よりも高濃度の第1導電型不純物を含む表面領域12とを有している。

(もっと読む)

高導電性のソース/ドレイン接点を有するIII族窒化物トランジスタ及びその製造方法

【課題】III族窒化物トランジスタのドレイン及びソース接点と、下位のドレイン及びソース領域の各々との間の抵抗を低減させる。

【解決手段】ゲート、ソース、及びドレイン領域上に延在するフィールド誘電体240にトレンチをエッチングする工程と、ゲート、ソース、及びドレイン領域上にゲート誘電体270を形成する工程と、ゲート誘電体上270にブランケット拡散バリア272を形成する工程と、ソース及びドレイン領域からブランケット拡散バリア272を除去する工程と、ゲート誘電体270をソース及びドレイン領域から除去し、ソース及びドレイン領域をほぼ露出させる工程とを含む。次いで、ソース及びドレイン領域に接点金属290を堆積することにより、オーミック接点を形成する。

(もっと読む)

半導体装置の製造方法

【課題】特性を十分に向上することができる半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法は、SiC膜11を形成する工程と、このSiC膜11の表面にSiを供給した状態で、このSiC膜11を熱処理する熱処理工程と、熱処理工程によってSiC膜11の表面に得られたファセットをチャネル16とする工程とを備えている。このようにすれば、Siを供給した状態でSiC膜11を熱処理することにより、SiC膜11をエネルギ的に安定な表面状態に再構成させることができる。その結果、一周期が100nm以上のファセットが得られ、ファセットの平坦部分の長さを従来に比べて長くすることができる。したがって、界面準位の密度を減少することによりキャリアの移動度を向上することができ、半導体装置の特性を十分に向上することができる。

(もっと読む)

半導体装置およびその製造方法

【課題】素子面積が小さくしかも素子の耐圧の高い半導体装置およびその製造方法を提供する。

【解決手段】基板11と、基板上に設けられた一導電型の第1の半導体層13と、第1の半導体層上に設けられた一導電型で低不純物濃度の第2の半導体層15と、アイソレーション領域50によって分離された素子領域71内に形成されたMOSトランジスタ75と、素子領域内に一主面から第1の半導体層に達して設けられた一導電型で高不純物濃度の領域17と、領域17とMOSトランジスタのドレイン領域35との間に設けられた絶縁領域60であって、一主面10から第1の半導体層13に達し、基板11に達していない絶縁領域60とを備える。

(もっと読む)

半導体装置およびその製造方法

【課題】適切な仕事関数を有する金属ゲート電極を備え、トランジスタ特性のばらつきが抑えられた半導体装置およびその製造方法を提供する。

【解決手段】半導体装置は、半導体基板1001と、半導体基板1001内に形成された第1導電型の第1の活性領域1003と、第1の活性領域1003上に形成された第1のゲート絶縁膜1030aと第1のゲート電極1032aとを有し、第1の活性領域1003上に形成された第1チャネル型の第1のMISFET1050とを備える。第1のゲート電極1032aは、第1のゲート絶縁膜1030a上に形成され、金属原子を含む第1の下部ゲート電極1011aと、炭素の単体を含む材料、または分子中に炭素を含む材料からなる第1の酸化防止膜1012aと、第1の上部ゲート電極1013aとを有している。

(もっと読む)

1 - 20 / 135

[ Back to top ]