Fターム[5F140CF07]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | 同時工程 (1,387) | SD拡散領域とゲート電極への拡散・注入 (182)

Fターム[5F140CF07]に分類される特許

1 - 20 / 182

半導体装置及び半導体装置の製造方法

半導体装置およびその製造方法

半導体装置およびその製造方法

【課題】トンネルトランジスタのトンネルオフリーク電流を低減することが可能な半導体装置を提供する。

【解決手段】実施形態によれば、半導体装置は、基板と、前記基板上にゲート絶縁膜を介して形成されたゲート電極とを備える。さらに、前記装置は、前記基板内に前記ゲート電極を挟むように形成された第1導電型のソース領域、および前記第1導電型とは逆導電型の第2導電型のドレイン領域を備える。さらに、前記ゲート電極は、前記ゲート電極内の前記ソース領域側に形成された前記第1導電型の第1領域と、前記ゲート電極内の前記ドレイン領域側に形成され、前記第1領域に比べて、前記第1導電型の不純物濃度から前記第2導電型の不純物濃度を引いた値が低い第2領域とを有する。

(もっと読む)

半導体装置の製造方法

【課題】特性の良好な半導体装置を製造する。

【解決手段】本発明は、MISFETを有する半導体装置の製造方法であって、(a)半導体基板の上方に、シリコン膜と絶縁膜CPとの積層膜を形成する工程と、(b)積層膜をパターニングすることによりゲート電極GE1とその上部に配置された絶縁膜CPとの積層体を形成する工程と、(c)積層体の側壁にサイドウォール膜SWを形成する工程と、(d)絶縁膜CPを除去する工程と、(e)サイドウォール膜SWおよびゲート電極GE1の合成体の両側の半導体基板中および前記ゲート電極GE1中にヒ素(As)を注入する工程と、を有する。かかる製法によれば、ヒ素(As)のイオン注入によるゲート電極GE1の体積膨張、特に、横方向への膨らみを低減することができ、ゲート電極とコンタクトプラグとの短絡を低減できる。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】高耐圧トランジスタ形成に適した半導体装置の新規な製造方法を提供する。

【解決手段】

半導体装置の製造方法は、シリコン基板に第1導電型第1領域と、第1領域に接する第2導電型第2領域を形成し、ゲート絶縁膜を形成し、第1領域と第2領域とに跨がるゲート電極を形成し、ゲート電極上から第2領域上に延在する絶縁膜を形成し、ゲート電極をマスクとし第2導電型不純物を注入してソース領域およびドレイン領域を形成し、ゲート電極および絶縁膜を覆って金属層を形成し熱処理を行って、ソース領域、ドレイン領域及びゲート電極にシリサイドを形成し、層間絶縁膜にソース領域、ドレイン領域、ゲート電極に達する第1、第2、第3コンタクトホール、及び絶縁膜に達する孔を形成し、第1〜第3コンタクトホール及び孔に導電材料を埋め込み、第1〜第3導電ビアと、孔の内部に配置された導電部材とを形成する。

(もっと読む)

MOSトランジスタおよびその製造方法

【課題】ドレイン端側においてゲート絶縁膜の膜厚を増大させる構成のMOSトランジスタにおいて、オン抵抗を低減し、耐圧を向上させる。

【解決手段】高電圧トランジスタ10のゲート電極構造をチャネル領域CHを第1の膜厚で覆う第1のゲート絶縁膜12G1と、第1の膜厚よりも大きい第2の膜厚で覆う第2のゲート絶縁膜12G2とし、第1のゲート絶縁膜12G1上の第1のゲート電極13G1と、第2のゲート絶縁膜12G2上の第2のゲート電極13G2の構成とする。更に、第1のゲート電極13G1と前記第2のゲート電極13G2とは、前記第1のゲート絶縁膜12G1から延在する絶縁膜12HKで隔てられる。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】ソース領域とドレイン領域間のリーク電流の発生が抑制された、LOCOS分離構造の半導体装置及び半導体装置の製造方法を提供する。

【解決手段】半導体基板の上部の一部に互いに離間して形成された第1導電型のソース領域及びドレイン領域と、ソース領域とドレイン領域に挟まれた領域を含んで半導体基板上に配置されたゲート絶縁膜と、半導体基板上にゲート絶縁膜と連続して配置された、ゲート絶縁膜よりも膜厚の厚いLOCOS絶縁膜と、ゲート絶縁膜上及びゲート絶縁膜周囲のLOCOS絶縁膜上に渡り連続的に配置された多結晶シリコン膜からなるゲート電極とを備え、ゲート電極のチャネル幅方向の端部である周辺領域におけるゲート閾値電圧がゲート電極の中央領域におけるゲート閾値電圧よりも高い。

(もっと読む)

半導体装置及びその製造方法

【課題】ゲートメタル電極とHigh−k膜とを用いた半導体装置において、低抵抗なゲートメタル電極により仕事関数を調整できるようにする。

【解決手段】半導体装置は、Nウェル102の上に形成された第1のゲート絶縁膜109と、該第1のゲート絶縁膜109の上に形成された第1のゲート電極とを備えている。第1のゲート絶縁膜109は、第1の高誘電体膜109bを含み、第1のゲート電極は、第1の高誘電体膜109bの上に形成され、TiN層110aとAlN層110bとが交互に積層された第1の実効仕事関数調整層110を含む。TiN層110aはAlN層110bよりも抵抗が小さく、且つ、AlN層110bはTiN層110aよりも実効仕事関数の調整量が大きい。

(もっと読む)

半導体装置及びその製造方法

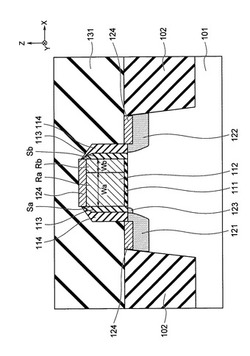

【課題】構造が簡単なトランジスタにより、サステイン耐圧を改善し且つサステイン耐圧のばらつきの抑制及びトランジスタ形成後のドレイン抵抗及び接合プロファイルの調整が可能な、自由度が高い半導体装置を実現できるようにする。

【解決手段】半導体装置は、p型ウェル102に形成され、互いに並行に延びると共に、ゲート長方向の幅が比較的に大きい第1ゲート電極125と、ゲート長方向の幅が比較的に小さい第2ゲート電極126と、p型ウェル102における第1ゲート電極125及び第2ゲート電極126同士の間に形成されたLDD低濃度領域135と、該p型ウェル102における第1ゲート電極125及び第2ゲート電極126のそれぞれの外側に形成されたLDD中濃度領域134とを有している。LDD低濃度領域135の不純物濃度は、LDD中濃度領域134の不純物濃度よりも低い。

(もっと読む)

窒化物上へゲルマニウム・スペーサを選択的に堆積するための構造及び方法

【課題】 窒化物上へゲルマニウム・スペーサを選択的に堆積するための構造及び方法を提供すること。

【解決手段】 半導体製造プロセス中でゲルマニウム構造体を選択的に形成する方法は、化学的酸化物除去(COR)プロセスにおいて自然酸化物を除去し、次いで、加熱された窒化物及び酸化物表面を加熱されたゲルマニウム含有ガスに曝して、ゲルマニウムを選択的に窒化物表面上にだけ形成し、酸化物表面上には形成しない。

(もっと読む)

高誘電率のゲート絶縁膜を有する半導体装置及びそれの製造方法

【課題】本発明はゲート構造物として高誘電率を有する物質として、高誘電率を有する物質からなるゲート絶縁膜を含む半導体装置及びその製造方法に関する。

【解決手段】半導体装置及びその製造方法において、基板上に形成され、ハフニウムシリコン酸化物含有固体物質を含むゲート絶縁膜パターンと前記ゲート絶縁膜パターン上に形成される第1ゲート導電膜パターンを含むゲート構造物及び前記ゲート構造物と隣接する基板の表面部位に配置されており、n型不純物がドーピングされたソース/ドレイン領域を含むことを特徴とする。

(もっと読む)

半導体装置

【課題】導電膜を有する半導体装置は、導電膜の内部応力の影響を受ける。内部応力について検討する。

【解決手段】絶縁表面上に設けられたnチャネル型TFTを有する半導体装置は、半導体膜が引っ張り応力を受けるように、導電膜、例えばゲート電極に不純物元素が導入され、絶縁表面上に設けられたpチャネル型TFTを有する半導体装置は、半導体膜が圧縮応力を受けるように、導電膜、例えばゲート電極に不純物が導入されている。

(もっと読む)

半導体装置およびその製造方法

【課題】オフトラ型ESD保護素子のESD耐量を増加する。

【解決手段】第2導電型ドレイン高濃度拡散層となる領域にトレンチを備え、トレンチ内に第2導電型の多結晶シリコン膜を埋め込むことで、第2導電型ドレイン高濃度拡散層の実効的な体積を増加することを実現する。これより、ゲート電極からドレインコンタクト孔の距離を大きくしたことと同じ効果が得られ、本発明の半導体装置はオフトラ型ESD保護素子として、素子サイズを変更しなくてもESD耐量の増加が可能となる。

(もっと読む)

半導体装置と論理回路およびその製造方法

【課題】インパクトイオン化MISFETに関して、微細素子において二つの入力によりAND型論理素子動作することを可能とし、素子バラツキを低減することを可能とし、消費電力を低減することを可能とする半導体装置を提供する。

【解決手段】第1導電型または真性である半導体領域の表面上に形成された二つの独立した第一および第二のゲート電極への両者への入力により反転層が形成された場合に、インパクトイオン化によるスイッチング動作が可能となることを特徴とする、半導体装置である。

(もっと読む)

半導体集積回路装置の製造方法

【課題】低抵抗で、かつ接合リーク電流の少ないCoシリサイド層を形成することのできるサリサイドプロセスを提供する。

【解決手段】Co純度が99.99%以上で、FeおよびNiの含有量が10ppm以下、より好ましくはCo純度が99.999%の高純度Coターゲットを用いたスパッタリング法によってウエハの主面上に堆積したCo膜をシリサイド化することにより、MOSFETのゲート電極(8n、8p)、ソース、ドレイン(p+型半導体領域13、n+型半導体領域14)の表面に低抵抗で接合リーク電流の少ないCoSi2層(16b)を形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】ゲート電極抵抗の増大や工程数の増加を招くことなく、シリコン混晶層を用いた歪技術により、半導体装置の高性能化を実現する。

【解決手段】半導体基板100における第1のゲート電極106Aから見て第1の絶縁性サイドウォールスペーサ111Aの外側に第1のソースドレイン領域114Aを形成する。その後、半導体基板100における第2のゲート電極106Bから見て第2の絶縁性サイドウォールスペーサ111Bの外側にリセス部119を形成すると共に、第2のゲート電極106Bを部分的に除去する。その後、リセス部109内に、第2のソースドレイン領域114Bとなるシリコン混晶層120を形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】ゲート長が短い微細構造を有しながら、低消費電力でかつ高速動作が可能なMISFETを有する半導体装置を提供する。

【解決手段】シリコン基板と、このシリコン基板上にシリコン含有絶縁膜を介して設けられた高誘電率金属酸化膜を有するゲート絶縁膜と、このゲート絶縁膜上に形成されたシリコン含有ゲート電極とを有し、少なくとも前記高誘電率金属酸化膜の側面側に窒素含有部を有するMIS型電界効果トランジスタを備えた半導体装置。

(もっと読む)

半導体装置およびその製造方法、pチャネルMOSトランジスタ

【課題】nチャネルMOSトランジスタにおいてhigh−Kゲート絶縁膜をhigh−K誘電体膜と酸化ランタン膜の積層により構成した半導体装置において、酸化ランタン膜のパターニングプロセスを不要とする半導体装置の製造方法を提供する。

【解決手段】界面酸化膜22上に形成されたhigh−K誘電体膜23上に酸化膜24を形成する工程と、前記high−K誘電体膜に窒化物層25を形成する工程と、前記窒化物層および前記酸化膜を第1の素子領域21Aから選択的に除去し、第1および第2の素子領域21Bにわたり酸化ランタン膜26を形成し、前記第1の素子領域においては前記界面酸化膜と前記high−K誘電体膜と前記酸化ランタン膜を積層した第1の積層構造を、また前記第2の素子領域においては前記界面酸化膜と前記high−K誘電体膜と前記酸化膜と前記窒化物層と前記酸化ランタン膜を積層した第2の積層構造を形成する工程と、を含む。

(もっと読む)

FinFETとトライゲートデバイス用のラップアラウンド型コンタクト

サブストレートとサブストレートの上に形成された半導体ボディを有する半導体デバイスである。半導体ボディはソース領域とドレイン領域を有している。ソース領域、ドレイン領域、またはその組み合わせは、第一の側面、第二の側面、及び上面を有している。第一の側面は第二の側面と向かい合っており、上面は底面と向かい合っている。ソース領域、ドレイン領域、またはその組み合わせは、実質的に全ての第一の側面の上に、実質的に全ての第二の側面の上に、そして上面の上に、形成されたメタル層を有している。  (もっと読む)

(もっと読む)

半導体製造装置

【課題】内部応力を有する膜を基板の裏面にのみ形成することにより、基板の反り量を抑制し、その際に基板の表面にダメージを与えず、裏面に対する成膜と表面に対するパターン形成とを一貫して行う半導体製造装置を得られるようにする。

【解決手段】基板に薬液を塗布する薬液塗布部102と、基板を加熱する加熱処理部104と、基板の表面にレジストを塗布するレジスト塗布部107と、そのレジストに所定のパターンを露光する露光部105と、そのレジストを現像することにより所定のパターンを得る現像部108とを備えている。薬液塗布部102は、基板を浮遊した状態で、基板を回転させながら基板の裏面にのみ薬液を塗布する薬液塗布手段を有し、加熱処理部104は、基板に熱処理を行うことにより、内部応力を有する応力印加膜を成膜する熱処理手段を有し、裏面に応力印加膜の成膜を行うことと、表面に所定のパターンを形成する処理とを一貫して行う。

(もっと読む)

1 - 20 / 182

[ Back to top ]