Fターム[5F152CC06]の内容

再結晶化技術 (53,633) | 基板 (3,980) | 材料(結晶化直前の状態) (3,902) | 絶縁性金属化合物、サファイア (331)

Fターム[5F152CC06]に分類される特許

1 - 20 / 331

半導体装置の作製方法

【課題】本発明の一態様は、スパッタ法でトランジスタ、ダイオード等の半導体用途に好

適な材料を提供することを課題の一とする。

【解決手段】下地部材上に、第1の酸化物部材を形成し、第1の加熱処理を行って表面か

ら内部に向かって結晶成長し、下地部材に少なくとも一部接する第1の酸化物結晶部材を

形成し、第1の酸化物結晶部材上に第2の酸化物部材を形成し、第2の加熱処理を行って

第1の酸化物結晶部材を種として結晶成長させて第2の酸化物結晶部材を設ける積層酸化

物材料の作製方法である。

(もっと読む)

SOI基板の作製方法

【課題】表面のP−V値が小さく、かつ、高い結晶性を有する半導体薄膜層を備えたSOI基板の作製方法を提供する。

【解決手段】半導体薄膜層の結晶性を高く保つため、水素イオン添加処理中の半導体基板の温度を200℃以下に抑制した。加えて、水素イオン添加処理後の半導体基板を100℃以上400℃以下に保持した状態で半導体基板に対してプラズマ処理を行うことにより、水素イオン添加処理により生じる、半導体薄膜層の分離に対して寄与度の高いSi−H結合を残存させたまま、半導体薄膜層の分離に対して寄与度の低いSi−H結合を低減した。

(もっと読む)

半導体装置の作製方法

【課題】複数のトランジスタが高集積化された素子の少なくとも一のトランジスタに、作製工程数を増加させることなくバックゲートを設ける半導体装置を提供する。

【解決手段】複数のトランジスタが上下に積層されて設けられた素子において、少なくとも上部のトランジスタ102は、半導体特性を示す金属酸化物により設けられ、下部のトランジスタ100が有するゲート電極層を上部のトランジスタのチャネル形成領域と重畳するように配して、ゲート電極層と同一の層の一部を上部のトランジスタ102のバックゲートBGとして機能させる。下部のトランジスタ100は、絶縁層で覆われた状態で平坦化処理が施され、ゲート電極が露出され、上部のトランジスタ102のソース電極及びドレイン電極となる層に接続されている。

(もっと読む)

半導体装置の作製方法

【課題】本発明の一態様は、酸化物半導体を用いたデバイスにおいて高い移動度を達成し

、信頼性の高い表示装置を提供する。

【解決手段】表面と略垂直な方向にc軸が配向する結晶領域を有する酸化物半導体層を形

成し、酸化物半導体層上に接する酸化物絶縁層を形成し、第3の加熱処理を行うことによ

り、酸化物半導体層に酸素を供給し、酸化物絶縁層上に、水素を含む窒化物絶縁層を形成

し、第4の加熱処理を行うことにより、少なくとも酸化物半導体層と酸化物絶縁層の界面

に水素を供給する。

(もっと読む)

半導体装置

【課題】プラスチック支持体を用いた半導体装置を提供する。

【解決手段】プラスチック支持体上に形成されたカラーフィルタと、前記カラーフィルタ

上に形成された接着層と、前記接着層上に形成された絶縁膜と、前記絶縁膜上に形成され

た薄膜トランジスタと、前記薄膜トランジスタ上に形成された発光素子とを有する。また

は、プラスチック支持体と、前記プラスチック支持体に対向する対向基板と、前記プラス

チック支持体と前記対向基板との間に保持された液晶とを有し、前記プラスチック支持体

上に形成されたカラーフィルタと、前記カラーフィルタ上に形成された接着層と、前記接

着層上に形成された絶縁膜と、前記絶縁膜上に形成された薄膜トランジスタとを有する。

(もっと読む)

OLEDデバイスのための電流駆動型配置の提供

【課題】電流型アクティブマトリックスOLEDを改良すること。

【解決手段】電流型アクティブ・マトリックスOLEDデバイスの製造方法は、基板の上方に、半導体層と、導電層と、その半導体層と導電層の間に挟まれた絶縁層を設け;上記半導体層または上記導電層の上方に有機発光ダイオードを画素ごとに設け;第1の電流としてのデータ信号を受け取って対応する画素から出る光の明るさを調節するため、上記半導体層の中に形成されたチャネル領域と、上記導電層の中に形成されたゲートとを備える第1のトランジスタを画素ごとに形成する操作を含んでいる。この方法は、第1の電流に応答して上記有機発光ダイオードの中を流れる電流を調節するため、上記導電層の中に形成されたゲートと、上記半導体層の中に形成されたチャネル領域とを備える第2のトランジスタを画素ごとに形成し;パルス式レーザーを用いて半導体層の特定の領域をアニーリングする操作も含んでいる。

(もっと読む)

半導体装置の作製方法

【課題】酸化物半導体を用いた半導体装置に安定した電気的特性を付与し、高信頼性化する。

【解決手段】酸化物半導体膜を含むトランジスタの作製工程において、非晶質酸化物半導体膜を形成し、該非晶質酸化物半導体膜に酸素を導入して酸素を過剰に含む非晶質酸化物半導体膜を形成する。該非晶質酸化物半導体膜上に酸化アルミニウム膜を形成した後、加熱処理を行い該非晶質酸化物半導体膜の少なくとも一部を結晶化させて、結晶性酸化物半導体膜を形成する。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供する。

【解決手段】ワイドギャップ半導体、例えば酸化物半導体を含むメモリセルを用いて構成された半導体装置であって、メモリセルからの読み出しのために基準電位より低い電位を出力する機能を有する電位切り替え回路を備えた半導体装置とする。ワイドギャップ半導体を用いることで、メモリセルを構成するトランジスタのオフ電流を十分に小さくすることができ、長期間にわたって情報を保持することが可能な半導体装置を提供することができる。

(もっと読む)

半導体装置

【課題】チャネル形成領域の空乏化領域を増やし、電流駆動能力の高い半導体装置を提供する。

【解決手段】島状の半導体領域308と、前記島状の半導体領域308の側面及び上面を覆って設けられたゲート絶縁膜310と、前記ゲート絶縁膜310を介して前記島状の半導体領域308の前記側面及び前記上面を覆って設けられたゲート電極とを有し、前記島状の半導体領域308の前記側面及び前記上面はチャネル形成領域として機能する半導体装置である。

(もっと読む)

半導体装置および半導体装置の駆動方法

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供する。

【解決手段】酸化物半導体を用いた書き込み用トランジスタ162、トランジスタ162と異なる半導体材料を用いた読み出し用トランジスタ160及び容量素子164を含む不揮発性のメモリセルにおいて、メモリセルへの書き込みは、書き込み用トランジスタ162をオン状態とすることにより、書き込み用トランジスタ162のソース電極(またはドレイン電極)と、容量素子164の電極の一方と、読み出し用トランジスタ160のゲート電極とが電気的に接続されたノードに電位を供給した後、書き込み用トランジスタ162をオフ状態とすることにより、ノードに所定量の電荷を保持させることで行う。また、読み出し用トランジスタ160として、pチャネル型トランジスタを用いて、読み出し電位を正の電位とする。

(もっと読む)

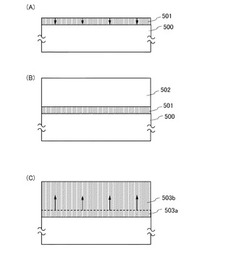

部材の作製方法

【課題】トランジスタなどの半導体素子を有する半導体装置を安価に得ることのできる生

産性の高い作製工程を提供することを課題の一とする。

【解決手段】下地部材上に、酸化物部材を形成し、加熱処理を行って表面から内部に向か

って結晶成長する第1の酸化物結晶部材を形成し、第1の酸化物結晶部材上に第2の酸化

物結晶部材を積層して設ける積層酸化物材料の作製方法である。特に第1の酸化物結晶部

材と第2の酸化物結晶部材がc軸を共通している。ホモ結晶成長またはヘテロ結晶成長の

同軸(アキシャル)成長をさせていることである。

(もっと読む)

酸化物半導体層

【課題】電気特性が良好で信頼性の高いトランジスタ及び当該トランジスタを用いた表示

装置を提供する。

【解決手段】チャネル領域に酸化物半導体を用いたボトムゲート型のトランジスタであっ

て、加熱処理により脱水化または脱水素化された酸化物半導体層を活性層に用い、該活性

層は、微結晶化した表層部の第1の領域と、その他の部分の第2の領域で形成されている

。この様な構成をした酸化物半導体層を用いることにより、表層部からの水分の再侵入や

酸素の脱離によるn型化や寄生チャネル発生の抑制、及びソース電極及びドレイン電極と

の接触抵抗を下げることができる。

(もっと読む)

半導体装置の作製方法

【課題】酸化物半導体を用いた半導体装置に安定した電気的特性を付与し、高信頼性化す

ることを目的の一とする。

【解決手段】酸化物半導体膜を有するボトムゲート構造のトランジスタの作製工程におい

て、熱処理による脱水化または脱水素化処理、及び酸素ドープ処理を行う。酸素ドープ処

理されたゲート絶縁膜、熱処理による脱水化または脱水素化処理された酸化物半導体膜を

有するトランジスタは、バイアス−熱ストレス試験(BT試験)前後においてもトランジ

スタのしきい値電圧の変化量が低減できており、信頼性の高いトランジスタとすることが

できる。

(もっと読む)

半導体装置

【課題】新たな構造の酸化物半導体層を用いた新たな構造の半導体装置を提供することを

目的の一とする。

【解決手段】絶縁表面を有する基板上の、第1の酸化物半導体層の表面から内部に向かっ

て成長させた結晶領域を有する第1の酸化物半導体層と、第1の酸化物半導体層上の第2

の酸化物半導体層と、第2の酸化物半導体層と接するソース電極層およびドレイン電極層

と、第2の酸化物半導体層、ソース電極層、およびドレイン電極層を覆うゲート絶縁層と

、ゲート絶縁層上の、第2の酸化物半導体層と重畳する領域のゲート電極層と、を有し、

第2の酸化物半導体層は、結晶領域から成長させた結晶を有する層である半導体装置であ

る。

(もっと読む)

部材の作製方法

【課題】本発明の一態様は、スパッタ法でトランジスタ、ダイオード等の半導体用途に好

適な材料を提供することを課題の一とする。

【解決手段】下地部材上に、第1の酸化物部材を形成し、第1の加熱処理を行って表面か

ら内部に向かって結晶成長し、下地部材に少なくとも一部接する第1の酸化物結晶部材を

形成し、第1の酸化物結晶部材上に第2の酸化物部材を形成し、第2の加熱処理を行って

第1の酸化物結晶部材を種として結晶成長させて第2の酸化物結晶部材を設ける積層酸化

物材料の作製方法である。

(もっと読む)

半導体装置、及び半導体装置の作製方法

【課題】微細化及び高集積化を達成した酸化物半導体を用いた半導体装置、及び半導体装置の作製工程において、安定した電気的特性を付与し、高信頼性化する。また、上記半導体装置の作製工程において、不良を抑制し、歩留まりよく作製する技術を提供する。

【解決手段】酸化物半導体層を含むトランジスタを有する半導体装置において、酸化物半導体膜を、絶縁層に設けられたトレンチに設ける。トレンチは下端コーナ部及び曲率半径が20nm以上60nm以下の曲面状の上端コーナ部を含み、酸化物半導体膜は、トレンチの底面、下端コーナ部、上端コーナ部、及び内壁面に接して設けられる。酸化物半導体膜は、少なくとも上端コーナ部において表面に概略垂直なc軸を有している結晶を含む酸化物半導体膜である。

(もっと読む)

酸化物半導体膜の形成方法および半導体装置の作製方法

【課題】良好な半導体特性を有する酸化物半導体膜の形成方法を提供する。さらに、該酸化物半導体膜を適用し、良好な電気特性を有する半導体装置の作製方法を提供する。

【解決手段】酸化物半導体膜を形成し、酸化物半導体膜上に接して設けられた水素透過膜を形成し、水素透過膜上に接して設けられた水素捕縛膜を形成し、加熱処理を行うことで、前記酸化物半導体膜から水素を脱離させる酸化物半導体膜の形成方法である。また、該形成方法を用いて作製する半導体装置の作製方法である。

(もっと読む)

化合物半導体薄膜の製造方法

【課題】 高温中で緻密化を図りつつ、下部電極や金属基板が過剰にVI族化されることを抑制し、且つVI族欠陥の少ない高品質なIB−IIIA−VIA族系化合物半導体薄膜を製造することができる化合物半導体薄膜の製造方法を提供する。

【解決手段】薄膜物質を形成する薄膜形成工程(S12)と、IB族−IIIA族金属間化合物を含む薄膜を形成する予備熱処理工程(S13)と、VI族物質を含む雰囲気中でIB族−IIIA族金属間化合物を含む薄膜を加熱し、CuxA(AはS、Seから選択される少なくとも一種、0.5≦x≦1)相を備える中間体を形成する第一熱処理工程(S14)と、VI族物質がない雰囲気下またはVI族濃度が薄い雰囲気下で中間体を熱処理する第二熱処理工程(S15)と、VI族物質を含む雰囲気中又はVI族濃度が濃い雰囲気中で、IB−IIIA−VIA族系化合物半導体を熱処理する第三熱処理工程(S16)とを含む。

(もっと読む)

SOI基板、およびSOI基板の作製方法

【課題】単結晶シリコン膜などの半導体膜が、支持基板から剥がれることを防止するSOI基板の作製方法を提供する。また、当該方法を用いることで、SOI基板作製における歩留まりを向上させ、生産コストを削減する。

【解決手段】半導体基板に絶縁膜を形成し、加速されたイオンを半導体基板に照射することにより、半導体基板中に脆化領域を形成し、半導体基板と支持基板とを、絶縁膜を介して貼り合わせ、脆化領域において、半導体基板を分離して、支持基板上に絶縁膜を介して半導体膜を形成し、半導体膜上にマスクを形成し、半導体膜の一部及び絶縁膜の一部をエッチングすることにより、半導体膜の周端部が、絶縁膜の周端部の内側に位置するように、半導体膜及び絶縁膜を形成する、SOI基板の作製方法である。

(もっと読む)

半導体装置の作製方法

【課題】側壁スペーサを形成することなく、且つ、工程数を増やすことなく、自己整合的にLDD領域を少なくとも一つ備えたTFTを提供する。また、同一基板上に、工程数を増やすことなく、様々なTFT、例えば、チャネル形成領域の片側にLDD領域を有するTFTと、チャネル形成領域の両側にLDD領域を有するTFTとを形成する作製方法を提供する。

【解決手段】回折格子パターン或いは半透膜からなる光強度低減機能を有する補助パターンを設置したフォトマスクまたはレチクルをゲート電極形成用のフォトリソグラフィ工程に適用して膜厚の厚い領域と、該領域より膜厚の薄い領域を片側側部に有する非対称のレジストパターンを形成し、段差を有するゲート電極を形成し、ゲート電極の膜厚の薄い領域を通過させて前記半導体層に不純物元素を注入して、自己整合的にLDD領域を形成する。

(もっと読む)

1 - 20 / 331

[ Back to top ]