Fターム[5F152LL03]の内容

再結晶化技術 (53,633) | 半導体膜成長技術(半導体層) (1,668) | 成長技術 (1,654) | 気相 (1,473) | CVD、VPE (918)

Fターム[5F152LL03]の下位に属するFターム

プラズマCVD (98)

MOCVD、MOVPE (333)

Fターム[5F152LL03]に分類される特許

1 - 20 / 487

赤色発光半導体素子とその製造方法

半導体発光素子、半導体発光素子の製造方法および発光装置

半導体加工用部品の処理方法およびそれにより形成された部品

III族窒化物複合基板の製造方法

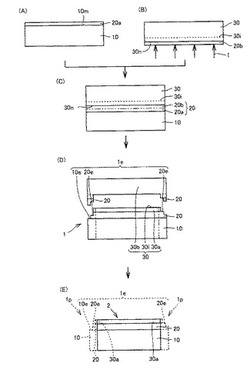

【課題】支持基板とIII族窒化物層との接合が良好なIII族窒化物複合基板の製造方法を提供する。

【解決手段】本III族窒化物複合基板の製造方法は、目標とする基板径より大きい径の主面10mを有する支持基板10と、目標とする基板径より大きい径の主面30nを有しその主面30nから所定の深さの位置にイオン注入領域30iが形成されたIII族窒化物基板30とを、中間層20を介在させて貼り合わせ、III族窒化物基板30をイオン注入領域30iにおいてIII族窒化物層30aと残りのIII族窒化物基板30bとに分離することにより、支持基板10上に中間層20を介在させてIII族窒化物層30aが接合された第1のIII族窒化物複合基板1を形成し、第1のIII族窒化物複合基板1の外周部を除去することにより目標とする基板径に等しい径の主面を有する第2のIII族窒化物複合基板2を得る。

(もっと読む)

シリコン単結晶膜およびその製造方法

【課題】薄層化された自立性のシリコン単結晶膜を提供し、また、剥離時の熱処理温度を格段に低減することができる新たなシリコン単結晶膜の形成方法を提供する。

【解決手段】シリコン単結晶膜6は、Siの含有率が、90原子%以上であり、厚みが、50μm以下であり、自立性がある。

(もっと読む)

半導体ウェハ

【課題】高い結晶品質を有する、多様な材料からなる、完全に緩和した、又は歪んだ半導体層を積層するために絶縁体層の格子寸法を調整するための高い柔軟性を許容する、SOI構造の作製のための基板を提供する。

【解決手段】実質的にシリコンからなる単結晶基板ウェハ1、電気絶縁性材料を含み、かつ2nm〜100nmの厚さを有する第一非晶質中間層2、立方晶系Ia−3結晶構造と、(Me12O3)-1-x(Me22O3)xの組成と、基板ウェハの材料の格子定数と0%〜5%異なる格子定数とを有する単結晶第一酸化物層3を示される順序で含むことを特徴とする半導体ウェハ。

(もっと読む)

グラフェン構造の製造方法及びこれを用いた半導体装置の製造方法

【課題】所望の位置にグラフェン膜を有するグラフェン構造及びこれを用いた半導体装置を提供する。

【解決手段】所定の基材3上において、炭素含有層4と、少なくともケイ素を含む炭素化合物層5とを順次に積層し、その上に絶縁膜層6を形成した後、絶縁膜層の一部をエッチングにより取り除いた基板に対してアニーリングを実施し、絶縁膜の除去部にのみグラフェン膜7を形成したグラフェン構造1を形成し、これを用いて表面にショットキー電極8、およびオーミック電極9,10を形成させて半導体装置2を作製する。

(もっと読む)

電界効果トランジスタの製造方法および電界効果トランジスタ

【課題】ドーピング密度を増やすことなく、高濃度キャリア走行部を形成でき、高い移動度と低いオン抵抗を実現できる電界効果トランジスタの製造方法および電界効果トランジスタを提供する。

【解決手段】この電界効果トランジスタ1は、窒素ドープn型SiCドリフト層12のキャリア走行部14を挟むように形成されたソース13とドレイン15とを備える。ソース13とドレイン15は、エッチングによってキャリア走行部14に隣接して形成された段部16,17を有する。キャリア走行部14は、段部16,17の段差面16A,17Aに紫外光を照射することによって段部16,17から延びるように形成された積層欠陥部18を有する。積層欠陥部18は、3C‐SiCの結晶構造を持ち、量子井戸構造のようにふるまうことからキャリアがここに多数閉じ込められる。

(もっと読む)

装置の作製方法

【課題】剥離前の形状及び特性を保った良好な状態で転置工程を行えるような、剥離工程

を用いて半導体装置及び表示装置を作製できる技術を提供する。よって、より高信頼性の

半導体装置及び表示装置を装置や工程を複雑化することなく、歩留まりよく作製できる技

術を提供することも目的とする。

【解決手段】透光性を有する第1の基板上に光触媒物質を有する有機化合物層を形成し、

光触媒物質を有する有機化合物層上に素子層を形成し、光を第1の基板を通過させて、光

触媒物質を有する有機化合物層に照射し、素子層を前記第1の基板より剥離する。

(もっと読む)

III族窒化物複合基板

【課題】支持基板と酸化物膜との接合強度および酸化物膜とIII族窒化物層との接合強度が高いIII族窒化物複合基板を提供する。

【解決手段】本III族窒化物複合基板1は、支持基板10と酸化物膜20とIII族窒化物層30aとを含み、支持基板10は多結晶で形成され、III族窒化物層30aは少なくともc軸方向に配向しているIII族窒化物結晶で形成され、酸化物膜20は不純物が添加され、不純物の濃度は、酸化物膜20において支持基板10側の第1主面20sからIII族窒化物層30a側の第2主面20tにかけて膜厚方向で変化し、第1主面20sにおける不純物の濃度は第2主面20tにおける不純物の濃度よりも高い。

(もっと読む)

窒化物半導体ウェーハ、窒化物半導体装置及び窒化物半導体結晶の成長方法

【課題】シリコン基板上に形成した、転位及びクラックの少ない窒化物半導体ウェーハ、窒化物半導体装置及び窒化物半導体結晶の成長方法を提供する。

【解決手段】実施形態によれば、シリコン基板と、その上に順次設けられた、下側歪緩和層、中間層、上側歪緩和層及び機能層と、を有する窒化物半導体ウェーハが提供される。中間層は、第1下側層と、第1ドープ層と、第1上側層と、を含む。第1下側層は、下側歪緩和層の上に設けられ下側歪緩和層の格子定数よりも大きい格子定数を有する。第1ドープ層は、第1下側層の上に設けられ第1下側層の格子定数以上の格子定数を有し1×1018cm−3以上1×1021cm−3未満の濃度であり第1下側層よりも高い濃度で不純物を含有する。第1上側層は、第1ドープ層の上に設けられ第1ドープ層の格子定数以上で第1下側層の格子定数よりも大きい格子定数を有する。

(もっと読む)

半導体装置の製造方法

【課題】結晶性の優れた炭化シリコン膜を形成することができる炭化シリコンからなる半導体装置の製造方法を提供する。

【解決手段】基板1上に、絶縁膜2を介してシリコン膜3が形成された半導体基板を用意し、炭化シリコン膜6形成予定領域を選択的に被覆するマスク膜5を形成する。このマスク膜5で被覆されない領域のシリコン膜3を酸化し、酸化シリコン膜4を形成する。マスク膜5を除去し、シリコン膜3を露出させ、露出したシリコン膜3を炭化し、炭化シリコン膜6を形成する。その後、炭化シリコン膜6上に炭化シリコンのエピタキシャル成長膜8を形成する。

(もっと読む)

複合基板の製造方法および複合基板

【課題】結晶成長用基板に形成した半導体結晶層を転写先基板に転写する場合の犠牲層のエッチング速度を高める。

【解決手段】半導体結晶層形成基板の上に犠牲層および半導体結晶層を順に形成し、転写先基板に接することとなる前記半導体結晶層形成基板の第1表面と、前記第1表面に接することとなる前記転写先基板の第2表面と、が向かい合うように、前記半導体結晶層形成基板と前記転写先基板とを貼り合わせ、前記半導体結晶層形成基板および前記転写先基板の全部または一部をエッチング液に浸漬して前記犠牲層をエッチングし、前記半導体結晶層を前記転写先基板側に残した状態で、前記転写先基板と前記半導体結晶層形成基板とを分離する。ここで、前記転写先基板が、非可撓性基板と有機物層とを有し、前記有機物層の表面が、前記第2表面であるものとする。

(もっと読む)

SiCエピタキシャルウエハおよびそれを用いたSiC半導体素子

【課題】高品質かつ高信頼性の素子を作製できるSiCエピタキシャルウエハ、およびそれを用いて得られるSiC半導体素子を提供すること

【解決手段】4°以下のオフ角を有するSiC基板2と、SiC基板2の主面4に形成され、その表面10に0.5nm以上の高さのステップバンチング9が形成されたSiCエピタキシャル層3とを含むSiCエピタキシャルウエハ1において、ステップバンチング9の線密度を40cm−1以下にする。

(もっと読む)

β−Ga2O3系単結晶膜の製造方法

【課題】ホモエピタキシャル成長法を用いて伝導特性に優れたβ−Ga2O3単結晶膜を形成することができるβ−Ga2O3単結晶膜の製造方法を提供する。

【解決手段】分子線エピタキシー法により、Snを添加しながらβ−Ga2O3結晶をβ−Ga2O3基板2上、又は前記β−Ga2O3基板上に形成されたβ−Ga2O3系結晶層上にホモエピタキシャル成長させ、Sn添加β−Ga2O3結晶膜を形成する工程と、第1の不活性雰囲気中で前記Sn添加β−Ga2O3結晶膜に第1のアニール処理を施す工程とを含む方法により、Sn添加β−Ga2O3単結晶膜を製造する。

(もっと読む)

半導体装置及びその製造方法

【課題】SOI構造のフラッシュメモリーの提供

【解決手段】

半導体基板1上にシリコン窒化膜2及びシリコン酸化膜3が選択的に設けられ、シリコン酸化膜3上には、選択的に横(水平)方向エピタキシャルSi層5が設けられ、Si層5の両側面には、それぞれ側面を接して横(水平)方向エピタキシャルSi層6が設けられた構造からなる半導体層が素子分離領域のシリコン窒化膜4により絶縁分離されている。Si層6の残りの周囲には第1のゲート酸化膜10を介して包囲型フローティングゲート電極11が設けられ、包囲型フローティングゲート電極11の周囲には第2のゲート酸化膜12を介して包囲型コントロールゲート電極13(ワード線)が設けられ、Si層5には概略ソースドレイン領域9が設けられている2重包囲型ゲート電極を有するMIS電界効果トランジスタより構成したフラッシュメモリー。

(もっと読む)

単結晶炭化シリコン膜の製造方法及び単結晶炭化シリコン膜付き基板の製造方法

【課題】結晶欠陥の少ない高品質なエピタキシャル膜を得ることが可能な単結晶炭化シリコン膜の製造方法及び単結晶炭化シリコン膜付き基板の製造方法を提供する。

【解決手段】シリコン基板11上に単結晶炭化シリコン膜14を形成する単結晶炭化シリコン膜14の製造方法であって、シリコン基板11の表面に炭化シリコン膜12を形成する第1の工程と、炭化シリコン膜12の表面にマスク材13を形成する第2の工程と、マスク材13に開口部13hを形成し、炭化シリコン膜12の一部を露出させる第3の工程と、原料ガスを含むガス雰囲気中でシリコン基板11を加熱し、炭化シリコン膜12を基点として単結晶炭化シリコンをエピタキシャル成長させ、炭化シリコン膜12及びマスク材13を覆う単結晶炭化シリコン膜14を形成する第4の工程と、を含み、原料ガスを含むガス雰囲気の圧力は、5.0×10−4Pa以上かつ0.5Pa以下である。

(もっと読む)

複合基板およびその製造方法、ならびに複合ウエハ

【課題】III族窒化物とは化学組成の異なる異組成基板とIII族窒化物層とが貼り合わされた複合基板であっても、反りおよびクラックを発生させることなくその複合基板上にIII族窒化物エピタキシャル層を形成することができる複合基板およびその製造方法を提供する。

【解決手段】本複合基板2Dは、III族窒化物以外の化学組成を有する異組成基板10と、異組成基板10に貼り合わされたIII族窒化物層21と、含み、III族窒化物層21は、平面充填が可能な少なくとも1種類の平面形状を有する複数のIII族窒化物タイル21pに分離している。

(もっと読む)

窒化物半導体エピタキシャル基板及び窒化物半導体デバイス

【課題】低転位であり、クラック発生を抑制できるIII族窒化物半導体層を有する窒化物

半導体エピタキシャル基板及び窒化物半導体デバイスを提供する。

【解決手段】基板上にAlを含むIII族窒化物半導体のバッファ層を介して成長した、C

面を表面とするIII族窒化物半導体層を有する窒化物半導体エピタキシャル基板であって

、前記バッファ層が、その表面にインバージョンドメインを有する。

(もっと読む)

半導体デバイス、半導体基板、半導体基板の製造方法および半導体デバイスの製造方法

【課題】単一基板上にソース・ドレインを同一工程で同時形成したIII−V族半導体のnMISFETおよびIV族半導体のpMISFETのソース・ドレイン領域抵抗または接触抵抗を小さくする。

【解決手段】第1半導体結晶層に形成された第1チャネル型の第1MISFETの第1ソースおよび第1ドレインと、第2半導体結晶層に形成された第2チャネル型の第2MISFETの第2ソースおよび第2ドレインが、同一の導電性物質からなり、当該導電性物質の仕事関数ΦMが、数1および数2の少なくとも一方の関係を満たす。

(数1) φ1<ΦM<φ2+Eg2

(数2) |ΦM−φ1|≦0.1eV、かつ、|(φ2+Eg2)−ΦM|≦0.1eV

ただし、φ1は、N型半導体結晶層の電子親和力、φ2およびEg2は、P型半導体結晶層の電子親和力および禁制帯幅。

(もっと読む)

1 - 20 / 487

[ Back to top ]