Fターム[5F152LM08]の内容

再結晶化技術 (53,633) | 一般エピタキシャル成長技術 (652) | 成長技術 (97)

Fターム[5F152LM08]に分類される特許

1 - 20 / 97

赤色発光半導体素子とその製造方法

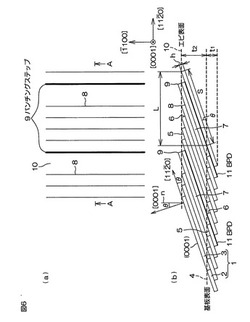

SiCエピタキシャルウエハおよびそれを用いたSiC半導体素子

【課題】高品質かつ高信頼性の素子を作製できるSiCエピタキシャルウエハ、およびそれを用いて得られるSiC半導体素子を提供すること

【解決手段】4°以下のオフ角を有するSiC基板2と、SiC基板2の主面4に形成され、その表面10に0.5nm以上の高さのステップバンチング9が形成されたSiCエピタキシャル層3とを含むSiCエピタキシャルウエハ1において、ステップバンチング9の線密度を40cm−1以下にする。

(もっと読む)

半導体膜蒸着装置および半導体膜蒸着方法

【課題】半導体膜の表面欠陥の発生を抑制する半導体膜蒸着装置および半導体膜蒸着方法を提供する。

【解決手段】

半導体原料を収容するるつぼ2と、るつぼ2と対向して基板5を支持する基板支持器6と、るつぼ2と基板5との間でるつぼ2の開口を覆って配置されるマスク4と、るつぼ2およびマスク4を加熱する加熱器3と、るつぼ2、基板支持器6、およびマスク4を収容する真空チャンバ7とを備える半導体膜蒸着装置。るつぼ2から飛散した半導体分子はマスク4内部を衝突しながら通過することで基板5上に表面欠陥が抑制された状態で成膜される。

(もっと読む)

発光素子用エピタキシャルウェハ及び発光素子

【課題】1枚のウェハからより多くのチップを取得することができる高性能な発光素子用エピタキシャルウェハを提供する。

【解決手段】加熱したn型基板100上にIII族原料ガス及びV族原料ガスを供給し、n型基板100上に少なくともn型クラッド層5、活性層7、p型クラッド層9,11及びコンタクト層13からなるIII−V族半導体層2を積層する発光素子用エピタキシャルウェハ1において、III−V族半導体層2のいずれかの層に不可避不純物として混入するS(硫黄)の濃度を1.0×1015cm-3以下にすべく、その層の成長時の基板温度を620℃以上とし、かつV族原料ガスとIII族原料ガスの実流量比を130以上とした。

(もっと読む)

炭化珪素半導体装置の製造方法

【課題】チャネル移動度の低下を抑制しつつ閾値電圧を制御する炭化珪素半導体装置の製造方法の提供を目的とする。

【解決手段】本発明の炭化珪素半導体装置の製造方法は、(b)二酸化珪素膜が形成された炭化珪素基板を窒化処理する工程と、(c)窒化処理された炭化珪素基板を水蒸気を含んだ酸素雰囲気で熱処理する工程とを備える。工程(c)は、(c1)窒化処理された炭化珪素基板を投入した熱処理炉の温度を不活性ガス雰囲気中で昇温又は降温する工程を含む。工程(c1)は、窒化処理直後のチャネル移動度をμch、昇温又は降温開始時刻をt=0、熱処理開始時刻をt=t1、熱処理終了時刻をt=t2、熱処理炉からの基板取出時刻をt=t3、ボルツマン定数をk、時刻tにおける熱処理炉の温度をT(K)とした場合に、式(1)により求められる炭化珪素基板中のチャネル移動度の低下率が10%以下となるように昇温速度及び/又は降温速度を決定する。

(もっと読む)

結晶性薄膜又は結晶性構造体の製造方法、及び結晶性構造体

【課題】シンプルな製造工程により界面状態の良好な結晶性薄膜を立体形状を含む所望のパターンに形成可能であり、結晶化に要する熱処理温度を低減させることが可能な結晶性薄膜又は結晶性構造体の製造方法、及び当該製造方法により形成された結晶性薄膜を備えた構造体を提供する。

【解決手段】結晶性薄膜又は結晶性構造体の製造方法においては、蒸着・結晶化促進工程において、スパッタリング法による金属酸化物の蒸着、及びレーザー光照射による金属酸化物の結晶化促進が同時に行われる。蒸着・結晶化促進工程を経た基板34は、所定の温度条件下においてアニールされる。これにより、金属酸化物が完全に結晶化された状態になる。

(もっと読む)

表面を改善する方法

【課題】本発明は、少なくとも部分的にシリコンを含む、半導体基板の表面を改善する方法に関する。本発明の目的は、少なくとも部分的にシリコンからなる半導体基板の表面を改善する方法であって、高い表面品質を有する半導体基板が提供されるよう、半導体基板の内部または表面にある欠陥を完全に修復することができる方法を提供することである。

【解決手段】この目的は、前記半導体基板の表面にある少なくとも1つのホール内での選択的エピタキシャル堆積を含んだ堆積ステップを含む、上述のタイプの方法によって解決される。

(もっと読む)

半導体装置およびその作製方法

【課題】酸化物半導体膜を用いた半導体装置に安定した電気的特性を付与し、信頼性の高い半導体装置を作製することを課題の一とする。

【解決手段】絶縁表面上に膜厚が1nm以上10nm以下の第1の材料膜(六方晶の結晶構造を有する膜)を形成し、第1の材料膜を核として、六方晶の結晶構造を有する第2の材料膜(結晶性酸化物半導体膜)を形成し、第1の材料膜と第2の材料膜の積層を形成する。第1の材料膜としては、ウルツ鉱型結晶構造を有する材料膜(例えば窒化ガリウム、或いは窒化アルミニウム)、或いはコランダム型結晶構造を有する材料膜(α−Al2O3、α−Ga2O3、In2O3、Ti2O3、V2O3、Cr2O3、或いはα−Fe2O3)を用いる。

(もっと読む)

単結晶半導体膜の作製方法、電極の作製方法

【課題】簡単かつコストの低い方法で単結晶半導体膜を得る方法を提供する。

【解決手段】単結晶半導体基板10の表面に、気相エピタキシャル成長法によって圧縮応力を有する単結晶半導体膜11を形成し、単結晶半導体膜11の表面に、引張応力を有する膜(例えば、熱硬化性樹脂膜12)を形成し、単結晶半導体膜11に力を加える剥離工程によって、単結晶半導体基板10と単結晶半導体膜11とを分離して、単結晶半導体膜を得る。なお、熱硬化性樹脂膜12としては、例えば、エポキシ樹脂膜を用いることが可能である。

(もっと読む)

半導体装置の製造方法

【課題】解像度限界より小さい寸法のパターンを規則的に形成する半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法は、構造体としての第1及び第2のパターン13a、13b間に露出する種結晶としての半導体基板10からエピタキシャル結晶としての単結晶膜14を形成し、単結晶膜14を単結晶膜14の融点以下の温度で加熱することにより単結晶膜14を流動させ、流動した単結晶膜14が凝集することにより複数の凝集体15を第1及び第2のパターン13a、13b間に形成することを含む。

(もっと読む)

フィン型FETを有する半導体装置およびその製造方法

【課題】横方向延伸を減少し、素子サイズを小さくすることができる半導体装置を提供する。

【解決手段】半導体基板上に延伸し、STI領域を間に有する第1および第2のフィンを形成する。STI領域の上面と第1および第2のフィンの上面の間の寸法を第1の高さとし、STI領域の第1と第2のフィンとの間の間隙内に誘電材料を堆積し、STI領域の上面上に上面を有して、誘電材料の上面と第1および第2のフィンの上面との寸法を第2の高さとし、第2の高さは、第1の高さより低くなるように誘電材料を堆積した後、第1および第2のフィン上でそれぞれ誘電体の上方に、第1および第2のフィン延伸をエピタキシャル成長で形成する。

(もっと読む)

半導体基板の製造方法および半導体デバイスの製造方法

【課題】シリコンデバイス等耐熱性の低い部位がSi基板に設けられた場合でも、Ge結晶に熱アニールを施し、十分な結晶品質のGe結晶薄膜を得る。

【解決手段】表面がSiであるベース基板と、前記ベース基板の上に形成され、組成がCxSiyGezSn1−x−y―z(0≦x<1、0≦y<1、0<z≦1、かつ、0<x+y+z≦1)である第1結晶層と、前記第1結晶層が形成された部分以外の前記ベース基板の上に形成された第1半導体素子と、を有する半導体基板の製造方法であって、前記第1半導体素子には電磁波を照射することがなく、前記第1結晶層の一部または全部に電磁波を照射する工程を有する半導体基板の製造方法を提供する。

(もっと読む)

半導体基板の製造方法

【課題】大型であって、かつ半導体装置を高い歩留りで製造することができる半導体基板の製造方法を提供する。

【解決手段】第1の炭化珪素基板11の第1の側面S1と、第2の炭化珪素基板12の側面S2とが互いに面するように、処理室60内にベース部30および第1および第2の炭化珪素基板11、12が配置される。処理室60内に、炭素元素と化合することができる固体材料からなる吸収部51が設けられる。第1および第2の側面S1、S2を互いに接合するために、炭化珪素が昇華し得る温度以上に処理室60内の温度が高められる。温度を高める工程において吸収部51が炭化される。

(もっと読む)

結晶シリコンの少なくとも一つの極薄層を含む多層膜を製造する方法及び前記方法により得られたデバイス

【課題】 結晶シリコンの少なくとも一つの極薄層を含む多層膜を製作する、単純で負担がより少ない方法を提案すること。

【解決手段】 本発明は結晶シリコンの少なくとも一つの極薄層を有する多層膜を製作する方法に関し、前記膜は、結晶構造を有し、予め洗浄された表面を含む基板から製作される。本発明によれば、前記方法は前記洗浄された表面をSiF4、水素、及びアルゴンのガス混合物内で生成されたRFプラズマに当て、それにより前記基板に接触して微小空洞を含有する界面副層を備える結晶シリコンの極薄層を形成するステップa)と、結晶シリコンの前記極薄層上に少なくとも1層の材料を堆積させ、それにより少なくとも一つの機械的に強い層を含む多層膜を形成するステップb)と、前記多層膜で覆われた前記基板を400℃より高い温度でアニールし、それにより前記多層膜を前記基板から分離させるステップc)とを含む。

(もっと読む)

微結晶半導体膜の作製方法、及び半導体装置の作製方法

【課題】結晶粒間に鬆がない緻密な結晶性半導体膜(例えば微結晶半導体膜)を作製する技術を提供することを目的とする。

【解決手段】プラズマCVD装置の反応室内における反応ガスの圧力を450Pa〜13332Paとし、当該プラズマCVD装置の第1の電極と第2の電極の間隔を1mm〜20mm、好ましくは4mm以上16mm以下として、前記第1の電極に60MHz以下の高周波電力を供給することにより、第1の電極および第2の電極の間にプラズマ領域を形成し、プラズマ領域を含む気相中において、結晶性を有する半導体でなる堆積前駆体を形成し、堆積前駆体を堆積させることにより、5nm以上15nm以下の結晶核を形成し、結晶核から結晶成長させることにより微結晶半導体膜を形成する。

(もっと読む)

センサ、半導体基板、および半導体基板の製造方法

【課題】効率よく光電変換ができる光吸収体を有する半導体基板、半導体基板の製造方法、および当該半導体基板を含む光センサを提供する。

【解決手段】シリコンを含むベース基板と、ベース基板上方に設けられたシード体と、シード体に格子整合または擬格子整合し、光または熱を吸収してキャリアを生成する3−5族化合物半導体からなる光熱吸収体とを備え、光熱吸収体が、光熱吸収体に入射する入射光または光熱吸収体に加わる熱に応じて電気信号を出力するセンサを提供する。また、シリコンを含むベース基板と、ベース基板の上方に形成され、ベース基板の表面を露出する開口を有し、結晶成長を阻害する阻害体と、開口の内部に設けられたシード体と、シード体に格子整合または擬格子整合し、光または熱を吸収してキャリアを生成する3−5族化合物半導体からなる光熱吸収体とを備える半導体基板を提供する。

(もっと読む)

光デバイス、半導体基板、光デバイスの製造方法、および半導体基板の製造方法

【課題】高品質な光デバイスをシリコン基板上にモノリシックに形成する。

【解決手段】シリコンを含むベース基板と、ベース基板上に設けられた複数のシード結晶と、複数のシード結晶に格子整合または擬格子整合する複数の3−5族化合物半導体とを備え、複数の3−5族化合物半導体のうちの少なくとも1つに、供給される駆動電流に応じて光を出力する発光半導体、または光の照射を受けて光電流を発生する受光半導体を含む光電半導体が形成されており、複数の3−5族化合物半導体のうち、光電半導体を有する3−5族化合物半導体以外の少なくとも1つの3−5族化合物半導体にヘテロ接合トランジスタが形成されている光デバイスを提供する。

(もっと読む)

半導体基板、電子デバイス、半導体基板の製造方法及び電子デバイスの製造方法

【課題】半導体基板、電子デバイス、半導体基板の製造方法及び電子デバイスの製造方法を提供する。

【解決手段】シリコンに不純物原子が導入された不純物領域104を有するベース基板102と、不純物領域104に接して設けられている複数のシード体112と、複数のシード体112の各々に接して設けられ、複数のシード体112の各々とそれぞれ格子整合または擬格子整合する複数の化合物半導体114とを備える半導体基板100。当該半導体基板100は、ベース基板102上に設けられ、不純物領域104の少なくとも一部を露出する複数の開口が設けられた阻害体をさらに備えてもよい。

(もっと読む)

ナノ/微小球リソグラフィによって製造されるナノ/マイクロワイヤ太陽電池

【課題】 ナノ/微小球リソグラフィによって製造されるナノ/マイクロワイヤ太陽電池を提供する。

【解決手段】 ナノワイヤ/マイクロワイヤ・ベースの太陽電池を製造する技術が提供される。一実施形態において、太陽電池を製造する方法が提供される。本方法は、以下のステップを含む。ドープ基板を準備する。基板の上に球の単層を堆積させる。球は、ナノ球、微小球、又はそれらの組み合わせを含む。球をトリミングして単層内の個々の球の間に空間を設ける。トリミングされた球をマスクとして用いて、基板内にワイヤをパターン形成する。ワイヤは、ナノワイヤ、マイクロワイヤ、又はそれらの組み合わせを含む。ドープ・エミッタ層をパターン形成されたワイヤ上に形成する。上部コンタクト電極をエミッタ層の上に堆積させる。底部コンタクト電極を基板のワイヤとは反対の側に堆積させる。

(もっと読む)

炭化シリコン膜の製造方法

【課題】緻密で均一な膜厚であり、しかも所望の膜厚の炭化シリコン膜を得ることができ、かつ低コストや大口径化が可能な炭化シリコン膜の製造方法を提供する。

【解決手段】本発明の炭化シリコン膜13の製造方法は、基板11上にアモルファスシリコンとポリシリコンとの少なくとも一方を含むシリコン膜14を形成する工程と、シリコン膜14を炭化処理し、炭化された膜を含んだ炭化シリコン膜13を形成する工程と、を有することを特徴とする。

(もっと読む)

1 - 20 / 97

[ Back to top ]