Fターム[5F152LN02]の内容

再結晶化技術 (53,633) | 格子整合、格子不整合技術 (1,553) | 目的 (706) | 歪みによる悪影響防止 (524)

Fターム[5F152LN02]の下位に属するFターム

転位、クラック等の低減又は抑制 (334)

凹凸の低減 (54)

反りの低減 (63)

Fターム[5F152LN02]に分類される特許

1 - 20 / 73

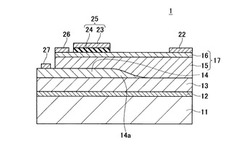

半導体装置とその製造方法

【課題】 寄生ダイオードを介したリーク電流を抑えること。

【解決手段】 半導体装置1は、c面を表面とする窒化物半導体の半導体層13と、厚みが減少する厚み減少部14aを有する窒化物半導体のp型の埋込み層14と、を備える。埋込み層14では、厚み減少部14aの内部に酸素濃度がピークとなる部分が存在しており、そのピーク部分と厚み減少部14aの傾斜面の間のp型不純物の濃度が酸素濃度よりも高い部分が存在する。

(もっと読む)

半導体ウェハ

【課題】高い結晶品質を有する、多様な材料からなる、完全に緩和した、又は歪んだ半導体層を積層するために絶縁体層の格子寸法を調整するための高い柔軟性を許容する、SOI構造の作製のための基板を提供する。

【解決手段】実質的にシリコンからなる単結晶基板ウェハ1、電気絶縁性材料を含み、かつ2nm〜100nmの厚さを有する第一非晶質中間層2、立方晶系Ia−3結晶構造と、(Me12O3)-1-x(Me22O3)xの組成と、基板ウェハの材料の格子定数と0%〜5%異なる格子定数とを有する単結晶第一酸化物層3を示される順序で含むことを特徴とする半導体ウェハ。

(もっと読む)

グラフェン構造の製造方法及びこれを用いた半導体装置の製造方法

【課題】所望の位置にグラフェン膜を有するグラフェン構造及びこれを用いた半導体装置を提供する。

【解決手段】所定の基材3上において、炭素含有層4と、少なくともケイ素を含む炭素化合物層5とを順次に積層し、その上に絶縁膜層6を形成した後、絶縁膜層の一部をエッチングにより取り除いた基板に対してアニーリングを実施し、絶縁膜の除去部にのみグラフェン膜7を形成したグラフェン構造1を形成し、これを用いて表面にショットキー電極8、およびオーミック電極9,10を形成させて半導体装置2を作製する。

(もっと読む)

複合基板の製造方法および複合基板

【課題】結晶成長用基板に形成した半導体結晶層を転写先基板に転写する場合の犠牲層のエッチング速度を高める。

【解決手段】半導体結晶層形成基板の上に犠牲層および半導体結晶層を順に形成し、転写先基板に接することとなる前記半導体結晶層形成基板の第1表面と、前記第1表面に接することとなる前記転写先基板の第2表面と、が向かい合うように、前記半導体結晶層形成基板と前記転写先基板とを貼り合わせ、前記半導体結晶層形成基板および前記転写先基板の全部または一部をエッチング液に浸漬して前記犠牲層をエッチングし、前記半導体結晶層を前記転写先基板側に残した状態で、前記転写先基板と前記半導体結晶層形成基板とを分離する。ここで、前記転写先基板が、非可撓性基板と有機物層とを有し、前記有機物層の表面が、前記第2表面であるものとする。

(もっと読む)

半導体基板の製造方法及び半導体装置

【課題】基板に形成された窒化ガリウム系半導体で形成された半導体層におけるドーパント濃度がばらつくと、半導体層を用いた半導体装置の特性がばらつくので、半導体層におけるドーパント濃度のばらつきが抑えられた層を有する半導体基板を得る。

【解決手段】基板に、窒化ガリウム系半導体で形成された半導体層を形成する半導体層形成段階と、半導体層に、中性子線を照射して、半導体層に含まれるガリウム原子の一部をゲルマニウム原子に変換する照射段階と、を備える半導体基板の製造方法を提供する。

(もっと読む)

半導体装置の製造方法

【課題】InAlN電子供給層上にGaN層を形成する場合でも、InAlN電子供給層の品質の悪化を抑制することが可能な半導体装置の製造方法を提供すること。

【解決手段】本発明は、基板10上にGaN電子走行層14を形成する工程と、GaN電子走行層14上にInAlN電子供給層18を形成する工程と、InAlN電子供給層18を形成した後、In含有ガスを供給しつつ、基板10を昇温させる工程と、昇温が終了した後、InAlN電子供給層18上にGaN層20を形成する工程と、を有する半導体装置の製造方法である。

(もっと読む)

歪吸収中間層遷移モジュールを有するIII族窒化物半導体構造

【課題】歪み吸収III族窒化物中間層モジュールを有する種々の半導体構造を提供する。

【解決手段】基板および当該基板の上方の第一遷移本体を有する。前記第一遷移本体は、第一表面において第一の格子パラメータを有し、前記第一表面とは反対側の第二表面において第二の格子パラメータを有する。前記典型的な実施では、遷移モジュール等の第二遷移本体をさらに有し、この第二遷移本体は前記第一遷移本体の前記第二表面に重層する下表面においてより小さい格子パラメータを有し、前記第二遷移本体の上表面においてより大きい格子パラメータを有し、前記第二遷移本体の上方のIII族窒化物半導体層も同様である。前記第二遷移本体は2以上の遷移モジュールからなっていてもよく、各遷移モジュールは2以上の中間層を有していてもよい。前記第一遷移本体および前記第二遷移本体は前記半導体構造の歪みを減少させる。

(もっと読む)

キャップ層および埋込みゲートを有する窒化物ベースのトランジスタを作製する方法

【課題】埋込み部を形成する際のエッチングにより埋込みゲートが損傷をきたし、ゲート領域劣化が生じ得る。

【解決手段】ショットキーコンタクトなどのゲートコンタクトを形成する前にゲート埋込み部のアニーリングを行うことにより、ゲートリークが低減され、かつ/またはトランジスタなどの半導体デバイス内に高品質のゲートコンタクトを提供することができる。アニーリング中に封入層を使用することで、トランジスタのゲート埋込み部内の半導体への損傷がさらに低減される。アニーリングを、例えばデバイスのオーミックコンタクトのアニーリングによって提供することができる。

(もっと読む)

半導体ウェハ及びその製造法

【課題】高い結晶品質を有する、多様な材料からなる、完全に緩和した、又は歪んだ半導体層を積層するために絶縁体層の格子寸法を調整するための高い柔軟性を許容する、SOI構造の作製のための基板を提供する。

【解決手段】実質的にシリコンからなる単結晶基板ウェハ1、電気絶縁性材料を含み、かつ2nm〜100nmの厚さを有する第一非晶質中間層2、立方晶系Ia−3結晶構造と、(Me12O3)-1-x(Me22O3)xの組成と、基板ウェハの材料の格子定数と0%〜5%異なる格子定数とを有する単結晶第一酸化物層3を示される順序で含むことを特徴とする半導体ウェハ。

(もっと読む)

窒化物半導体形成用基板及び窒化物半導体

【課題】窒化物半導体形成に好適な、シリコンウェーハをベースとした安価な形成用基板を提供することである。また、厚膜の窒化物半導体エピタキシャル層を成長させた場合でも、各材料間の格子定数差および熱膨張係数差から生じる、反り・クラックの発生を低減し、機械的強度や、熱的強度に優れた窒化物半導体形成用基板を提供すること。

【解決手段】ボロンとゲルマニウムとが特定濃度でドープされており、好ましくはボロンとゲルマニウムの濃度比において、ゲルマニウムの濃度をボロンの濃度の5〜8倍と制御したシリコンウェーハ。

(もっと読む)

シリコン薄膜の製造方法、シリコン薄膜太陽電池の製造方法、シリコン薄膜、シリコン薄膜太陽電池

【課題】シリコン薄膜の製造方法、シリコン薄膜太陽電池の製造方法、シリコン薄膜を提供する。

【解決手段】シリコン基板32上にシリコン結晶12の原料ガス28に対して前記シリコン結晶12の成長が不活性な不活性層38を選択的に形成することにより前記シリコン基板32の露出面34と前記不活性層38による不活性面36を形成し、前記原料ガス28のうち前記シリコン基板32における表面分解反応が支配的な性質を有する原料ガス28を前記シリコン基板32に供給して前記シリコン結晶12を前記露出面34から成長させ前記シリコン結晶12が前記シリコン基板を覆う態様でシリコン薄膜10を製造する方法であって、前記露出面34の幅を0.001μmから1μmの範囲で形成することにより、前記シリコン薄膜10を前記シリコン基板32から剥離可能な状態で形成することを特徴とする。

(もっと読む)

剥離装置および剥離方法

【課題】本発明の実施形態は、剥離作業中に剥離の適否を知ることができる剥離装置および剥離方法を提供する。

【解決手段】実施形態によれば、基板の膜が形成された側とは反対の側からレーザ光を照射して、前記基板から前記膜を剥離させる剥離装置であって、前記レーザ光とは異なる波長を有する検査光を出射する検査光源と、前記レーザ光の照射領域に照射された前記検査光の反射光、および、前記レーザ光が照射されることで前記膜の表層が分解される際に生じたプラズマ光の少なくともいずれかを検出する検出部と、前記検出された反射光、および、前記検出されたプラズマ光の少なくともいずれかに基づいて剥離の適否を判定する判定部と、を備えたことを特徴とする剥離装置が提供される。

(もっと読む)

半導体基板、半導体基板の製造方法、および電磁波発生装置

【課題】複数の異なる周波数を出力する半導体基板を提供する。

【解決手段】p型半導体またはn型半導体を含む第1の不純物半導体と、第1の不純物半導体に接する複数の空乏領域を有する空乏化半導体とを備え、複数の空乏領域のそれぞれは、第1の不純物半導体との第1界面と、第1界面と対向する表面とを有し、複数の空乏領域のそれぞれは、第1界面に垂直な方向における第1界面と表面との平均距離および組成の少なくとも一つが異なる半導体基板を提供する。

(もっと読む)

半導体薄膜の形成方法

【課題】所望の特性が得られる状態で、InPからなる基板の表面に付着した汚染物としての不純物による問題が解消できるようにする。

【解決手段】まず、Feが添加された半絶縁性のInPからなる基板101の上に、炭素(C)を添加したGaAsSbからなる半導体層(第1半導体層)102を形成する。半導体層102は、Cの添加によりp型とされている。また、添加されるCは、基板101の表面に付着している不純物とは逆の電気的特性を有する不純物となる。なお、半導体層102は、InおよびGaの少なくとも一方とAs,Sbとを少なくとも備える化合物半導体から構成されていればよく、AlzInxGa1-x-zAs1-ySby(0≦x≦0.2,0.3≦y≦1,0≦z≦1,0≦x+z≦1)から構成されていればよい。

(もっと読む)

半導体発光素子の製造方法

【課題】基板上に、面内と周縁部の膜厚の均一な塗布膜を形成することを目的とする。

【解決手段】単結晶ウエハ1と半導体層4と、その間の結晶格子の不整合を緩和するバッファ層3を備えた半導体基板の製造方法であって、前記単結晶ウエハの外周端部1aを被覆材2で被覆した後、前記バッファ層3を前記単結晶ウエハ1の一面側に形成する工程と、前記被覆材2を取り除いた後、前記半導体層4を前記バッファ層3上の一面側に形成すると共に、前記単結晶ウエハ1の外周端部1aから前記半導体層4の外周部4bにかけて前記半導体層4の構成材料からなる堆積物4aを堆積させる工程と、前記半導体層4上に塗布液をスピンコート法により塗布する工程と、を具備してなることを特徴とする半導体基板の製造方法を提供する。

(もっと読む)

半導体ウエハの製造方法

【課題】基板の表面に4H−SiC単結晶層を効率的にエピタキシャル成長させることができる半導体ウエハの製造方法を提供する。

【解決手段】半導体ウエハの製造方法は、Si層形成工程と、Si層密閉工程と、加熱工程と、成長工程とを含む。Si層形成工程では、単結晶SiC基板70の表面にSi層71を形成する。Si層密閉工程では、Si層71が形成された単結晶SiC基板70に3C−SiC多結晶層72を形成することで、Si層71を密閉する。加熱工程では、単結晶SiC基板70を加熱することで、3C−SiC多結晶層72の内側でSi層71を溶融させてSi融液層71aを形成する。成長工程では、加熱制御を行うことで、Si融液層71aが、3C−SiC多結晶層72からCとSiとを取り込むとともに、取り込んだCとSi融液層中のSiとを結合させることで、当該単結晶SiC基板70に4H−SiC単結晶をエピタキシャル成長させる。

(もっと読む)

歪み補償半導体構造および歪み補償半導体構造を製作する方法

【課題】歪みの程度がGaNの割れの閾値を上回るならば、GaNが割れ、GaNの半導体デバイスへの使用を受容できないものにする可能性がある。

【解決手段】この半導体構造は、第1の面内無歪み格子定数を有する基板と、基板上に設けられ、第1の面内無歪み格子定数とは異なる第2の面内無歪み格子定数を有する、第1の半導体材料を含む第1の層と、基板と第1の層の間に配置され、第2の半導体材料を含む可変不整合層とを含む半導体構造、およびこの半導体構造の製作方法が提供される。可変不整合層は、第1の層を基板上に直接成長させる場合に生じる応力を下回る程度にまで第1の層の応力が低減されるように構成される。可変不整合層は、第1の層の無歪み格子定数と実質的に整合する面内歪み格子定数を有する層であってもよい。

(もっと読む)

半導体素子およびその製造方法

【課題】基板の表面上に積層される半導体素子層に発生する所定の方向の歪みを低減することが可能な半導体素子を提供する。

【解決手段】この半導体素子1は、第1方向(A方向)および第2方向(B方向)に平行な主表面を有するとともに第1方向に沿って延びる段差部2aが形成された窒化物系半導体からなる基板2と、基板2上に形成され、窒化物系半導体からなる下地層3、第1半導体層4および第2半導体層5とを備える。そして、下地層3および第2半導体層5の無歪みの状態における第2方向の格子定数は、それぞれ、基板2の無歪みの状態における第2方向の格子定数よりも大きく、下地層3および第2半導体層5の基板2の主表面上に形成された状態における第2方向の格子定数は、それぞれ、基板2の第2方向の格子定数よりも大きい。

(もっと読む)

半導体素子およびその製造方法

【課題】異種基板上に高品質半導体結晶からなる島状のGaN系半導体層を基板の湾曲を抑えて成長させることができ、しかもGaN系半導体層が極めて厚くてもクラックなどの発生を抑えることができ、大面積の半導体素子を容易に実現することができる半導体素子およびその製造方法を提供する。

【解決手段】半導体素子は、GaN系半導体と異なる物質からなる基板11と、基板11上に直接または間接的に設けられ、一つまたは複数のストライプ状の開口12aを有する成長マスク12と、成長マスク12を用いて基板11上に(0001)面方位に成長された一つまたは複数の島状のGaN系半導体層13とを有する。成長マスク12のストライプ状の開口12aはGaN系半導体層13の〈1−100〉方向に平行な方向に延在している。

(もっと読む)

半導体デバイスおよび半導体構造の製造方法

【課題】 半導体結晶材料の作製またはこの半導体結晶材料を含む構造を提供する。

【解決手段】 第1の半導体結晶材料の表面の粗さは、低減されている。半導体デバイスは、第1の結晶材料の表面上に低欠陥の歪んだ第2の半導体結晶材料を含む。歪んだ第2の半導体結晶材料の表面の粗さは、低減されている。一実施例は、第1および第2の半導体結晶材料間の界面境界の不純物を減少させるプロセスパラメータを作成することによって、粗さが低減された表面を得ることを含む。一実施の形態では、第1の半導体結晶材料は、アスペクト比トラッピング技術を用いて欠陥をトラップするのに十分なアスペクト比を有する絶縁体の開口によって限定されることができる。

(もっと読む)

1 - 20 / 73

[ Back to top ]