Fターム[5F152LN11]の内容

再結晶化技術 (53,633) | 格子整合、格子不整合技術 (1,553) | バッファ層、動作層 (308)

Fターム[5F152LN11]の下位に属するFターム

Fターム[5F152LN11]に分類される特許

1 - 20 / 35

半導体装置の製造方法

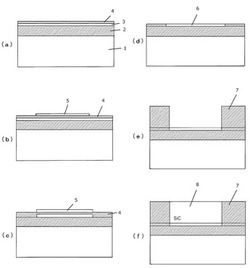

【課題】結晶性の優れた炭化シリコン膜を形成することができる炭化シリコンからなる半導体装置の製造方法を提供する。

【解決手段】基板1上に、絶縁膜2を介してシリコン膜3が形成された半導体基板を用意し、炭化シリコン膜6形成予定領域を選択的に被覆するマスク膜5を形成する。このマスク膜5で被覆されない領域のシリコン膜3を酸化し、酸化シリコン膜4を形成する。マスク膜5を除去し、シリコン膜3を露出させ、露出したシリコン膜3を炭化し、炭化シリコン膜6を形成する。その後、炭化シリコン膜6上に炭化シリコンのエピタキシャル成長膜8を形成する。

(もっと読む)

半導体基板の製造方法及び半導体装置

【課題】基板に形成された窒化ガリウム系半導体で形成された半導体層におけるドーパント濃度がばらつくと、半導体層を用いた半導体装置の特性がばらつくので、半導体層におけるドーパント濃度のばらつきが抑えられた層を有する半導体基板を得る。

【解決手段】基板に、窒化ガリウム系半導体で形成された半導体層を形成する半導体層形成段階と、半導体層に、中性子線を照射して、半導体層に含まれるガリウム原子の一部をゲルマニウム原子に変換する照射段階と、を備える半導体基板の製造方法を提供する。

(もっと読む)

III/V族半導体材料を形成する方法及びそのような方法を用いて形成された半導体構造体

【課題】内部の欠陥数がより少なく且つ/又は減少したIII/V族半導体材料を形成する方法、並びに欠陥数がより少なく且つ/又は減少したそのようなIII/V族半導体材料を含む半導体構造体及び素子が必要である。

【解決手段】三元III族窒化物材料を形成する方法は、チャンバー内で基板上に三元III族窒化物材料をエピタキシャル成長させるステップを含む。エピタキシャル成長は、チャンバー中の窒素前駆体の分圧と1つ又は複数のIII族前駆体の分圧との比較的に高い比を含む前駆体ガス混合物をチャンバー内に準備するステップを含む。少なくとも一部は比較的に高い比のため、三元III族窒化物材料の層は、小さいVピット欠陥をその中に含む高い最終厚さに成長させることができる。そのような三元III族窒化物材料の層を含む半導体構造体をそのような方法を用いて作製する。

(もっと読む)

光デバイスウエーハの加工方法

【課題】光デバイスウエーハを構成するエピタキシー基板の表面に積層された光デバイス層に損傷を与えることなく光デバイス層を移設基板に円滑に移し変えることができる光デバイスウエーハの加工方法を提供する。

【解決手段】エピタキシー基板20の表面にバファー層22を介して積層され、格子状に形成された複数のストリート23により区画された複数の領域に形成された光デバイス層21の表面に移設基板3を接合する工程と、移設基板3が接合されたエピタキシー基板20を所定のストリートに沿って切断し、複数のブロック200に分割する工程と、エピタキシー基板20の裏面側からエピタキシー基板20を透過するレーザー光線をバファー層22に集光点を位置付けて照射することによりバファー層22を分解する工程と、複数のブロック200に分割されたエピタキシー基板20を光デバイス層21から剥離する工程とを含む。

(もっと読む)

GaN系半導体エピタキシャル基板の製造方法

【課題】異種基板上にGaN系半導体を成長させることにより発生する貫通転位を低減し、低転位密度(例えば、105/cm2以下)のGaN系半導体をエピタキシャル成長させることができるGaN系半導体エピタキシャル基板の製造方法を提供する。

【解決手段】異種材料からなる成長用基板(例えばNGO基板)上にGaN系半導体をエピタキシャル成長させる際に、成長用基板上に、第1GaN系半導体層をエピタキシャル成長させ(第1工程)、第1GaN系半導体層における転位発生部分にエッチピットを形成し(第2工程)、エッチピットにSi3N4膜を選択的に形成し(第3工程)、Si3N4膜上に第2GaN系半導体層をエピタキシャル成長させる(第4工程)。

(もっと読む)

半導体発光素子の製造方法

【課題】基板上に、面内と周縁部の膜厚の均一な塗布膜を形成することを目的とする。

【解決手段】単結晶ウエハ1と半導体層4と、その間の結晶格子の不整合を緩和するバッファ層3を備えた半導体基板の製造方法であって、前記単結晶ウエハの外周端部1aを被覆材2で被覆した後、前記バッファ層3を前記単結晶ウエハ1の一面側に形成する工程と、前記被覆材2を取り除いた後、前記半導体層4を前記バッファ層3上の一面側に形成すると共に、前記単結晶ウエハ1の外周端部1aから前記半導体層4の外周部4bにかけて前記半導体層4の構成材料からなる堆積物4aを堆積させる工程と、前記半導体層4上に塗布液をスピンコート法により塗布する工程と、を具備してなることを特徴とする半導体基板の製造方法を提供する。

(もっと読む)

発光サイリスタ、発光素子アレイ、発光装置および画像形成装置

【課題】 ベース層のキャリア濃度および厚み寸法を大きく設定することなく、発光強度に対する電流増幅率βの影響を抑制することのできる発光サイリスタ、発光素子アレイ、発光装置および画像形成装置を提供することである。

【解決手段】 発光サイリスタは、基板上に第1半導体層、第1半導体層と反対導電型の第2半導体層、第1半導体層と同じ導電型の第3半導体層、および第1半導体層と反対導電型の第4半導体層がこの順に積層されており、第3半導体層のバンドギャップは、第2半導体層のバンドギャップと略同一、かつ、第1および第4半導体層のバンドギャップより狭幅であり、第3半導体層は、基板側の第1領域と基板と反対側の第2領域とからなり、かつ、第1領域の不純物濃度は1×1016(cm−3)未満である。

(もっと読む)

歪Si−SOI基板の製造方法及び該方法により製造された歪Si−SOI基板

【課題】歪Si層表面が平坦で欠陥が少ない歪Si−SOI基板を簡便に製造する。

【解決手段】SOI基板10の第1Si層13上にSiGe混晶層14を形成し、SiGe混晶層上に第1Si層の厚さより厚い55〜550nmの厚さの第2Si層16を形成する。基板を酸化性雰囲気下又は不活性ガス雰囲気下、950℃以上で熱処理してSiGe混晶層を溶融するとともに第1Si層と第2Si層の一部にGeを拡散する。基板を降温して溶融したSiGe混晶層18,19,21を固化し、固化したSiGe混晶層22の上に歪Si層16aが形成された歪Si−SOI基板23を得る。

(もっと読む)

半導体電子デバイス

【課題】耐圧性が高く反りが小さい半導体電子デバイスを提供すること。

【解決手段】基板と、前記基板上に形成された、前記基板よりも格子定数が小さく熱膨張係数が大きい窒化物系化合物半導体からなる第一半導体層と該第一半導体層よりも格子定数が小さく前記基板よりも熱膨張係数が大きい窒化物系化合物半導体からなる第二半導体層とが交互に積層した2層以上の複合層を有するバッファ層と、前記基板と前記バッファ層との間に形成された、前記第一半導体層よりも格子定数が小さく前記基板よりも熱膨張係数が大きい窒化物系化合物半導体からなる介在層と、前記バッファ層上に形成された、窒化物系化合物半導体からなる半導体動作層と、を備え、前記バッファ層において、前記第一半導体層の層厚が不均一であるとともに、該第一半導体層のうち少なくとも一つが、前記基板に対して発生させる反りの方向が反転する臨界厚さよりも厚い層厚を有する。

(もっと読む)

基板の製造方法

【課題】III族窒化物の結晶体の基板を製造する際における剥離バッファー層をエッチングするための時間を短縮する方法を提供する。

【解決手段】基板の製造方法は、下地基板の上にバッファー層を形成するバッファー層形成工程S1と、バッファー層の上に、バッファー層の一部を覆うマスクパターンを形成するマスクパターン形成工程S2と、バッファー層及びマスクパターンを覆うように、III族窒化物の結晶体を成長させる成長工程S5と、マスクパターンの第1のエッチャントを用いてマスクパターンを選択的にエッチングすることにより、バッファー層の第2のエッチャントを供給するための経路を形成する経路形成工程S6と、経路を介して第2のエッチャントを供給してバッファー層を選択的にエッチングすることにより、結晶体を下地基板から分離する分離工程S7とを備える。

(もっと読む)

炭化ケイ素半導体装置およびその製造方法

【課題】炭化ケイ素からなる基板上に欠陥密度の低減された活性層が形成された炭化ケイ素半導体装置およびその製造方法を提供する。

【解決手段】半導体装置1は、面方位{0001}に対しオフ角が50°以上65°以下である、炭化ケイ素からなる基板2と、バッファ層21と、活性層(エピタキシャル層3、p型層4、およびn+領域5、6)とを備える。バッファ層21は、基板2上に形成され、炭化ケイ素からなる。活性層は、バッファ層21上に形成され、炭化ケイ素からなる。活性層におけるマイクロパイプ密度は基板2におけるマイクロパイプ密度より低い。また、活性層における、バーガーズベクトルの向きが[0001]である転位の密度は、基板2における当該転位の密度より高い。

(もっと読む)

半絶縁性窒化物半導体基板とその製造方法並びに窒化物半導体エピタキシャル基板及び電界効果トランジスタ

【課題】 反りが少なくクラックが発生しない半絶縁性の窒化物半導体結晶基板及びその製造方法を提供する。

【解決手段】 下地基板の上に、幅或いは直径sが10μm〜100μmであるドット被覆部或いはストライプ被覆部を間隔wが250μm〜2000μmであるように並べたマスクを形成し、HVPE法によって成長温度が1040℃〜1150℃であって、5/3族比bが1〜10であるような3族、5族原料ガスと、鉄を含むガスとを供給することによって下地基板の上に窒化物半導体結晶を成長させ、下地基板を除去することによって、比抵抗が1×105Ωcm以上、厚みが100μm以上、反りの曲率半径が3m以上の自立した半絶縁性窒化物半導体基板を得、更にその基板を用いたデバイスの作製を得る。

(もっと読む)

半導体基板およびその製造方法、ならびに半導体装置

【課題】圧縮歪層と引張歪層とを利用して、InP系半導体デバイスを成長させるメタモルフィック基板の欠陥(例えば転位)の低減を可能にする。

【解決手段】ガリウムヒ素基板100と、前記ガリウムヒ素基板100上に形成されたバッファ層101と、前記バッファ層101上に、前記バッファ層101よりも面内方向の格子定数が小さい材料からなる引張歪層105aと、前記バッファ層101よりも面内方向の格子定数大きい材料からなる圧縮歪層105bとを積層して形成された歪補償構造層105とを有することを特徴とする。

(もっと読む)

素子基板とその製造法

【課題】

酸化亜鉛、および、酸化亜鉛固溶体からなる電子素子、光素子を製造する上で、酸化亜鉛、および酸化亜鉛固溶体の結晶構造に由来する自発分極の方向を考慮した結晶成長が求められる。これらを実現するには、結晶成長に際しての基板材質の選択、および、結晶成長時の成長条件、あるいは、結晶成長後の後処理等を検討し、所望の自発分極方向、すなわち、所望の結晶成長方向に対して結晶を成長する技術が得られなければならない。かつ、製造コストなどの経済性を考慮した場合、より流通量の多い、安定した供給の得られる基板材質をも使用できる、自発分極方向、すなわち、結晶成長方向を制御した酸化亜鉛を提供することが求められる。

【解決手段】

本発明の素子基板は、基板と酸化亜鉛薄膜との間にスピネル型構造の緩衝層を有し、前記酸化亜鉛薄膜は、ウルツ鉱型の結晶構造を有し、その表面が亜鉛(0001)面であることを特徴とする。

(もっと読む)

半導体装置の製造方法、半導体装置および電子機器

【課題】InP基板に擬似格子整合もしくは格子整合させたデバイス層を形成し、そのデバイス層よりInP基板を剥離して、InP基板の再利用を可能とする。

【解決手段】インジウムリン(InP)基板11上に擬似格子整合もしくは格子整合する犠牲層12を形成する工程と、前記犠牲層12上にデバイス層13を形成する工程と、前記犠牲層12を除去することで前記InP基板11と前記デバイス層13とを分離する工程とを備えたことを特徴とする。

(もっと読む)

炭化珪素半導体装置の製造方法および炭化珪素半導体装置

【課題】デバイス中のベーサルプレーン転位を低減させること。

【解決手段】炭化珪素半導体基板100は、炭化珪素単結晶基板101上に、窒素(N)をドープしたNドープn型SiCエピタキシャル層102、およびリン(P)をドープしたPドープn型SiCエピタキシャル層103が順に積層されている。Nドープn型SiCエピタキシャル層102およびPドープn型SiCエピタキシャル層103は、エピタキシャル成長時に2種類以上のドーパント、たとえば、窒素およびリンを用いることによって形成される。

(もっと読む)

半導体構造およびその成長方法

【課題】薄いバッファ層を採用した高品質のGeエピタキシャル層を有する半導体構造およびその成長方法を提供する。

【解決手段】 この半導体構造は、Si基板と、その上に形成された臨界膜厚以下の厚さのGe組成が20%以上80%以下のSiGe層と、SiGe層上に形成されたGeエピタキシャル層とを有する。

(もっと読む)

半導体基板の製造方法

【課題】ミスフィット転位による結晶欠陥の発生が抑制されたSiCを備え、反りが低減された半導体基板の製造方法を提供する

【解決手段】半導体基板10は、Si基板12から自然酸化膜12aを除去した後、その表面にSi1−XGeX層13を成膜し、続いてSi1−XGeX層13を炭化させてSi1−X−YGeXCY層14を形成し、次いでSi1−X−YGeXCY層14の表面にヘテロエピタキシャル成長により3C−SiC層16を成膜することにより製造される。

(もっと読む)

III族窒化物系半導体、その製造方法、発光素子及び照明装置

【課題】 P型不純物がドープされ活性化されたIII族窒化物系半導体をアニールを必要とせずに容易に製造可能なP型導電性のIII族窒化物系半導体等を提供すること。

【解決手段】 基板110の一主面上に形成されたIII族窒化物系半導体(P型半導体層112)であり、III族窒化物系半導体に基板110からの不純物が含まれている。これにより、アクセプタ不純物としてのホウ素を、基板110から直接的にIII族窒化物系半導体に混入させることができる。

(もっと読む)

III族窒化物半導体素子用エピタキシャル基盤

【課題】 優れた発光効率、逆耐電圧特性および静電耐圧特性等を有するIII族窒化物半導体発光素子の製造に適したIII族窒化物半導体素子用エピタキシャル基盤を提供すること。

【解決手段】 表面粗さ(Ra)が1nm以下の基板と該基板上に直接積層されたIII族窒化物半導体層とからなり、該III族窒化物半導体層は互いに接する複数の層からなり、該複数の層の少なくとも一層は転位密度が1×107cm-2以下の層であるIII族窒化物半導体素子用エピタキシャル基盤。

(もっと読む)

1 - 20 / 35

[ Back to top ]