Fターム[5F152LN15]の内容

再結晶化技術 (53,633) | 格子整合、格子不整合技術 (1,553) | バッファ層、動作層 (308) | 組成変化 (147) | 階段状に変化 (53)

Fターム[5F152LN15]に分類される特許

1 - 20 / 53

半導体基板の製造方法

【課題】シリコンウェハ等のベース基板上方に窒化物半導体からなる半導体結晶層を形成する場合に、当該半導体結晶層の転位密度を低減する。

【解決手段】ベース基板をエピタキシャル結晶成長装置の成長室に設置した後、ベース基板の上に、接着層、バッファ層および活性層をエピタキシャル成長法により順次形成する層形成工程を有し、接着層形成工程が、第1結晶層を形成する工程と第2結晶層を形成する工程と、を有し、第1結晶層の形成後であって第2結晶層の形成前の第1の段階、および、第2結晶層の形成後であってバッファ層の形成前の第2の段階、からなる群から選択された少なくとも1つの段階において、3族原料ガスの供給を停止するとともに成長室の内部を、アンモニアを含むガスの雰囲気に一定時間だけ維持する雰囲気維持工程を有する半導体基板の製造方法を提供する。

(もっと読む)

III族窒化物エピタキシャル基板およびその製造方法

【課題】デバイス化の工程で割れが発生することを抑制することが可能なIII族窒化物エピタキシャル基板およびその製造方法を提供する。

【解決手段】本発明のIII族窒化物エピタキシャル基板10は、Si基板11と、該Si基板11と接する初期層14と、該初期層14上に形成され、Al組成比が0.5超え1以下のAlGaNからなる第1層15A1(15B1)およびAl組成比が0超え0.5以下のAlGaNからなる第2層15A2(15B2)を順次有する積層体を複数組有する超格子積層体15と、を有し、前記第2層のAl組成比が、前記基板から離れるほど漸減することを特徴とする。

(もっと読む)

半導体素子及びその製造方法

【課題】転位密度を低減させるバッファ層を有する半導体素子を提供する。

【解決手段】基板と、基板の上方に形成されたバッファ領域と、バッファ領域上に形成された活性層と、活性層上に形成された少なくとも2つの電極とを備え、バッファ領域は、第1の格子定数を有する第1半導体層と、第1の格子定数と異なる第2の格子定数を有する第2半導体層と、第1の格子定数と第2の格子定数との間の第3の格子定数を有する第3半導体層とが順に積層した複合層を少なくとも一層有する半導体素子。

(もっと読む)

半導体素子及びその製造方法

【課題】厚膜化が可能で、反りが小さく、かつリーク電流が小さい半導体素子を提供する。

【解決手段】基板と、基板の上方に形成された第1のバッファ領域と、第1のバッファ領域上に形成された第2のバッファ領域と、第2のバッファ領域上に形成された活性層と、活性層上に形成された少なくとも2つの電極とを備え、第1のバッファ領域は、第1半導体層と、第2半導体層とが順に積層した複合層を少なくとも一層有し、第2のバッファ領域は、第3半導体層と、第4半導体層と、第5半導体層とが順に積層した複合層を少なくとも一層有し、第4半導体層の格子定数は、第3半導体層と第5半導体層の間の格子定数を有する半導体素子。

(もっと読む)

半導体基板及びその製造方法

【課題】単純な単結晶シリコン基板を出発基板として窒化ガリウム膜を形成することができ、反りやクラックが抑制された半導体基板及びその製造方法を提供する。

【解決手段】半導体基板10は、単結晶シリコン基板11と、前記単結晶シリコン基板11の最表面を除く表層領域に形成された転位層12と、前記単結晶シリコン基板11の前記最表面に形成されたバッファ層13と、前記バッファ層13の表面に形成された窒化ガリウム層14とを備えている。転位層12は、窒化ガリウム層14が形成された単結晶シリコン基板14の表層領域に転位が発生し且つ単結晶シリコン基板11の最表面には転位が発生しない条件下でイオン注入することにより形成される。イオン注入では、ドーズ量が5E+14atoms/cm2以上5E+17atoms/cm2以下のアルゴンイオンを注入する。

(もっと読む)

イオン・インプラント・アイソレーションによるLED製作

【課題】電気的に隔離された発光ダイオードを提供する。

【解決手段】半導体発光ダイオードは、半導体基板51と、基板上にあるn型III群窒化物のエピタキシャル層52と、n型エピタキシャル層上にあり当該n型層と共にp−n接合部を形成する、III群窒化物のp型エピタキシャル層53と、n型エピタキシャル層上にありp型エピタキシャル層に隣接し、p−n接合部58の一部を電気的に隔離する抵抗性窒化ガリウム領域54とを含む。p型エピタキシャル層上に金属接点層55を形成する。方法の実施形態では、p型エピタキシャル領域上に打ち込みマスクを形成し、p型エピタキシャル領域の部分にイオンを打ち込んでp型エピタキシャル領域の部分を半絶縁性にすることによって、抵抗性窒化ガリウム境界を形成する。フォトレジスト・マスク又は十分に厚い金属層を、打ち込みマスクとして用いることができる。

(もっと読む)

半導体基板の製造方法および半導体デバイスの製造方法

【課題】シリコンデバイス等耐熱性の低い部位がSi基板に設けられた場合でも、Ge結晶に熱アニールを施し、十分な結晶品質のGe結晶薄膜を得る。

【解決手段】表面がSiであるベース基板と、前記ベース基板の上に形成され、組成がCxSiyGezSn1−x−y―z(0≦x<1、0≦y<1、0<z≦1、かつ、0<x+y+z≦1)である第1結晶層と、前記第1結晶層が形成された部分以外の前記ベース基板の上に形成された第1半導体素子と、を有する半導体基板の製造方法であって、前記第1半導体素子には電磁波を照射することがなく、前記第1結晶層の一部または全部に電磁波を照射する工程を有する半導体基板の製造方法を提供する。

(もっと読む)

非極性または半極性(Ga、Al、In、B)N基板上に成長させられる素子

非極性または半極性の(Ga、Al、In、B)N基板上の(Ga、Al、In、B)N薄膜の成長形態を改良する方法であって、(Ga、Al、In、B)N薄膜は、非極性または半極性の(Ga、Al、In、B)N基板あるいはテンプレート上に直接成長させられ、成長の際に使用されるキャリアガスの一部は、不活性ガスから構成される。非極性または半極性の窒化物LEDおよびダイオードレーザは、本発明によって成長させられる平滑(Ga、Al、In、B)N薄膜上に成長させられてもよい。  (もっと読む)

(もっと読む)

歪み半導体デバイス用のゲルマニウム含有量が漸次変化した高ゲルマニウム化合物膜

ゲルマニウム含有量が漸次変化した高ゲルマニウム化合物領域を供する装置及び方法に係る実施例が全体として記載されている。他の実施例も記載及びクレームされている。  (もっと読む)

(もっと読む)

半導体装置の製造方法

【課題】半導体製造工程におけるストレス印加およびアニールによる転位、結晶欠陥を抑え、チャネル領域において良好なストレスを印加するとともに、低抵抗化と浅接合化の両立を図ることが可能な半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法において、半導体基板表面に前記半導体基板表面の面積に対する開口率が5〜30%の開口部を形成する工程と、前記開口部内に15〜25%の範囲の濃度で前記半導体基板を構成する原子と異なる格子定数を有する第2の原子を含む混晶からなるエピタキシャル層を形成する工程と、前記エピタキシャル層にイオン注入する工程と、所定の温度Tで活性化アニールを行う工程とを備え、前記所定の温度Tは、1150℃以上かつT≦1E−5exp(21541/T)からなる関係を満たす。

(もっと読む)

グレーデッドエピタキシャル成長を用いた半導体品の製造プロセス

【課題】緩和III−V族またはII−VI族マテリアルオンインシュレータの製造方法の提供。

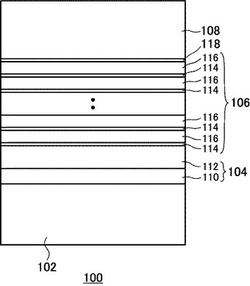

【解決手段】緩和Si1−yGey層104を有する半導体構造の形成プロセスは、第1の基板上へのグレーデッドSi1−xGexバッファ層102の堆積であって、前記Ge濃度xはゼロから値yまで増加するものである堆積、緩和Si1−yGey層104の堆積、前記緩和Si1−yGey層104中にイオンを導入して第1のヘテロ構造を規定、前記第1のヘテロ構造を第2の基板108に接合して第2のヘテロ構造を規定、および前記導入されたイオンの領域での前記第2のヘテロ構造の分割であって、前記緩和Si1−yGey層104の表層部分は前記第2の基板上108に残るものである分割を含む。

(もっと読む)

半導体基板

【課題】従来に比べ極めて薄いバッファ層を用いて、工業的に安定でかつ低コストで、基板と格子定数の異なる良質の薄膜を形成した半導体基板を提供すること。

【解決手段】基板1は、格子定数xを有するものである。第1の半導体層2は、基板1上に形成され、格子定数yを有し、少なくともSbを含んでいる。第2の半導体層3は、第1の半導体層2上に形成され、格子定数yからzまで格子定数を段階的又は連続的に変化させものである。第3の半導体層4は、第2の半導体層3上に形成され、格子定数zを有するものある。これらの格子定数の関係は、x<z<yの関係を有している。基板1上に格子定数の異なる薄膜を形成する際に、まずSbを含む半導体を形成し、その上層に格子定数を変化させるためのバッファ層を形成することで、従来に比べ薄いバッファ層で結晶欠陥のない薄膜形成が可能となる。

(もっと読む)

半導体装置の製造方法

【課題】Si系基板上に結晶性の良いSi系単結晶をエピタキシャル成長させることのできる半導体装置の製造方法を提供する。

【解決手段】本発明の一態様に係る半導体装置の製造方法は、酸化物からなる部材を備えたSiを主成分とする半導体基板の表面をSiおよびGeのうちの少なくともいずれか1つを含むハロゲン含有ガスに曝す工程と、前記半導体基板の前記表面をハロゲン含有ガスに曝し始めた後、前記表面をハロゲンを含まないSi含有ガスおよびハロゲンを含まないGe含有ガスのうち少なくともいずれか1つを含む雰囲気に曝し、前記表面にSiおよびGeのうち少なくともいずれか1つを含む結晶膜をエピタキシャル成長させる工程と、を含む。

(もっと読む)

相分離が抑制されたIII族窒化物材料系を用いた半導体構造及び光検出器

【課題】レーザダイオード、トランジスタ、光検出器などの半導体構造に使用され、相分離を抑制または解消するとともに発光効率を向上させるIII族窒化物4元及び5元材料系並びに方法を提供する。

【解決手段】典型的な実施形態では、半導体構造は、ほぼ相分離なく形成された第1導電型のBAlGaN材料系を用いた4元材料層と、ほぼ相分離のないBAlGaN材料系を用いた4元材料活性層と、ほぼ相分離なく形成された逆導電型のBAlGaN材料系を用いた別の4元材料層を備えている。

(もっと読む)

伸張歪ゲルマニウム薄膜の作製方法、伸張歪ゲルマニウム薄膜、及び多層膜構造体

【課題】 ゲルマニウム錫混晶層の歪緩和を促進し、より大きな面内伸張歪を持つ伸張歪ゲルマニウム層を形成することができる多層膜構造体を提供する。

【解決手段】半導体装置に好適な多層膜構造体10の形成方法として、シリコン基板11の上方にゲルマニウム層12を形成する工程と、その上方にゲルマニウム錫混晶層13を形成する工程と、その上方に伸張歪ゲルマニウム層14を形成する工程とを含む。

(もっと読む)

半導体ウエーハ及び半導体素子及び製造方法

【課題】 シリコン基板上に窒化物半導体領域を設けると、半導体ウエーハに反りが発生する。

【解決手段】 シリコン基板2の上に窒化物半導体から成るバッファ領域3を介してHEMT用の窒化物半導体から成る主半導体領域4を設ける。前記バッファ領域4を、第1の多層構造バッファ領域5と第2の多層構造バッファ領域8とで構成する。第1の多層構造バッファ領域5を複数のサブ多層構造バッファ領域6と複数の単層構造バッファ領域7で構成する。サブ多層構造バッファ領域6を、交互に配置された複数の第1及び第2の層で構成する。第1の層をアルミニウムを第1の割合で含む窒化物半導体で形成する。第2の層をアルミニウムを含まない又は前記第1の割合よりも小さい第2の割合で含む窒化物半導体で形成する。第2の多層構造バッファ領域8を第3及び第4の層で構成する。第3の層のアルミニウム割合を第1の割合よりも低くする。

(もっと読む)

半導体ウエーハ及び半導体素子及び製造方法

【課題】 シリコン基板上に窒化物半導体領域を設けると、半導体ウエーハに反りが発生する。

【解決手段】 シリコン基板2の上に窒化物半導体から成るバッファ領域3を介して主半導体領域4を設ける。前記バッファ領域4を、複数の多層構造バッファ領域5,5′と、該複数の多層構造バッファ領域5,5′の相互間に配置された第2の単層構造バッファ領域8とで構成する。複数の多層構造バッファ領域5,5′のそれぞれを、交互に配置された複数の第1及び第2の層から成るサブ多層構造バッファ領域と第2の単層構造バッファ領域8よりも薄い第1の単層構造バッファ領域とで構成する。第1の層をアルミニウムを第1の割合で含む窒化物半導体で形成する。第2の層、第1の単層構造バッファ領域及び第2の単層構造バッファ領域8のアルミニウムの割合(ゼロを含む)を第1の割合よりも小さくする。

(もっと読む)

半導体電子デバイス

【課題】異種基板上のバッファ層の結晶性を向上させた窒化物系化合物半導体を有する半導体電子デバイスを提供する。

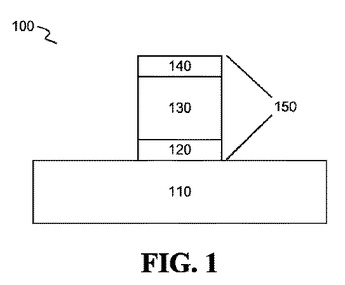

【解決手段】窒化物系化合物半導体を有する半導体電子デバイスにおいて、基板10上に窒化物系化合物半導体からなるバッファ層20及び半導体動作層30を順次積層してなり、前記バッファ層20は、第1の層22と第2の層23が積層された複合層を1層以上有し、第1の層22と第2の層23との各格子定数の差は0.2%以上であり、第1の層22の厚さは、100nm以上、1000nm以下である。

(もっと読む)

半導体ヘテロ構造を作製する方法

【課題】接合の前に最上層を有するドナー・ウェーハ基板上への熱負荷を軽減すること、および、にも拘らず接合の良好な結果を達成すること。

【解決手段】ドナー・ウェーハを作製するために、第1の面内格子定数を持つ第1の基板と、該第1の基板上に、上部が格子緩和状態で第2の面内格子定数を有する空間的に組成傾斜した緩衝層とを準備し、該組成傾斜した緩衝層上に、格子緩和状態で第3の面内格子定数を有する半導体材料の組成非傾斜層を形成し、該組成非傾斜層上に半導体材料の最上層を形成する。また、持ち運び用ウェーハを作製するために、第2の基板を準備し、該第2の基板上に絶縁層を形成し、ドナー・ウェーハを持ち運び用ウェーハに接合する。

(もっと読む)

半導体装置及びその製造方法

【課題】従来の不具合を抑制しながらキャリアの移動度を高くすることができる半導体装置及びその製造方法を提供する。

【解決手段】溝8内にp型のSiGe混晶層49aがエピタキシャル成長法により形成され、その上にp型のSiGe混晶層49bがエピタキシャル成長法により形成されている。更に、SiGe混晶層49b上にp型のSiGe混晶層49cがエピタキシャル成長法により形成されている。なお、SiGe混晶層49aの最表面の溝8の底からの高さa4は、シリコン基板1の表面を基準としたときの溝8の深さよりも低い。また、SiGe混晶層49bの最表面の溝8の底からの高さb4は、シリコン基板1の表面を基準としたときの溝8の深さよりも高い。更に、SiGe混晶層49a及び49c中のGe濃度は、SiGe混晶層49b中のGe濃度より低い。

(もっと読む)

1 - 20 / 53

[ Back to top ]