Fターム[5F152MM03]の内容

再結晶化技術 (53,633) | 半導体素子等への用途 (2,408) | 電子素子 (1,201) | トランジスタ (962)

Fターム[5F152MM03]の下位に属するFターム

MOSFET (619)

MESFET、HEMT (163)

JFET (21)

バイポーラトランジスタ (105)

Fターム[5F152MM03]に分類される特許

1 - 20 / 54

シリコン基板、これを採用したエピ構造体及びシリコン基板の製造方法

半導体基板の製造方法

【課題】シリコンウェハ等のベース基板上方に窒化物半導体からなる半導体結晶層を形成する場合に、当該半導体結晶層の転位密度を低減する。

【解決手段】ベース基板、接着層、バッファ層および活性層を有し、前記ベース基板、前記接着層、前記バッファ層および前記活性層がこの順に位置し、前記ベース基板の前記接着層と接する領域にSiが存在し、前記接着層、前記バッファ層および前記活性層が、窒化物半導体からなる半導体基板の製造方法であって、前記ベース基板をエピタキシャル結晶成長装置の成長室に設置した後、前記ベース基板の温度を1000℃以上1150℃以下に維持しつつ前記ベース基板の表面を水素ガスに暴露する水素ガス暴露工程と、前記水素ガス暴露工程の後、前記ベース基板の上に、前記接着層、前記バッファ層および前記活性層をエピタキシャル成長法により順次形成する層形成工程と、を有する半導体基板の製造方法を提供する。

(もっと読む)

半導体素子の製造方法

【課題】SiC半導体基板の不純物元素を捕捉・固定するためのゲッタリング層の形成を含む半導体素子の製造方法を提供する。

【解決手段】SiC基板10上にSiCエピタキシャル層16を形成し、該エピタキシャル層16にイオン注入および熱処理を行なって半導体素子を製造する方法において、上記SiC基板10よりも欠陥密度の高いゲッタリング層13を形成する工程を含むことを特徴とする半導体素子の製造方法。

(もっと読む)

半導体材料、半導体材料の製造方法及び半導体素子

【課題】pn接合のI−V特性を向上させる半導体材料を提供すること。

【解決手段】本発明に係る半導体材料は、酸化亜鉛の結晶を含有する粒子を備え、酸化亜鉛の結晶子の大きさが5〜50nmであり、酸化亜鉛の結晶における窒素の含有率が500〜10000質量ppmである。

(もっと読む)

窒化ガリウム基板

【課題】量産に用い得る厚さと面積を確保しながら、容易な生産方法でかけやわれの発生を抑制してオリエンテーションフラットを形成することを目的とする。

【解決手段】窒化ガリウム結晶体27から、ファセット15を有する硬質の立体構造物14を陵線等に平行に除去することで、欠けや割れの発生を抑制した窒化ガリウム基板を提供できる。しかも、ファセット15を有する硬質の立体構造物14の陵線等は特有の結晶方位を有し、かつ、明瞭であるので、立体構造物14の陵線等に平行に切断加工した窒化ガリウム結晶体27の切断線21をデバイス加工の基準線となるオリエンテーションフラットに用いることができる。

(もっと読む)

半導体装置

【課題】シリコンなどの基板上に形成した高品質な結晶を有する半導体装置を提供する。

【解決手段】実施形態によれば、GaNを含む下地層と、窒化物半導体を含む機能部と、前記下地層と前記機能部との間に設けられ、AlNを含む層を含む中間層と、を備えた半導体装置が提供される。前記下地層のうちの前記中間層とは反対側の第1領域におけるシリコン原子の濃度は、前記下地層のうちの前記中間層の側の第2領域におけるシリコン原子の濃度よりも高く、前記下地層の前記中間層とは反対側の第1面は、複数の凹部を有する。

(もっと読む)

III/V族半導体材料を形成する方法及びそのような方法を用いて形成された半導体構造体

【課題】内部の欠陥数がより少なく且つ/又は減少したIII/V族半導体材料を形成する方法、並びに欠陥数がより少なく且つ/又は減少したそのようなIII/V族半導体材料を含む半導体構造体及び素子が必要である。

【解決手段】三元III族窒化物材料を形成する方法は、チャンバー内で基板上に三元III族窒化物材料をエピタキシャル成長させるステップを含む。エピタキシャル成長は、チャンバー中の窒素前駆体の分圧と1つ又は複数のIII族前駆体の分圧との比較的に高い比を含む前駆体ガス混合物をチャンバー内に準備するステップを含む。少なくとも一部は比較的に高い比のため、三元III族窒化物材料の層は、小さいVピット欠陥をその中に含む高い最終厚さに成長させることができる。そのような三元III族窒化物材料の層を含む半導体構造体をそのような方法を用いて作製する。

(もっと読む)

半導体基板の製造方法

【課題】表面保護膜の剥離ムラやウォーターマークの発生、及びSi基板への不純物吸着等の問題を抑制することにより、固体撮像装置を作製した場合に暗電流の白傷欠陥の発生を効果的に防止可能なエピタキシャル基板の製造方法を提供する。

【解決手段】SiからなるCZ基板11上に、アクリル樹脂をベースポリマーとする有機膜12を形成する。有機膜12を介してCZ基板11に炭素イオンを注入し、CZ基板11中に炭素注入領域13を形成する。その後、有機膜12を比較的強い酸化剤であるSPM(硫酸過酸化水素水)の溶液によるウェットエッチング、若しくは水素ガスを用いたドライエッチングで洗浄して除去する。その後はCZ基板11の表面にSi材料を用いてSiエピタキシャル層14を形成し、エピタキシャル基板を得る。

(もっと読む)

半導体装置

【課題】転位ループが発生するおそれがあるダミーパターン領域を有しながらも、転位ループによる基板上の他の素子等への悪影響が抑えられた半導体装置を提供する。

【解決手段】一実施の形態による半導体装置は、基板上に形成された素子分離絶縁膜と、前記素子分離絶縁膜により前記基板上に区画された素子領域およびダミーパターン領域と、前記素子領域内の前記基板上に形成された第1のエピタキシャル結晶層と、前記ダミーパターン領域内の前記基板上に形成された第2のエピタキシャル結晶層と、を有する。第1のエピタキシャル結晶層は前記基板を構成する結晶と異なる格子定数を有する結晶からなる。第2のエピタキシャル結晶層は前記第1のエピタキシャル結晶層と同じ結晶からなる。前記第2のエピタキシャル結晶層と前記基板との界面上の任意の点を含む前記基板の(111)面は、前記第2のエピタキシャル結晶層よりも深い領域で前記素子分離絶縁膜に囲まれる。

(もっと読む)

化合物半導体基板

【課題】基板の反りの低減とデバイスの高速性を高いレベルで実現することのできる化合物半導体基板を提供する。

【解決手段】

Si単結晶の基板と、基板の主面上に形成された窒化物半導体の中間層と、中間層の主面上に形成された窒化物半導体の化合物半導体層からなり、基板の酸素濃度が0.2×1018atoms/cm3以上1.4×1018atoms/cm3以下であり、抵抗値が1000Ωcm以上であり、前記中間層と前記化合物半導体層を合計した、主面と垂直方向の膜厚が450nm以上4500nm以下であることを特徴とする化合物半導体基板。

(もっと読む)

エピタキシャルシリコンウェーハの製造方法

【課題】研磨工程の簡略化で生産性が高まり、コストダウンが可能で、鏡面研磨されたウェーハ表面に生じる加工起因のLPDの密度を低減し、ウェーハ表面の表面粗さを改善可能なエピタキシャルシリコンウェーハの製造方法を提供する。

【解決手段】1次、2次研磨のみを行い仕上げ研磨を省略するので、シリコンウェーハの研磨が簡略化し、エピタキシャルシリコンウェーハの生産性が高まり、コストダウンが図れる。また、従来の砥粒を含む1次研磨のみを施した場合に比べて、ウェーハ表面に発生する加工起因のLPDの密度が低減し、ウェーハの表面粗さが小さくなる。さらに、砥粒で酸化膜を除去する1次研磨を行うので、砥粒が存在しない2次研磨時、アルカリ性水溶液による研磨レートが高まる。

(もっと読む)

エピタキシャルシリコンウェーハの製造方法

【課題】シリコンウェーハの鏡面研磨された表面に発生する加工起因のLPDの密度を低減し、かつウェーハ表面の表面粗さを小さくすることで、LPD密度が低く、表面粗さ品質に優れたエピタキシャル膜を有するエピタキシャルシリコンウェーハの製造方法を提供する。

【解決手段】砥粒を含まず水溶性高分子を含むアルカリ性水溶液の研磨液を用いて、シリコンウェーハの表面を鏡面研磨する。水溶性高分子をアルカリ性水溶液に添加したので、摩擦係数を低下させ、鏡面研磨されたウェーハ表層部に発生する加工起因のLPDの密度を低減でき、LPD密度が低いエピタキシャルシリコンウェーハを製造できる。しかも、鏡面研磨されたウェーハ表面に発生する表面粗さを小さくでき、表面粗さ品質に優れたエピタキシャルシリコンウェーハを提供できる。

(もっと読む)

デバイスのためのガリウム及び窒素含有超薄型エピタキシャル構造のための高速成長方法及び構造

ガリウム及び窒素含有材料の高速成長のための方法が記載される。本方法は、バルクガリウム及び窒素含有基板を提供することを含んでいる。第1の厚さの第1のエピタキシャル材料が、好ましくは擬似形態的プロセスによって、基板上に形成される。本方法は、第1の層上に第2のエピタキシャル層をも形成し、これによってスタック構造がもたらされる。スタック構造は、約2ミクロン未満の全体厚さで構成される。 (もっと読む)

炭化シリコン膜の製造方法

【課題】良好な膜質であり所望の導電型や導電性に制御された炭化シリコン膜を低コストで効率よく製造する方法を提供する。

【解決手段】本発明の炭化シリコン膜の製造方法は、不純物領域を有する炭化シリコン膜の製造方法である。表層にシリコン膜16aを有する基板11のシリコン膜16aを炭化処理して、炭化された膜を含んだ炭化シリコン膜13を形成する工程を有する。不純物領域になる部分のシリコン膜を炭化処理する前に、この部分に不純物を注入する。

(もっと読む)

半導体薄膜素子の製造方法並びに半導体ウエハ、及び、半導体薄膜素子

【課題】Si結晶層上に半導体素子を備えたSi以外の半導体単結晶層を備えた半導体薄膜素子の製造方法並びに半導体ウエハ、及び、半導体薄膜素子を提供する。

【解決手段】Si(111)基板(第1の基板)101の表面にバッファ層102と半導体単結晶層103とを順次形成する第1の工程と、半導体単結晶層101aとバッファ層102aとSi(111)基板の所定の厚さ部分102bとを含む分離島150を形成する第2の工程と、分離島の表面を覆う被覆層200を形成する第3の工程と、被覆層をマスクに前記Si(111)基板をSi(111)面に沿ってエッチングして剥離する第4の工程と、分離島の剥離面を別の基板(第2の基板)201の表面に接合する第5の工程とを備える。

(もっと読む)

半導体装置の製造方法

【課題】 格子定数が異なる複数種類の半導体素子を同一の基板上に混載することが可能な半導体装置の製造方法を提供する。

【解決手段】 半導体装置の製造方法は、シリコン基板21の一部に絶縁膜22を形成し、シリコン基板21と絶縁膜22上にアモルファスSiGe層23を形成し、シリコン基板を熱処理し、アモルファスSiGe層23を絶縁膜22上に横方向に固相若しくは液相成長させて結晶化し、シリコン基板22と絶縁膜22上に格子定数が後に形成される材料層の格子定数に整合されたSiGe層23bを形成する。

(もっと読む)

基板から分離された窒化ガリウムの膜をエピタキシーにより製造する方法

【課題】本発明は、欠陥密度レベルの減少した、エピタキシーによる窒化ガリウム膜の製造に関する。それは、GaNのエピタキシャル付着により窒化ガリウム(GaN)膜を製造するための方法に関する。

【解決手段】本発明は、それが少なくとも1ステップのエピタキシャル横方向成長を含んでなり、それがGaN基板への直接的イオン注入による脆化でその基板からGaN層の一部を分離させるステップを含んでなることで特徴付けられる。本発明は、上記方法で得られる膜、並びに該窒化ガリウム膜を備えた光電子および電子部品にも関する。

(もっと読む)

貼り合わせ基板の製造方法

【課題】接合強度を十分に維持できると共に、短時間で分離することができる、貼り合わせ基板の製造方法を提供する。

【解決手段】この貼り合わせ基板の製造方法は、III族窒化物半導体基板及び第1支持基板のうち少なくとも一方上に、表面粗さRrmsが0.1〜10000nmの表面を有する第1緩衝膜を形成する工程と、第1緩衝膜を介して、第1支持基板にIII族窒化物半導体基板を貼り合わせる工程とを含む。

(もっと読む)

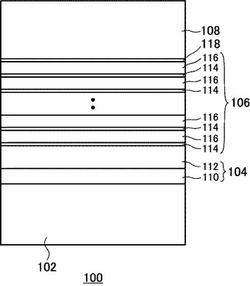

半導体素子

【課題】バッファ層を介した電極間のリーク電流を抑制した半導体素子を提供する。

【解決手段】本半導体素子は、基板10に形成された第1のAlXGa1−XN層14a及び第1のAlXGa1−XN層14aよりAl組成Xの大きい第2のAlXGa1−XN層14bが交互に積層して形成された超格子バッファ層14を有する。そして、第1のAlXGa1−XN層14a及び第2のAlXGa1−XN層14bのAl組成Xは共に0.3より大きく、かつ第1のAlXGa1−XN層14a及び第2のAlXGa1−XN層14bのAl組成Xの差は0より大きく0.6より小さい。この構成によれば、バッファ層を介したリーク電流を低減することができる。

(もっと読む)

3次元集積回路装置及びその製造方法

【課題】ガラス基板上に薄膜半導体層を形成した3次元集積回路装置を提供する。

【解決手段】ガラス基板11上に、単結晶もしくは準単結晶の2層の薄膜半導体層13,16が層間絶縁層14を介して積層され、2層の薄膜半導体層13,16は、下層の第1層の薄膜半導体層13と上層の第2層の薄膜半導体層16とが異なる材料であり、2層の薄膜半導体層13,16が、層間絶縁層14に形成された開口内を埋めて形成された、エピタキシャル層15によって接続され、エピタキシャル層15の表面部は、第2層の薄膜半導体層16と同じ材料の層であり、第1層の薄膜半導体層13及び第2層の薄膜半導体層16のうち、1層以上に能動素子Tr21,Tr22が形成されている3次元集積回路装置10を構成する。

(もっと読む)

1 - 20 / 54

[ Back to top ]