Fターム[5F152MM08]の内容

再結晶化技術 (53,633) | 半導体素子等への用途 (2,408) | 発光素子 (415)

Fターム[5F152MM08]の下位に属するFターム

Fターム[5F152MM08]に分類される特許

1 - 20 / 51

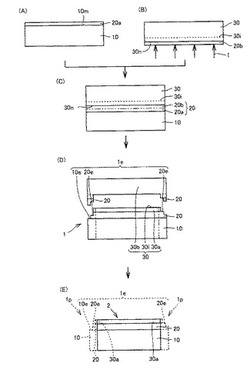

III族窒化物複合基板の製造方法

【課題】支持基板とIII族窒化物層との接合が良好なIII族窒化物複合基板の製造方法を提供する。

【解決手段】本III族窒化物複合基板の製造方法は、目標とする基板径より大きい径の主面10mを有する支持基板10と、目標とする基板径より大きい径の主面30nを有しその主面30nから所定の深さの位置にイオン注入領域30iが形成されたIII族窒化物基板30とを、中間層20を介在させて貼り合わせ、III族窒化物基板30をイオン注入領域30iにおいてIII族窒化物層30aと残りのIII族窒化物基板30bとに分離することにより、支持基板10上に中間層20を介在させてIII族窒化物層30aが接合された第1のIII族窒化物複合基板1を形成し、第1のIII族窒化物複合基板1の外周部を除去することにより目標とする基板径に等しい径の主面を有する第2のIII族窒化物複合基板2を得る。

(もっと読む)

半導体装置、半導体基板、半導体装置の製造方法、及び半導体基板の製造方法

【課題】エピタキシャル層に残存する転位の数を少なくする。

【解決手段】第2エピタキシャル層200は、第1エピタキシャル層100上にエピタキシャル成長している。第1エピタキシャル層100は、エピタキシャル成長層110及び欠陥層120を有している。欠陥層120は、エピタキシャル成長層110の上、かつ、第1エピタキシャル層100の表層に位置している。欠陥層120の欠陥密度は、5×1017cm−2以上である。欠陥層120を突き抜けた欠陥は、第2エピタキシャル層200の内部でループを形成している。

(もっと読む)

III族窒化物エピタキシャル基板およびその製造方法

【課題】デバイス化の工程で割れが発生することを抑制することが可能なIII族窒化物エピタキシャル基板およびその製造方法を提供する。

【解決手段】本発明のIII族窒化物エピタキシャル基板10は、Si基板11と、該Si基板11と接する初期層14と、該初期層14上に形成され、Al組成比が0.5超え1以下のAlGaNからなる第1層15A1(15B1)およびAl組成比が0超え0.5以下のAlGaNからなる第2層15A2(15B2)を順次有する積層体を複数組有する超格子積層体15と、を有し、前記第2層のAl組成比が、前記基板から離れるほど漸減することを特徴とする。

(もっと読む)

半導体基板上での逆相境界の無いIII−V化合物半導体材料およびその製造方法

【課題】逆相境界(APB)の無いIII−V化合物半導体材料およびその製造方法を提供する。

【解決手段】III−V化合物半導体材料の製造方法は、a){001}配向を有する第1半導体材料からなる基板と、基板の上に位置し、これと接触する絶縁層と、絶縁層内に、少なくとも部分的に基板を露出させる凹部領域を用意する工程と、b)凹部領域において露出基板の上に位置し、これと接触するバッファ層を形成する工程工程と、c)バッファ層の表面を粗面化するために、熱処理を印加する工程とを含み、バッファ層が、熱処理の印加後に二重ステップ表面を有する丸み形状をなし、d)凹部領域を、バッファ層の二重ステップ表面の上に位置し、これと接触するIII−V化合物半導体材料で少なくとも部分的に充填する工程をさらに含む。

(もっと読む)

レーザリフトオフ装置

【課題】基板上に形成された材料層に割れを生じさせることなく、レーザリフトオフ処理を短時間に行うことを可能とすること。

【解決手段】基板1と前記材料層2との界面で前記材料層を前記基板から剥離させるため、基板1上に材料層2が形成されたワーク3に対し、基板1側からマスク44を介してレーザ光を照射する。レーザ光はマスク44により複数の小面積のレーザ光に分割され、ワーク上に互いに離間した複数の照射領域が形成される。また隣り合う照射領域は互いに離間し、各照射領域の端部と、隣接する照射領域の、ワークの相対的移動方向に対して平行方向に伸びる端部とは、ワークが移動するに従って順次に重畳するように配列され、上記各照射領域の端部は隣接する照射領域の端部と互いに重畳する。これにより、基板上に形成された材料層に割れを生じさせることなく、材料層を基板から確実に剥離させることができる。

(もっと読む)

積層体の製造方法、III族窒化物単結晶自立基板の製造方法、および、積層体

【課題】III族窒化物単結晶が積層された積層体を冷却したとしても、該積層体の反り(結晶軸の歪み)が低減できる製造方法を提供する。

【解決手段】ベース基板/第1のIII族窒化物単結晶層/第1の非単結晶層からなる積層基板を形成する工程、積層基板からベース基板を除去する工程、第1のIII族窒化物単結晶層上にIII族窒化物単結晶をエピタキシャル成長させて第2のIII族窒化物単結晶層を形成する工程、第2のIII族窒化物単結晶層上に、第2の非単結晶層を形成する工程、を含む積層体の製造方法。

(もっと読む)

GaN系半導体エピタキシャル基板の製造方法

【課題】異種基板上にGaN系半導体を成長させることにより発生する貫通転位を低減し、低転位密度(例えば、105/cm2以下)のGaN系半導体をエピタキシャル成長させることができるGaN系半導体エピタキシャル基板の製造方法を提供する。

【解決手段】異種材料からなる成長用基板(例えばNGO基板)上にGaN系半導体をエピタキシャル成長させる際に、成長用基板上に、第1GaN系半導体層をエピタキシャル成長させ(第1工程)、第1GaN系半導体層における転位発生部分にエッチピットを形成し(第2工程)、エッチピットにSi3N4膜を選択的に形成し(第3工程)、Si3N4膜上に第2GaN系半導体層をエピタキシャル成長させる(第4工程)。

(もっと読む)

エピタキシャル構造、その形成方法、および、それを含むデバイス

半導体基板、半導体デバイスおよび半導体基板の製造方法

【課題】中間層としてGe結晶を用いる場合の化合物半導体へのGe原子の混入を抑制する。

【解決手段】ベース基板と、ベース基板上に形成された第1結晶層と、第1結晶層を被覆する第2結晶層と、第2結晶層に接して形成された第3結晶層とを備え、第1結晶層が、ベース基板における第1結晶層と接する面と面方位が等しい第1結晶面、及び、第1結晶面と異なる面方位を有する第2結晶面を有し、第2結晶層が、第1結晶面と面方位が等しい第3結晶面、及び、第2結晶面と面方位が等しい第4結晶面を有し、第3結晶層が、第3結晶面及び第4結晶面のそれぞれの少なくとも一部に接しており、第1結晶面に接する領域における第2結晶層の厚みに対する第2結晶面に接する領域における第2結晶層の厚みの比が、第3結晶面に接する領域における第3結晶層の厚みに対する第4結晶面に接する領域における第3結晶層の厚みの比よりも大きい半導体基板を提供する。

(もっと読む)

発光素子および発光素子の製造方法

【課題】本発明は、信頼性が向上し、発光構造物のクラック及びひび割れなどの損傷を防止し、発光効率を向上させる発光素子の製造方法を提供するためのものである。

【解決手段】本発明に従う発光素子の製造方法は、多数のチップ領域及びアイソレーション領域を含む基板の上に多数の化合物半導体層を形成するステップと、前記各チップ領域に発光構造物を形成し、前記アイソレーション領域に緩衝構造物を形成するために前記化合物半導体層をエッチングするステップと、前記発光構造物及び前記緩衝構造物の上に伝導性支持部材を形成するステップと、レーザリフトオフ工程を用いて前記基板を除去するステップと、前記発光構造物を分離するステップと、を含み、前記緩衝構造物は前記発光構造物から離隔する。

(もっと読む)

半導体装置の製造方法

【課題】格子定数が異なる複数種類の半導体素子やスピン機能素子を同一の基板上の同一の層上に混載することが可能な半導体装置の製造方法を提供しようとする。

【解決手段】シリコン基板上に絶縁膜を形成する工程と、前記絶縁膜に開口部を設け、前記シリコン基板の一部を露出させる工程と、前記露出したシリコン基板及び前記絶縁膜上にGeを含むアモルファスの第1の半導体層を形成する工程と、前記第1の半導体層を第1の方向に延伸した構造に加工する工程と、前記第1の方向に延伸した第1の半導体層に熱処理を加えて、前記開口部から離れるにしたがってSiの濃度が減少する第1のSi1-xGex(0≦x≦1)層を形成する工程と、を含む。

(もっと読む)

半導体基板、電子デバイス及び半導体基板の製造方法

【課題】シリコン基板上の一部の領域に形成する3族窒化物半導体の結晶性を高める製造方法を提供する。

【解決手段】表面がシリコン結晶であるベース基板102と、シリコン結晶上の一部の領域に形成されたSixGe1−xC(0≦x<1)エピタキシャル結晶104と、SixGe1−xC(0≦x<1)エピタキシャル結晶104上に形成された3族窒化物半導体結晶106とを含む半導体基板100を提供する。一例として、当該半導体基板100は、シリコン結晶上に形成され、かつ、シリコン結晶を露出する開口110を有し、結晶の成長を阻害する阻害体108をさらに含み、SixGe1−xC(0≦x<1)エピタキシャル結晶104は、開口110の内部に形成されている。

(もっと読む)

半導体基板、半導体デバイスおよび半導体基板の製造方法

【課題】単一のシリコン基板上に種類の異なる半導体結晶層をエピタキシャル成長させる場合に、表面の平坦性を向上し、半導体デバイスの信頼性を高める。

【解決手段】第1窪みおよび第2窪みが形成されたシリコン結晶を表面に有するベース基板と、第1窪みの内部に形成され、露出されている第1のIVB族半導体結晶と、第2窪みの内部に形成された第2のIVB族半導体結晶と、第2窪みの内部の第2のIVB族半導体結晶上に形成され、露出されているIII−V族化合物半導体結晶とを備える半導体基板を提供する。

(もっと読む)

シリコン半導体基板の製造方法

【課題】単結晶炭化シリコン層からなる半導体基板を製造する技術に関し、特にシリコン基板の表層部がさらに応力緩和炭化シリコン層を有する半導体基板を製造する技術を提供する。

【解決手段】下記のステップ:(1)シリコン半導体基板を用意し(2)シリコン基板内に炭素イオンを注入してケイ素と炭素の混在した炭素含有層を形成するステップと(3)基板を熱処理して炭素含有層を応力緩和炭化シリコン膜層と酸化膜キャップを形成するステップと(4)酸化膜キャップを除去するステップと(5)第2の酸化膜キャップを形成するステップと(6)応力緩和炭化シリコン膜層と第2の酸化膜キャップとの間のシリコン層に炭素イオンを注入して、ケイ素と炭素の混在した炭素含有層を形成するステップと(7)基板を熱処理して炭素含有層を結晶成長炭化ケイ素膜層とするステップと(8)基板の表面に形成された酸化膜キャップを除去するステップを順次実施する。

(もっと読む)

半導体発光素子の製造方法

【課題】基板上に、面内と周縁部の膜厚の均一な塗布膜を形成することを目的とする。

【解決手段】単結晶ウエハ1と半導体層4と、その間の結晶格子の不整合を緩和するバッファ層3を備えた半導体基板の製造方法であって、前記単結晶ウエハの外周端部1aを被覆材2で被覆した後、前記バッファ層3を前記単結晶ウエハ1の一面側に形成する工程と、前記被覆材2を取り除いた後、前記半導体層4を前記バッファ層3上の一面側に形成すると共に、前記単結晶ウエハ1の外周端部1aから前記半導体層4の外周部4bにかけて前記半導体層4の構成材料からなる堆積物4aを堆積させる工程と、前記半導体層4上に塗布液をスピンコート法により塗布する工程と、を具備してなることを特徴とする半導体基板の製造方法を提供する。

(もっと読む)

半導体素子の製造方法

【課題】 半導体層のエッチング時間の短縮化が望まれている。

【解決手段】 第1の膜及び半導体膜がこの順番に形成された積層基板の前記半導体膜の上に、マスクパターンを形成する。マスクパターンをエッチングマスクとして、半導体膜をエッチングすることにより、凹部を形成するとともに、凹部の底面の一部の領域に第1の膜が露出し、他の領域には、半導体膜の残渣が残っている状態でエッチングを停止させる。凹部の底面に露出した第1の膜を厚さ方向及び横方向にエッチングすることにより、残渣の下に空洞を形成する。積層基板を浸漬させた液体に超音波を印加することにより、空洞の上に残留している残渣を積層基板から脱離させる。

(もっと読む)

光デバイス、半導体基板、光デバイスの製造方法、および半導体基板の製造方法

【課題】高品質な光デバイスをシリコン基板上にモノリシックに形成する。

【解決手段】シリコンを含むベース基板と、ベース基板上に設けられた複数のシード結晶と、複数のシード結晶に格子整合または擬格子整合する複数の3−5族化合物半導体とを備え、複数の3−5族化合物半導体のうちの少なくとも1つに、供給される駆動電流に応じて光を出力する発光半導体、または光の照射を受けて光電流を発生する受光半導体を含む光電半導体が形成されており、複数の3−5族化合物半導体のうち、光電半導体を有する3−5族化合物半導体以外の少なくとも1つの3−5族化合物半導体にヘテロ接合トランジスタが形成されている光デバイスを提供する。

(もっと読む)

半導体装置の製造方法

【課題】 格子定数が異なる複数種類の半導体素子を同一の基板上に混載することが可能な半導体装置の製造方法を提供する。

【解決手段】 半導体装置の製造方法は、シリコン基板21の一部に絶縁膜22を形成し、シリコン基板21と絶縁膜22上にアモルファスSiGe層23を形成し、シリコン基板を熱処理し、アモルファスSiGe層23を絶縁膜22上に横方向に固相若しくは液相成長させて結晶化し、シリコン基板22と絶縁膜22上に格子定数が後に形成される材料層の格子定数に整合されたSiGe層23bを形成する。

(もっと読む)

半導体薄膜素子の製造方法並びに半導体ウエハ、及び、半導体薄膜素子

【課題】Si結晶層上に半導体素子を備えたSi以外の半導体単結晶層を備えた半導体薄膜素子の製造方法並びに半導体ウエハ、及び、半導体薄膜素子を提供する。

【解決手段】Si(111)基板(第1の基板)101の表面にバッファ層102と半導体単結晶層103とを順次形成する第1の工程と、半導体単結晶層101aとバッファ層102aとSi(111)基板の所定の厚さ部分102bとを含む分離島150を形成する第2の工程と、分離島の表面を覆う被覆層200を形成する第3の工程と、被覆層をマスクに前記Si(111)基板をSi(111)面に沿ってエッチングして剥離する第4の工程と、分離島の剥離面を別の基板(第2の基板)201の表面に接合する第5の工程とを備える。

(もっと読む)

半導体基板、半導体基板の製造方法、電子デバイス、および電子デバイスの製造方法

【課題】結晶薄膜を有する半導体基板の設計および上記結晶薄膜の膜質および膜厚の制御を容易にできる半導体基板を提供する。

【解決手段】ベース基板と、ベース基板上に、一体にまたは分離して設けられ、化合物半導体の結晶成長を阻害する阻害層とを備え、阻害層は、ベース基板まで阻害層を貫通する複数の開口を有する複数の第1開口領域を有し、複数の第1開口領域のそれぞれは、内部に同一の配置で設けられた複数の第1開口を含み、複数の第1開口の一部は、電子素子が形成されるべき第1化合物半導体が設けられている第1素子形成開口であり、複数の第1開口の他の一部は、電子素子が形成されない第1ダミー開口である半導体基板を提供する。

(もっと読む)

1 - 20 / 51

[ Back to top ]