Fターム[5F152MM18]の内容

再結晶化技術 (53,633) | 半導体素子等への用途 (2,408) | エピタキシャルウエハ (260)

Fターム[5F152MM18]に分類される特許

1 - 20 / 260

半導体加工用部品の処理方法およびそれにより形成された部品

シリコン基板、これを採用したエピ構造体及びシリコン基板の製造方法

炭化珪素半導体装置の製造方法

エピタキシャルウェーハとその製造方法

シリコン単結晶膜およびその製造方法

【課題】薄層化された自立性のシリコン単結晶膜を提供し、また、剥離時の熱処理温度を格段に低減することができる新たなシリコン単結晶膜の形成方法を提供する。

【解決手段】シリコン単結晶膜6は、Siの含有率が、90原子%以上であり、厚みが、50μm以下であり、自立性がある。

(もっと読む)

β−Ga2O3系基板の製造方法、及び結晶積層構造体の製造方法

【課題】還元雰囲気や不活性ガス雰囲気下におけるドナー濃度の変化が抑えられたβ−Ga2O3系基板の製造方法、及び還元雰囲気や不活性ガス雰囲気下において品質のばらつきの小さい高品質な結晶膜をエピタキシャル成長させることのできる結晶積層構造体の製造方法を提供する。

【解決手段】IV族元素を含むβ−Ga2O3系結晶からβ−Ga2O3系基板を切り出す工程を含み、還元雰囲気及び不活性ガス雰囲気の少なくともいずれか一方を含む雰囲気下でのアニール処理が、前記β−Ga2O3系基板を切り出す前の前記β−Ga2O3系結晶、又は切り出された前記β−Ga2O3系基板に施される、β−Ga2O3系基板の製造方法を提供する。

(もっと読む)

窒化物半導体ウェーハ、窒化物半導体装置及び窒化物半導体結晶の成長方法

【課題】シリコン基板上に形成した、転位及びクラックの少ない窒化物半導体ウェーハ、窒化物半導体装置及び窒化物半導体結晶の成長方法を提供する。

【解決手段】実施形態によれば、シリコン基板と、その上に順次設けられた、下側歪緩和層、中間層、上側歪緩和層及び機能層と、を有する窒化物半導体ウェーハが提供される。中間層は、第1下側層と、第1ドープ層と、第1上側層と、を含む。第1下側層は、下側歪緩和層の上に設けられ下側歪緩和層の格子定数よりも大きい格子定数を有する。第1ドープ層は、第1下側層の上に設けられ第1下側層の格子定数以上の格子定数を有し1×1018cm−3以上1×1021cm−3未満の濃度であり第1下側層よりも高い濃度で不純物を含有する。第1上側層は、第1ドープ層の上に設けられ第1ドープ層の格子定数以上で第1下側層の格子定数よりも大きい格子定数を有する。

(もっと読む)

半導体基板および半導体基板の製造方法

【課題】シリコンウェハ等のベース基板上方に窒化物半導体からなる半導体結晶層を形成する場合に、当該半導体結晶層の転位密度を低減する。

【解決手段】ベース基板、接着層、バッファ層および活性層を有し、前記ベース基板、前記接着層、前記バッファ層および前記活性層がこの順に位置し、前記ベース基板の前記接着層と接する領域にSiが存在し、前記接着層、前記バッファ層および前記活性層が、窒化物半導体からなる半導体基板であって、前記バッファ層が、第1結晶層と第2結晶層が交互に複数積層された積層構造体であり、前記第1結晶層が、AlmGa1−mN、(但し0≦m≦1)で表される結晶からなり、前記第2結晶層が、AlnGa1−nN、(但し0≦n≦1、m>n)で表される結晶からなり、前記第1結晶層の格子緩和度が、前記第2結晶層の格子緩和度より大きい半導体基板を提供する。

(もっと読む)

エピタキシャルウェーハとその製造方法

【課題】歪み層形成に供されるウェーハで転位発生に対して耐性が高いエピタキシャルウェーハを提供する。

【解決手段】シリコンエピタキシャル層表面の酸素濃度が1.0×1017〜12×1017atoms/cm3とされてなるエピタキシャルウェーハの製造方法であって、酸素濃度設定熱処理の処理温度Xと処理時間Yとが、処理温度Xが800℃〜1400℃の範囲、処理時間Yが180min以下で、かつ、

Y ≧ 1.21×1010 exp(−0.0176X)

の関係を満たすように設定される。

(もっと読む)

半導体基板の製造方法及び半導体装置

【課題】基板に形成された窒化ガリウム系半導体で形成された半導体層におけるドーパント濃度がばらつくと、半導体層を用いた半導体装置の特性がばらつくので、半導体層におけるドーパント濃度のばらつきが抑えられた層を有する半導体基板を得る。

【解決手段】基板に、窒化ガリウム系半導体で形成された半導体層を形成する半導体層形成段階と、半導体層に、中性子線を照射して、半導体層に含まれるガリウム原子の一部をゲルマニウム原子に変換する照射段階と、を備える半導体基板の製造方法を提供する。

(もっと読む)

III族窒化物層複合基板の製造方法

【課題】支持基板上にIII族窒化物層が接合していない欠陥領域がない高品質のIII族窒化物層複合基板の製造方法を提供する。

【解決手段】本III族窒化物層複合基板の製造方法は、III族窒化物基板20にイオン注入領域20iを形成し、III族窒化物基板20のイオンが注入された側の主表面側および支持基板10の主表面側の少なくともひとつに接合用前駆体層40を形成し、III族窒化物基板20と支持基板10とを接合用前駆体層40を介在させて接合し、接合用前駆体層40をリフローさせることにより接合層50を形成し、III族窒化物基板20をイオン注入領域20iにおいて分離してIII族窒化物層21と残りのIII族窒化物基板22とにすることにより、支持基板10の主表面上に接合層40を介在させてIII族窒化物層21が接合されたIII族窒化物層複合基板1を形成する。

(もっと読む)

III族窒化物エピタキシャル基板およびその製造方法

【課題】デバイス化の工程で割れが発生することを抑制することが可能なIII族窒化物エピタキシャル基板およびその製造方法を提供する。

【解決手段】本発明のIII族窒化物エピタキシャル基板10は、Si基板11と、該Si基板11と接する初期層14と、該初期層14上に形成され、Al組成比が0.5超え1以下のAlGaNからなる第1層15A1(15B1)およびAl組成比が0超え0.5以下のAlGaNからなる第2層15A2(15B2)を順次有する積層体を複数組有する超格子積層体15と、を有し、前記第2層のAl組成比が、前記基板から離れるほど漸減することを特徴とする。

(もっと読む)

窒化物半導体エピタキシャル基板及び窒化物半導体デバイス

【課題】低転位であり、クラック発生を抑制できるIII族窒化物半導体層を有する窒化物

半導体エピタキシャル基板及び窒化物半導体デバイスを提供する。

【解決手段】基板上にAlを含むIII族窒化物半導体のバッファ層を介して成長した、C

面を表面とするIII族窒化物半導体層を有する窒化物半導体エピタキシャル基板であって

、前記バッファ層が、その表面にインバージョンドメインを有する。

(もっと読む)

ヘテロエピタキシャル層を備えた半導体ウェハ及び前記ウェハの製造方法

【課題】バウの制御のためだけでなく、SiGeエピタキシャル層の品質を改善するために、特にSi基板上に堆積されたSiGe層のクロスハッチ及び表面ラフネスを低減するために、背面層によって形成された応力を用いる適切な解決策を提供する。

【解決手段】第1の面及び第2の面を有する基板10、前記基板の第1の面に堆積された完全に又は部分的に緩和されたヘテロエピタキシャル層20、及び前記基板の第2の面に堆積された応力相殺層30を有する、半導体ウェハ。

(もっと読む)

二元及び三元金属カルコゲニド材料ならびにその製造方法及び使用方法

【課題】本発明は化学蒸着(CVD)プロセス、原子層堆積(ALD)プロセス又は湿式溶液プロセスを用いた金属カルコゲニドの合成を開示する。

【解決手段】オルガノシリルテルル又はオルガノシリルセレンの、求核性置換基を有する一連の金属化合物とのリガンド交換反応により、金属カルコゲニドが生成される。この化学的性質を用いて、相変化メモリデバイス及び光電池デバイスのためのゲルマニウム−アンチモン−テルル(GeSbTe)膜及びゲルマニウム−アンチモン−セレン(GeSbSe)膜又はその他のテルル及びセレンをベースとする化合物を堆積させる。

(もっと読む)

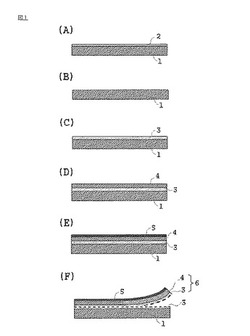

多層膜構造体及びその形成方法

【課題】新規な多層膜構造体及びその形成方法を提供すること。

【解決手段】半導体素子用の多層膜構造体の形成方法であって、シリコンを含む基板上に、ゲルマニウム錫混晶からなる半導体層を形成する半導体層形成工程と、前記半導体層上に表面保護層を形成する表面保護層形成工程と、前記半導体層に熱処理を施すことにより、前記ゲルマニウム錫混晶と前記シリコンを含む基板との固相反応を進め、シリコンゲルマニウム錫混晶からなる半導体歪印加層を形成する半導体歪印加層形成工程と、前記表面保護層を除去する除去工程と、前記半導体歪印加層の上方に、前記除去工程後に、歪半導体層を積層する積層工程とを含むことを特徴とする多層膜構造体の形成方法。

(もっと読む)

ダイアモンド基板上炭化珪素並びに関連するデバイス及び方法

【課題】ワイドバンドギャップ材料内に、接合温度低下、動作中の高電力密度化、及び定格電力密度における信頼性向上を達成する高電力デバイスを形成する。

【解決手段】SiC層10にSiO2層を形成し、次いで、熱伝導率を高めるためにダイアモンド層11を形成する。そして、SiC層10の厚さを低減し、ダイアモンド層11及びSiC層10の向きを逆にしてダイアモンド11を基板とする。次いで、SiC層10上に、バッファ層16、ヘテロ構造層14及び15を形成する。

(もっと読む)

電界効果トランジスタ用窒化物半導体エピタキシャルウェハ、窒化物半導体系電界効果トランジスタ、及び電界効果トランジスタ用窒化物半導体エピタキシャルウェハの製造方法

【課題】電子のトラッピング現象を緩和すると共に、ヘキサゴナル欠陥の発生を抑制可能な窒化物半導体エピタキシャルウェハの製造方法を提供する。

【解決手段】基板1上に核生成層2を形成し、その核生成層2上に第一の窒化物半導体層3を形成し、その第一の窒化物半導体層3上に、前記第一の窒化物半導体層3よりも電子親和力の小さい第二の窒化物半導体層4を形成する窒化物半導体エピタキシャルウェハ10の製造方法において、前記第一の窒化物半導体層3を形成する際の成長温度が、前記第二の窒化物半導体層4を形成する際の成長温度よりも低くするものである。

(もっと読む)

シリコン−オン−インシュレーター構造及びバルク基板に対するSiGeの堆積

【課題】欠陥を最小限としながら、SiGe−オン−インシュレーター構造を製造するため及びシリコン上に歪み緩和SiGe層を製造するための方法を提供する。

【解決手段】アモルファスSiGe層600が、トリシラン及びGeH4からCVDによって、ドーパントの1以下のモノレイヤー上に堆積される。これらのアモルファスSiGe層600は、融解または固相エピタキシー(SPE)プロセスによってシリコン上に再結晶される。融解プロセスは、好ましくは、全体のゲルマニウム含量を希釈するようなゲルマニウムの拡散も引き起こし、そして絶縁体の上層のシリコン500を実質的に消費する。SPEプロセスは、下地のシリコン500中へのゲルマニウムの拡散を用いてまたは用いずに実際され得、従って、SOI及び従来の半導体基板に適用可能である。

(もっと読む)

エピタキシャル基板およびその製造方法、固体撮像素子およびその製造方法、電子情報機器

【課題】高温熱処理による不純物拡散を抑制することにより、基板性能に要求されるオーバーフロードレイン機能とゲッタリング能力を向上できて、製造工程も複雑化しない。

【解決手段】シリコン基板1の表面側に、砒素(またはアンチモン)がイオン注入されて高濃度N型層3が形成され、この高濃度N型層3上にエピタキシャル層4がエピタキシャル成長して形成されている。これによって、砒素(As)の拡散係数がリン(P)に比べて小さいことから、従来手法によるリンドープ基板に比べて製造工程における熱処理による不純物拡散(プロファイル拡散)を大幅に抑制する。

(もっと読む)

1 - 20 / 260

[ Back to top ]