Fターム[5F152NN02]の内容

再結晶化技術 (53,633) | 基板材料(積層体を基板として扱う場合も含む) (4,266) | 半導体 (1,904) | 4族 (1,311)

Fターム[5F152NN02]の下位に属するFターム

Fターム[5F152NN02]に分類される特許

1 - 20 / 64

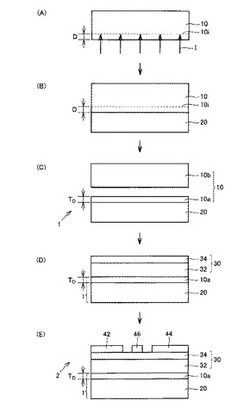

GaN薄膜貼り合わせ基板およびその製造方法、ならびにGaN系高電子移動度トランジスタおよびその製造方法

【課題】バッファリーク電流およびゲートリーク電流が抑制された高性能のHEMTを提供する。

【解決手段】本GaN薄膜貼り合わせ基板の製造方法は、GaNバルク結晶10の主表面から0.1μm以上100μm以下の深さの面10iへの平均注入量が1×1014cm-2以上3×1017cm-2以下の水素イオン注入工程と、水素イオン注入されたGaNバルク結晶10の上記主表面へのGaNと化学組成が異なる異組成基板20の貼り合わせ工程と、GaNバルク結晶10の熱処理によりGaNバルク結晶10を水素イオンが注入された深さの面10iにおいて分離することによる異組成基板20上に貼り合わされたGaN薄膜10aの形成工程と、を含む。GaN系HEMTの製造方法は、上記GaN薄膜貼り合わせ基板1のGaN薄膜10a上への少なくとも1層のGaN系半導体層30の成長工程を含む。

(もっと読む)

ダイアモンド基板上炭化珪素並びに関連するデバイス及び方法

【課題】ワイドバンドギャップ材料内に、接合温度低下、動作中の高電力密度化、及び定格電力密度における信頼性向上を達成する高電力デバイスを形成する。

【解決手段】SiC層10にSiO2層を形成し、次いで、熱伝導率を高めるためにダイアモンド層11を形成する。そして、SiC層10の厚さを低減し、ダイアモンド層11及びSiC層10の向きを逆にしてダイアモンド11を基板とする。次いで、SiC層10上に、バッファ層16、ヘテロ構造層14及び15を形成する。

(もっと読む)

歪吸収中間層遷移モジュールを有するIII族窒化物半導体構造

【課題】歪み吸収III族窒化物中間層モジュールを有する種々の半導体構造を提供する。

【解決手段】基板および当該基板の上方の第一遷移本体を有する。前記第一遷移本体は、第一表面において第一の格子パラメータを有し、前記第一表面とは反対側の第二表面において第二の格子パラメータを有する。前記典型的な実施では、遷移モジュール等の第二遷移本体をさらに有し、この第二遷移本体は前記第一遷移本体の前記第二表面に重層する下表面においてより小さい格子パラメータを有し、前記第二遷移本体の上表面においてより大きい格子パラメータを有し、前記第二遷移本体の上方のIII族窒化物半導体層も同様である。前記第二遷移本体は2以上の遷移モジュールからなっていてもよく、各遷移モジュールは2以上の中間層を有していてもよい。前記第一遷移本体および前記第二遷移本体は前記半導体構造の歪みを減少させる。

(もっと読む)

エピタキシャル成長用基板およびエピタキシャル成長用基板の製造方法

【課題】平坦性、結晶性および配向性に優れ、厚さ方向の熱伝導率が高く放熱性に優れたエピタキシャル成長用基板およびその製造方法を提供する。

【解決手段】炭素基板の少なくとも一方の主表面に、算術平均表面粗さRaが0.05μm以下で、表面粗さの最大値Ryが0.5μm以下であり、X線回折法による(0002)面のロッキングカーブの半値幅が1.5度以下であり、ラマンスペクトルにおけるGバンドのピーク強度に対するDバンドのピーク強度の比が0.01以下である高結晶グラファイト層を形成してなることを特徴とするエピタキシャル成長用基板である。

(もっと読む)

窒化ガリウム系半導体基板の製造方法

【課題】貫通ピットの無い窒化ガリウム系半導体基板を安価に得ることができる窒化ガリウム系半導体基板の製造方法を提供する。

【解決手段】窒化ガリウム系半導体基板の製造方法であって、気相成長装置内に、表面にピット25を生じた窒化ガリウム系半導体層20を有する基板を準備する第1の工程と、前記気相成長装置内で、前記窒化ガリウム系半導体層20上に、非晶質又は多結晶のIII族窒化物のピット埋込層30を形成して前記ピット25を埋める第2の工程と、前記ピット埋込層30を研磨により除去して前記窒化ガリウム系半導体層20の表面を露出させる第3の工程と、を具備する。

(もっと読む)

半導体基板

【課題】単結晶構造を有するSiCから作られた領域と、炭化珪素から作られた支持部とを有し、かつ両者の界面の電気抵抗を低減することができる半導体基板を提供する。

【解決手段】支持部30は炭化珪素から作られている。少なくとも1つの層11の各々は第1および第2の面B1、F1を有する。第1の面B1は支持部30に支持されている。少なくとも1つの層11の各々は第1および第2の領域61、62を有する。第1の領域61は単結晶構造の炭化珪素から作られている。第2の領域62はグラファイトから作られている。第2の面F1は第1の領域61によって形成された面を有する。第1の面B1は、第1の領域61によって形成された面と、第2の領域62によって形成された面との各々を有する。

(もっと読む)

半導体複合体構造を形成する方法

【課題】 パターン付けされたシリコン・オン・インシュレータ(SOI)/シリコン・オン・ナッシング(SON)複合構造体を多孔性Si技術によって形成すること。

【解決手段】 パターン付けされたSOI/SON複合構造体及びその形成方法を提供する。SOI/SON複合構造体においては、パターン付けされたSOI/SON構造体が、Siオーバーレイヤと半導体基板の間に挟まれる。パターン付けされたSOI/SON複合構造体を形成する方法は、SOI及びSON構造が共に形成される共有加工処理ステップを含む。本発明はまた、埋没導電/SON構造体を含む複合構造体の形成方法、及び、埋没ボイド平面だけを有する複合構造体の形成方法を提供する。

(もっと読む)

ダイヤモンド半導体素子およびその製造方法

【課題】ダイヤモンド薄膜内に存在する結晶欠陥、不純物等を減少させ、高品質なダイヤモンド薄膜を作製可能なダイヤモンド薄膜作製方法を提供すること。

【解決手段】ダイヤモンドが安定な高圧力下でアニールを行う。これにより、結晶中に含まれる格子欠陥等が回復、除去され、ダイヤモンド結晶薄膜を高品質化する事ができる。「(ダイヤモンドが)安定な、安定に」とは、ダイヤモンドがグラファイト化せずにダイヤモンドの状態を保つ状態を指す。ダイヤモンドが安定にアニール出来る領域内でアニールを行う温度(アニール温度、とも呼ぶ)Tおよびアニールを行う圧力(アニール圧力、とも呼ぶ)Pが決定される。この領域は、図21に示される、P>0.71+0.0027TまたはP=0.71+0.0027Tを満たし、なおかつP≧1.5GPaの領域である。このような領域は、図21中の斜線部分である。

(もっと読む)

GaN基板およびその製造方法、GaN層接合基板の製造方法、ならびに半導体デバイスの製造方法

【課題】加工しろが小さく一様な加工が容易なGaN基板およびその製造方法、かかるGaN基板を用いたGaN層接合基板および半導体デバイスの製造方法を提供する。

【解決手段】本GaN基板20は、第1領域20jと、第1領域20jに比べてGa/N組成比が高い第2領域20iとを含み、第2領域20iは、一方の主面20mから所定の深さDを中心に深さD−ΔDから深さD+ΔDまで広がり、深さDにおけるGa/N組成比と第1領域20jの深さD+4ΔD以上の深さにおけるGa/N組成比との差が、深さD+ΔDにおけるGa/N組成比と第1領域20jの深さD+4ΔD以上の深さにおけるGa/N組成比との差の3倍であり、第2領域20iのGa/N組成比が、第1領域20jの深さD+4ΔD以上の深さにおけるGa/N組成比に対して1.05以上である。

(もっと読む)

ダイヤモンド半導体素子およびその製造方法

【課題】最大発振周波数fmaxを高くしてダイヤモンド電界効果トランジスタの特性を大きく向上させ、かつ電圧降下を小さく抑えることにより実用レベルに到達させること。

【解決手段】「ソース・ゲート電極間隔dSG、ゲート・ドレイン電極間隔dGDを狭くすること」と「ソース電極の厚さtS、ドレイン電極の厚さtDを厚くすること」とを両立させるために、ソース電極およびドレイン電極を、エッチング溶液を用いてエッチングする層とレジストを用いてリフトオフする層とに分けて形成する。これにより電極の逆メサ部を小さくすることができるため、ソース電極とゲート電極との間隔を小さくして最大発振周波数fmaxを上げ、かつソース電極およびドレイン電極の厚みを厚くして電圧降下を小さく抑えることができる。

(もっと読む)

ダイヤモンド薄膜及びその製造方法

【課題】積層欠陥及び貫通転位の密度が十分に低いダイヤモンド薄膜構造とその製造方法を提供する。

【解決手段】本発明のダイヤモンド薄膜構造は、基板と、基板の主方位面の一部を覆うマスク材と、基板の主方位面の表面からエピタキシャル成長するダイヤモンド薄膜とで構成されるダイヤモンド薄膜構造であって、ダイヤモンド薄膜は、マスク材の上に形成され、ダイヤモンド薄膜の結晶方位は基板の結晶方位とそろっており、基板の主方位面の一部にストライプ状の溝が形成され、マスク材は、ストライプ状の溝を覆うように配置されている。

(もっと読む)

III族窒化物半導体層接合基板およびIII族窒化物半導体デバイスの製造方法

【課題】III族窒化物半導体層の欠落部分の少ない高品質のIII族窒化物半導体層接合基板の製造方法を提供する。

【解決手段】本III族窒化物半導体接合基板の製造方法は、主表面20mに現れる表面異状領域22の大きさおよび密度が所定の範囲内のIII族窒化物半導体基板20を準備する工程と、III族窒化物半導体基板20の主表面20m側にイオンを注入する工程と、III族窒化物半導体基板20の主表面20mに異種基板10を接合する工程と、III族窒化物半導体基板20をイオンが注入された領域20iで分離して異種基板10に接合したIII族窒化物半導体層20aを形成することにより、III族窒化物半導体層接合基板1を得る工程と、を備える。

(もっと読む)

積層構造物

【課題】過度に複雑な、成長後の加工処理(post growth processing)が最小限に抑えられ、第2のいっそう厚い層と比べて非常に異なる特性を有する薄いダイヤモンド層を有する構造体を合成することが可能となる方法を提供する。

【解決手段】互いに接触している少なくとも2つの層(20,22)であって、各々の層は広いバンドギャップの材料でできており、各々の層は少なくとも1つの性質が他の層と相違している前記少なくとも2つの層(20,22)を有する生成物を製造する方法。

(もっと読む)

III族窒化物半導体層貼り合わせ基板およびその製造方法、ならびにIII族窒化物半導体デバイス

【課題】光の取り出し効率が高い半導体デバイスが得られる安価なIII族窒化物半導体層貼り合わせ基板およびその製造方法ならびにIII族窒化物半導体デバイスを提供する。

【解決手段】本III族窒化物半導体層貼り合わせ基板1は、III族窒化物半導体層20aと、III族窒化物半導体層20aと化学組成が異なる基礎基板10と、が貼り合わせられた基板であって、III族窒化物半導体層20aは、基礎基板10と接合する主面20nを有し主面20nに平行な2次元方向に屈折率が周期的に変化するフォトニック結晶構造層20pを含む。

(もっと読む)

立方晶炭化ケイ素単結晶薄膜の製造方法及び半導体装置

【課題】低コストの立方晶炭化ケイ素(3C−SiC)単結晶薄膜を得るための立方晶炭化ケイ素単結晶薄膜の製造方法及び半導体装置を提供する。

【解決手段】立方晶炭化ケイ素単結晶薄膜の製造方法において、基板101の表面に犠牲層102を形成する第1の工程と、犠牲層の表面に少なくとも表面層が立方晶構造である立方晶半導体層103を形成する第2の工程と、立方晶半導体層の表面に立方晶炭化ケイ素単結晶層104を形成する第3の工程と、犠牲層をエッチング除去して、立方晶半導体層と立方晶炭化ケイ素単結晶層との積層体を剥離する第4の工程とを備える。

(もっと読む)

半導体薄膜素子の製造方法並びに半導体ウエハ、及び、半導体薄膜素子

【課題】Si結晶層上に半導体素子を備えたSi以外の半導体単結晶層を備えた半導体薄膜素子の製造方法並びに半導体ウエハ、及び、半導体薄膜素子を提供する。

【解決手段】Si(111)基板(第1の基板)101の表面にバッファ層102と半導体単結晶層103とを順次形成する第1の工程と、半導体単結晶層101aとバッファ層102aとSi(111)基板の所定の厚さ部分102bとを含む分離島150を形成する第2の工程と、分離島の表面を覆う被覆層200を形成する第3の工程と、被覆層をマスクに前記Si(111)基板をSi(111)面に沿ってエッチングして剥離する第4の工程と、分離島の剥離面を別の基板(第2の基板)201の表面に接合する第5の工程とを備える。

(もっと読む)

ダイヤモンド薄膜及びその製造方法

【課題】積層欠陥及び貫通転位の密度が十分に低いダイヤモンド薄膜構造とその製造方法を提供する。

【解決手段】基板101と、基板101の主方位面の一部を覆うマスク材102と、基板101の主方位面の表面からエピタキシャル成長するダイヤモンド薄膜103とで構成されるダイヤモンド薄膜構造であって、ダイヤモンド薄膜103は、マスク材102の上に形成され、ダイヤモンド薄膜103の結晶方位は基板101の結晶方位とそろっている。ダイヤモンド基板101に存在する貫通転位104aは、マスク材102で覆われていない部分のダイヤモンド基板101の主方位面を介してダイヤモンド薄膜103まで貫通するが、貫通転位104bは、マスク材102によってダイヤモンド薄膜103への伝播が遮られるため、ダイヤモンド薄膜103の貫通転位密度は低下し、結晶性が向上する。

(もっと読む)

ダイヤモンド半導体及び作製方法

【課題】従来技術と比較して、室温で十分に高いキャリア濃度を有するダイヤモンド半導体及び作製方法を提供すること。

【解決手段】ダイヤモンド基板11(図5(a))上にマイクロ波プラズマCVD装置を用い、メタンを反応ガスとし、基板温度700℃でダイヤモンド薄膜12を1ミクロン積層する(図5(b))。ダイヤモンド薄膜12にイオン注入装置を用い、不純物1(VI族又はII族元素)を打ち込む(図5(c))。その後、不純物2(III族又はV族元素)を打ち込んだが(図5(d))、注入条件は、打ち込んだ不純物がそれぞれ表面から0.5ミクロンの厚さの範囲内で、1×1017cm-3となるようにシミュレーションにより決定した。その後、2種類のイオンが注入されたダイヤモンド薄膜13をアニールすることにより(図5(e))、イオン注入された不純物の活性化を行い、ダイヤモンド半導体薄膜15を得た(図5(f))。

(もっと読む)

複合基板、エピタキシャル基板、半導体デバイス及び複合基板の製造方法

【課題】支持基板上に高品質の窒化物半導体層が形成された複合基板、エピタキシャル基板、半導体デバイス及び複合基板の製造方法を提供する。

【解決手段】複合基板は、支持基板と、窒化物半導体層と、支持基板と窒化物半導体層との間に設けられた接合層とを備える。窒化物半導体層の転位密度は、1×108個/cm2以下である。窒化物半導体層は、接合層側の第1面と、第1面とは反対側の第2面とを有している。第1面における転位密度と第2面における転位密度との差が1×102個/cm2以下である。

(もっと読む)

III族窒化物半導体層貼り合わせ基板の製造方法

【課題】III族窒化物半導体層の結晶性が高いIII族窒化物半導体層貼り合わせ基板を提供する。

【解決手段】本III族窒化物半導体層貼り合わせ基板の製造方法は、III族窒化物半導体基板20の一方の主表面20mから所定の深さDの領域に水素およびヘリウムの少なくともいずれかのイオンIを注入する工程と、III族窒化物半導体基板20の主表面20mに異種基板10を貼り合わせる工程と、III族窒化物半導体基板20をイオンIが注入された領域20iにおいて分離することにより、III族窒化物半導体層貼り合わせ基板1を得る工程と、III族窒化物半導体層貼り合わせ基板1を、窒素含有ガスNの雰囲気下700℃以上でアニールする工程と、を備える。

(もっと読む)

1 - 20 / 64

[ Back to top ]