Fターム[5F152NN04]の内容

再結晶化技術 (53,633) | 基板材料(積層体を基板として扱う場合も含む) (4,266) | 半導体 (1,904) | 4族 (1,311) | Ge、SiGe (150)

Fターム[5F152NN04]に分類される特許

1 - 20 / 150

グラフェン構造の製造方法及びこれを用いた半導体装置の製造方法

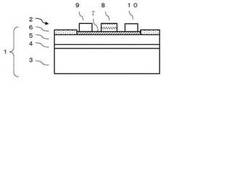

【課題】所望の位置にグラフェン膜を有するグラフェン構造及びこれを用いた半導体装置を提供する。

【解決手段】所定の基材3上において、炭素含有層4と、少なくともケイ素を含む炭素化合物層5とを順次に積層し、その上に絶縁膜層6を形成した後、絶縁膜層の一部をエッチングにより取り除いた基板に対してアニーリングを実施し、絶縁膜の除去部にのみグラフェン膜7を形成したグラフェン構造1を形成し、これを用いて表面にショットキー電極8、およびオーミック電極9,10を形成させて半導体装置2を作製する。

(もっと読む)

複合基板の製造方法

【課題】結晶成長用基板に形成した半導体結晶層を転写先基板に転写する場合の犠牲層のエッチング速度を高める。

【解決手段】半導体結晶層形成基板の上に犠牲層および半導体結晶層を順に形成するステップと、犠牲層の一部が露出するように半導体結晶層をエッチングし、半導体結晶層を複数の分割体に分割するステップと、転写先基板に接することとなる半導体結晶層形成基板側の第1表面と、第1表面に接することとなる転写先基板側の第2表面と、が向かい合うように、半導体結晶層形成基板と転写先基板とを貼り合わせるステップと、半導体結晶層形成基板および転写先基板をエッチング液に浸漬して犠牲層をエッチングし、半導体結晶層を転写先基板側に残した状態で、転写先基板と半導体結晶層形成基板とを分離するステップと、を有し、前記半導体結晶層が、GexSi1−x(0<x≦1)からなる、複合基板の製造方法を提供する。

(もっと読む)

複合基板の製造方法および複合基板

【課題】結晶成長用基板に形成した半導体結晶層を転写先基板に転写する場合の犠牲層のエッチング速度を高める。

【解決手段】半導体結晶層形成基板の上に犠牲層および半導体結晶層を順に形成し、転写先基板に接することとなる前記半導体結晶層形成基板の第1表面と、前記第1表面に接することとなる前記転写先基板の第2表面と、が向かい合うように、前記半導体結晶層形成基板と前記転写先基板とを貼り合わせ、前記半導体結晶層形成基板および前記転写先基板の全部または一部をエッチング液に浸漬して前記犠牲層をエッチングし、前記半導体結晶層を前記転写先基板側に残した状態で、前記転写先基板と前記半導体結晶層形成基板とを分離する。ここで、前記転写先基板が、非可撓性基板と有機物層とを有し、前記有機物層の表面が、前記第2表面であるものとする。

(もっと読む)

薄膜製造方法、それを用いた半導体デバイスの製造方法およびそれらに用いられる半導体薄膜部品

【課題】高品質な半導体薄膜を製造する薄膜製造方法を提供する。

【解決手段】薄膜製造方法は、a−Si膜等の半導体薄膜を第1の基板上に堆積する工程S1と、第1の基板をエッチングして第1の基板と半導体薄膜との間に中空部を形成する工程S2と、半導体薄膜に第2の基板を接触させる工程S3と、半導体薄膜に第2の基板を押し付け、または半導体薄膜が溶融する強度を有するレーザ光を半導体薄膜に照射する工程S4と、第1の基板を半導体薄膜から引き離す工程S5とを備える。

(もっと読む)

半導体デバイス、半導体基板、半導体基板の製造方法および半導体デバイスの製造方法

【課題】単一基板上にソース・ドレインを同一工程で同時形成したIII−V族半導体のnMISFETおよびIV族半導体のpMISFETのソース・ドレイン領域抵抗または接触抵抗を小さくする。

【解決手段】第1半導体結晶層に形成された第1チャネル型の第1MISFETの第1ソースおよび第1ドレインと、第2半導体結晶層に形成された第2チャネル型の第2MISFETの第2ソースおよび第2ドレインが、同一の導電性物質からなり、当該導電性物質の仕事関数ΦMが、数1および数2の少なくとも一方の関係を満たす。

(数1) φ1<ΦM<φ2+Eg2

(数2) |ΦM−φ1|≦0.1eV、かつ、|(φ2+Eg2)−ΦM|≦0.1eV

ただし、φ1は、N型半導体結晶層の電子親和力、φ2およびEg2は、P型半導体結晶層の電子親和力および禁制帯幅。

(もっと読む)

半導体装置および半導体装置の駆動方法

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供する。

【解決手段】酸化物半導体を用いた書き込み用トランジスタ162、トランジスタ162と異なる半導体材料を用いた読み出し用トランジスタ160及び容量素子164を含む不揮発性のメモリセルにおいて、メモリセルへの書き込みは、書き込み用トランジスタ162をオン状態とすることにより、書き込み用トランジスタ162のソース電極(またはドレイン電極)と、容量素子164の電極の一方と、読み出し用トランジスタ160のゲート電極とが電気的に接続されたノードに電位を供給した後、書き込み用トランジスタ162をオフ状態とすることにより、ノードに所定量の電荷を保持させることで行う。また、読み出し用トランジスタ160として、pチャネル型トランジスタを用いて、読み出し電位を正の電位とする。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供する。

【解決手段】ワイドギャップ半導体、例えば酸化物半導体を含むメモリセルを用いて構成された半導体装置であって、メモリセルからの読み出しのために基準電位より低い電位を出力する機能を有する電位切り替え回路を備えた半導体装置とする。ワイドギャップ半導体を用いることで、メモリセルを構成するトランジスタのオフ電流を十分に小さくすることができ、長期間にわたって情報を保持することが可能な半導体装置を提供することができる。

(もっと読む)

半導体の製造方法及び半導体装置

【課題】複雑な工程を経ることなく、通常の半導体製造装置を使用して、低コストで、半導体装置の、低電圧動作、高集積性を実現する。

【解決手段】次の工程(1)〜(5)で半導体装置を製造する。(1)シリコン結晶製の半導体支持基板の表面を洗浄し、酸化被膜を除去して、結晶面を露出させる工程、(2)該結晶面上に高誘電率非晶質薄膜を低温で堆積する工程、(3)該高誘電率非晶質薄膜の結晶化開始温度よりも低いプレアニール温度で該高誘電率非晶質薄膜をプレアニールする工程、(4)該半導体支持基板を選択的に急速加熱することにより該高誘電率非晶質薄膜内部に基板界面から該薄膜表面方向に向けて温度が低くなる急峻な温度勾配を形成することにより該高誘電率非晶質薄膜を結晶化して、エピタキシャル薄膜を形成する工程、(5)該エピタキシャル薄膜の上面に半導体結晶の配向膜を形成する工程を有する。

(もっと読む)

歪吸収中間層遷移モジュールを有するIII族窒化物半導体構造

【課題】歪み吸収III族窒化物中間層モジュールを有する種々の半導体構造を提供する。

【解決手段】基板および当該基板の上方の第一遷移本体を有する。前記第一遷移本体は、第一表面において第一の格子パラメータを有し、前記第一表面とは反対側の第二表面において第二の格子パラメータを有する。前記典型的な実施では、遷移モジュール等の第二遷移本体をさらに有し、この第二遷移本体は前記第一遷移本体の前記第二表面に重層する下表面においてより小さい格子パラメータを有し、前記第二遷移本体の上表面においてより大きい格子パラメータを有し、前記第二遷移本体の上方のIII族窒化物半導体層も同様である。前記第二遷移本体は2以上の遷移モジュールからなっていてもよく、各遷移モジュールは2以上の中間層を有していてもよい。前記第一遷移本体および前記第二遷移本体は前記半導体構造の歪みを減少させる。

(もっと読む)

III/V族半導体材料を形成する方法及びそのような方法を用いて形成された半導体構造体

【課題】内部の欠陥数がより少なく且つ/又は減少したIII/V族半導体材料を形成する方法、並びに欠陥数がより少なく且つ/又は減少したそのようなIII/V族半導体材料を含む半導体構造体及び素子が必要である。

【解決手段】三元III族窒化物材料を形成する方法は、チャンバー内で基板上に三元III族窒化物材料をエピタキシャル成長させるステップを含む。エピタキシャル成長は、チャンバー中の窒素前駆体の分圧と1つ又は複数のIII族前駆体の分圧との比較的に高い比を含む前駆体ガス混合物をチャンバー内に準備するステップを含む。少なくとも一部は比較的に高い比のため、三元III族窒化物材料の層は、小さいVピット欠陥をその中に含む高い最終厚さに成長させることができる。そのような三元III族窒化物材料の層を含む半導体構造体をそのような方法を用いて作製する。

(もっと読む)

表面を改善する方法

【課題】本発明は、少なくとも部分的にシリコンを含む、半導体基板の表面を改善する方法に関する。本発明の目的は、少なくとも部分的にシリコンからなる半導体基板の表面を改善する方法であって、高い表面品質を有する半導体基板が提供されるよう、半導体基板の内部または表面にある欠陥を完全に修復することができる方法を提供することである。

【解決手段】この目的は、前記半導体基板の表面にある少なくとも1つのホール内での選択的エピタキシャル堆積を含んだ堆積ステップを含む、上述のタイプの方法によって解決される。

(もっと読む)

半導体記憶装置

【課題】メモリデータを外部回路を用いずに、コピーを行う半導体記憶装置を提供することを課題とする。

【解決手段】複数のメモリセルの第一端子が共通接続されたビット線と、ビット線に接続され、読み出し時にビット線を特定の電位にプリチャージするプリチャージ回路と、メモリセルから読み出したデータ、もしくはメモリセルへの書き込みデータを一時的に保持する容量素子を有するデータ保持回路と、データ保持回路で保持しているデータの反転データをビット線に出力する反転データ出力回路とを有し、反転データ出力回路は、データ保持回路で保持しているデータの反転データの出力を制御する手段を有する構成とする。

(もっと読む)

半導体基板上での逆相境界の無いIII−V化合物半導体材料およびその製造方法

【課題】逆相境界(APB)の無いIII−V化合物半導体材料およびその製造方法を提供する。

【解決手段】III−V化合物半導体材料の製造方法は、a){001}配向を有する第1半導体材料からなる基板と、基板の上に位置し、これと接触する絶縁層と、絶縁層内に、少なくとも部分的に基板を露出させる凹部領域を用意する工程と、b)凹部領域において露出基板の上に位置し、これと接触するバッファ層を形成する工程工程と、c)バッファ層の表面を粗面化するために、熱処理を印加する工程とを含み、バッファ層が、熱処理の印加後に二重ステップ表面を有する丸み形状をなし、d)凹部領域を、バッファ層の二重ステップ表面の上に位置し、これと接触するIII−V化合物半導体材料で少なくとも部分的に充填する工程をさらに含む。

(もっと読む)

単結晶半導体膜の作製方法、電極の作製方法

【課題】簡単かつコストの低い方法で単結晶半導体膜を得る方法を提供する。

【解決手段】単結晶半導体基板10の表面に、気相エピタキシャル成長法によって圧縮応力を有する単結晶半導体膜11を形成し、単結晶半導体膜11の表面に、引張応力を有する膜(例えば、熱硬化性樹脂膜12)を形成し、単結晶半導体膜11に力を加える剥離工程によって、単結晶半導体基板10と単結晶半導体膜11とを分離して、単結晶半導体膜を得る。なお、熱硬化性樹脂膜12としては、例えば、エポキシ樹脂膜を用いることが可能である。

(もっと読む)

半導体薄膜基板および半導体薄膜基板を用いた半導体装置の作製方法

【課題】一層の半導体層から膜厚の異なる半導体層を有する半導体薄膜基板を提供することを目的の一とする。または、半導体薄膜基板を適用した半導体装置を提供することを目的の一とする。

【解決手段】基板上に半導体層を形成し、半導体層を加工して第1の島状半導体層および第2の島状半導体層を形成し、第1の島状半導体層にレーザー照射を行うことにより第1の島状半導体層を溶融させ、第1の島状半導体層から第2の島状半導体層より膜厚が厚い第3の島状半導体層を形成する、半導体薄膜基板の作製方法である。

(もっと読む)

単結晶3C−SiC基板の製造方法およびそれによって得られた単結晶3C−SiC基板

【課題】エピタキシャル成長過程において発生する表面欠陥を大幅に減少させることができ、後工程を簡略化しながら半導体デバイスとしての品質を確保できる単結晶3C−SiC基板の製造方法を提供する。

【解決手段】ベース基板上にエピタキシャル成長によって単結晶3C−SiC層を形成させる単結晶3C−SiC基板の製造方法であって、

上記単結晶3C−SiC層を、平坦性の高い表面とその中に点在する表面ピットからなる表面状態となるよう形成する第1の成長段階と、

上記第1の成長段階で得られた単結晶3C−SiC層を、脱離律速の領域において表面の上記表面ピットを埋めるようさらにエピタキシャル成長させる第2の成長段階とを行う。

(もっと読む)

発光素子および発光素子の製造方法

【課題】本発明は、信頼性が向上し、発光構造物のクラック及びひび割れなどの損傷を防止し、発光効率を向上させる発光素子の製造方法を提供するためのものである。

【解決手段】本発明に従う発光素子の製造方法は、多数のチップ領域及びアイソレーション領域を含む基板の上に多数の化合物半導体層を形成するステップと、前記各チップ領域に発光構造物を形成し、前記アイソレーション領域に緩衝構造物を形成するために前記化合物半導体層をエッチングするステップと、前記発光構造物及び前記緩衝構造物の上に伝導性支持部材を形成するステップと、レーザリフトオフ工程を用いて前記基板を除去するステップと、前記発光構造物を分離するステップと、を含み、前記緩衝構造物は前記発光構造物から離隔する。

(もっと読む)

フィン型FETを有する半導体装置およびその製造方法

【課題】横方向延伸を減少し、素子サイズを小さくすることができる半導体装置を提供する。

【解決手段】半導体基板上に延伸し、STI領域を間に有する第1および第2のフィンを形成する。STI領域の上面と第1および第2のフィンの上面の間の寸法を第1の高さとし、STI領域の第1と第2のフィンとの間の間隙内に誘電材料を堆積し、STI領域の上面上に上面を有して、誘電材料の上面と第1および第2のフィンの上面との寸法を第2の高さとし、第2の高さは、第1の高さより低くなるように誘電材料を堆積した後、第1および第2のフィン上でそれぞれ誘電体の上方に、第1および第2のフィン延伸をエピタキシャル成長で形成する。

(もっと読む)

半導体複合体構造を形成する方法

【課題】 パターン付けされたシリコン・オン・インシュレータ(SOI)/シリコン・オン・ナッシング(SON)複合構造体を多孔性Si技術によって形成すること。

【解決手段】 パターン付けされたSOI/SON複合構造体及びその形成方法を提供する。SOI/SON複合構造体においては、パターン付けされたSOI/SON構造体が、Siオーバーレイヤと半導体基板の間に挟まれる。パターン付けされたSOI/SON複合構造体を形成する方法は、SOI及びSON構造が共に形成される共有加工処理ステップを含む。本発明はまた、埋没導電/SON構造体を含む複合構造体の形成方法、及び、埋没ボイド平面だけを有する複合構造体の形成方法を提供する。

(もっと読む)

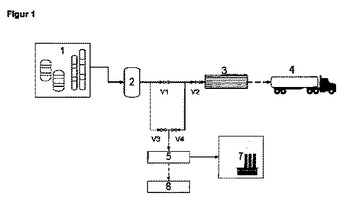

シラン及びゲルマンの純度を間接的に決定するための固有抵抗の使用及び相応する方法

本発明は、固有抵抗を測定するための機器を使用してシラン及びゲルマンの純度を間接的に決定するための方法に関する。本発明はさらに、固有抵抗を測定するための機器を使用した品質管理を含めた、シラン又はゲルマンの工業的製造及び/又は充填のためのプラントに関する。  (もっと読む)

(もっと読む)

1 - 20 / 150

[ Back to top ]