Fターム[5F152NQ11]の内容

再結晶化技術 (53,633) | 動作層、活性層、素子構成層の材料 (2,604) | 結晶性 (160)

Fターム[5F152NQ11]の下位に属するFターム

Fターム[5F152NQ11]に分類される特許

1 - 19 / 19

半導体ウェハ

【課題】高い結晶品質を有する、多様な材料からなる、完全に緩和した、又は歪んだ半導体層を積層するために絶縁体層の格子寸法を調整するための高い柔軟性を許容する、SOI構造の作製のための基板を提供する。

【解決手段】実質的にシリコンからなる単結晶基板ウェハ1、電気絶縁性材料を含み、かつ2nm〜100nmの厚さを有する第一非晶質中間層2、立方晶系Ia−3結晶構造と、(Me12O3)-1-x(Me22O3)xの組成と、基板ウェハの材料の格子定数と0%〜5%異なる格子定数とを有する単結晶第一酸化物層3を示される順序で含むことを特徴とする半導体ウェハ。

(もっと読む)

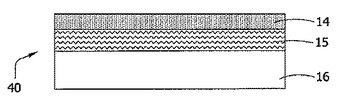

III族窒化物複合基板

【課題】支持基板と酸化物膜との接合強度および酸化物膜とIII族窒化物層との接合強度が高いIII族窒化物複合基板を提供する。

【解決手段】本III族窒化物複合基板1は、支持基板10と酸化物膜20とIII族窒化物層30aとを含み、支持基板10は多結晶で形成され、III族窒化物層30aは少なくともc軸方向に配向しているIII族窒化物結晶で形成され、酸化物膜20は不純物が添加され、不純物の濃度は、酸化物膜20において支持基板10側の第1主面20sからIII族窒化物層30a側の第2主面20tにかけて膜厚方向で変化し、第1主面20sにおける不純物の濃度は第2主面20tにおける不純物の濃度よりも高い。

(もっと読む)

酸化物半導体膜及び半導体装置

【課題】より安定した電気的特性の酸化インジウム亜鉛でなる酸化物半導体膜を提供する。また、当該酸化物半導体膜を用いることにより、半導体装置に安定した電気的特性を付与し、信頼性の高い半導体装置を提供する。

【解決手段】酸化インジウム亜鉛でなる酸化物半導体膜において、当該酸化物半導体膜は、a−b面が酸化物半導体膜表面に概略平行である六方晶の結晶構造と、a−b面が該酸化物半導体膜表面に概略平行である菱面体晶の結晶構造と、を有する酸化物半導体膜である。

(もっと読む)

半導体ウェハ及びその製造法

【課題】高い結晶品質を有する、多様な材料からなる、完全に緩和した、又は歪んだ半導体層を積層するために絶縁体層の格子寸法を調整するための高い柔軟性を許容する、SOI構造の作製のための基板を提供する。

【解決手段】実質的にシリコンからなる単結晶基板ウェハ1、電気絶縁性材料を含み、かつ2nm〜100nmの厚さを有する第一非晶質中間層2、立方晶系Ia−3結晶構造と、(Me12O3)-1-x(Me22O3)xの組成と、基板ウェハの材料の格子定数と0%〜5%異なる格子定数とを有する単結晶第一酸化物層3を示される順序で含むことを特徴とする半導体ウェハ。

(もっと読む)

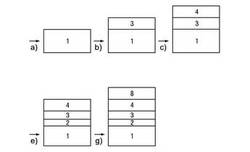

光起電力素子、TFT、及びi型半導体層の形成方法

【課題】 低コストで、優れた性能をもつシリコン系薄膜を提供するために、タクトタイムが短くて、高速の成膜速度で特性のすぐれたシリコン系薄膜と、それを含む半導体素子。さらにこのシリコン系薄膜を用いた密着性、耐環境性などに優れた半導体素子を提供することを目的とする。

【解決手段】 i型半導体層と前記i型半導体層の下地層である前記p型半導体層またはn型半導体層との界面領域であって前記i型半導体層と前記p型半導体層またはn型半導体層との界面から1.0nm以上20nm以下の界面領域の微結晶が(100)面に優先配向しており、前記i型半導体層の層厚方向における前記微結晶のエックス線または電子線による(220)面の回折強度の全回折強度に対する割合である(220)面の配向性が前記i型半導体層の下地層である前記p型半導体層又は前記n型半導体層側では小さく、前記下地層から離れるに伴って大きくなるように変化する。

(もっと読む)

微結晶半導体膜の作製方法、及び半導体装置の作製方法

【課題】結晶粒間に鬆がない緻密な結晶性半導体膜(例えば微結晶半導体膜)を作製する技術を提供することを目的とする。

【解決手段】プラズマCVD装置の反応室内における反応ガスの圧力を450Pa〜13332Paとし、当該プラズマCVD装置の第1の電極と第2の電極の間隔を1mm〜20mm、好ましくは4mm以上16mm以下として、前記第1の電極に60MHz以下の高周波電力を供給することにより、第1の電極および第2の電極の間にプラズマ領域を形成し、プラズマ領域を含む気相中において、結晶性を有する半導体でなる堆積前駆体を形成し、堆積前駆体を堆積させることにより、5nm以上15nm以下の結晶核を形成し、結晶核から結晶成長させることにより微結晶半導体膜を形成する。

(もっと読む)

半導体薄膜素子の製造方法並びに半導体ウエハ、及び、半導体薄膜素子

【課題】Si結晶層上に半導体素子を備えたSi以外の半導体単結晶層を備えた半導体薄膜素子の製造方法並びに半導体ウエハ、及び、半導体薄膜素子を提供する。

【解決手段】Si(111)基板(第1の基板)101の表面にバッファ層102と半導体単結晶層103とを順次形成する第1の工程と、半導体単結晶層101aとバッファ層102aとSi(111)基板の所定の厚さ部分102bとを含む分離島150を形成する第2の工程と、分離島の表面を覆う被覆層200を形成する第3の工程と、被覆層をマスクに前記Si(111)基板をSi(111)面に沿ってエッチングして剥離する第4の工程と、分離島の剥離面を別の基板(第2の基板)201の表面に接合する第5の工程とを備える。

(もっと読む)

立方晶炭化ケイ素単結晶薄膜の製造方法及び半導体装置

【課題】低コストの立方晶炭化ケイ素(3C−SiC)単結晶薄膜を得るための立方晶炭化ケイ素単結晶薄膜の製造方法及び半導体装置を提供する。

【解決手段】立方晶炭化ケイ素単結晶薄膜の製造方法において、基板101の表面に犠牲層102を形成する第1の工程と、犠牲層の表面に少なくとも表面層が立方晶構造である立方晶半導体層103を形成する第2の工程と、立方晶半導体層の表面に立方晶炭化ケイ素単結晶層104を形成する第3の工程と、犠牲層をエッチング除去して、立方晶半導体層と立方晶炭化ケイ素単結晶層との積層体を剥離する第4の工程とを備える。

(もっと読む)

半導体基板の製造方法

【課題】良好な立方晶の炭化珪素膜を形成可能な半導体基板の製造方法を提供すること。

【解決手段】シリコン基板11上にバッファ層12を形成する第1の工程と、バッファ層12上にシリコン膜15を形成する第2の工程と、シリコン膜15を炭化して炭化珪素膜13を形成する第3の工程と、を含み、バッファ層12は、シリコンの格子定数と炭化珪素膜13の格子定数との間の格子定数を有する金属酸化物で構成され、第3の工程は、炭化水素系ガスの雰囲気下で行われる。

(もっと読む)

窒化ガリウムウエハ

【課題】 これまで実在しなかった窒化ガリウムの自立した円形ウエハを実用的な形にして初めて提供すること。

【解決手段】 1016cm−3〜1020cm−3の濃度で酸素ドープされた六方晶系で{0001}面方位の窒化ガリウム単結晶よりなり透明であって独立し自立した円形のウエハであって方位を指定するフラット部を一つあるいは方位と表裏を示すフラット部を二つ付ける。周辺部を面取りすることも有用である。n型の導電性をしめす。

(もっと読む)

有機薄膜の製造方法

【課題】基板上に大面積の単結晶の有機薄膜を形成することができる有機薄膜の製造方法を提供する。

【解決手段】基板上に第1の有機分子からなる規則的な分子配列を有する第1の有機分子層を形成する工程と、前記第1の有機分子層の上にエピタキシャル成長する第2の有機分子層を形成する工程と、前記第1の有機分子層を昇華、蒸発あるいは溶解して前記第2の有機分子層から除去する工程を有する有機薄膜の製造方法。前記第1の有機分子がアントラセン、前記第2の有機分子がペンタセンであることが好ましい。

(もっと読む)

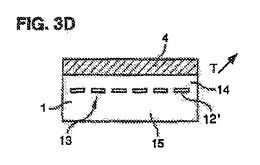

少なくとも1つの窒化材料層を有するハイブリッド基板の製造法

本発明は電子工学分野での応用を目的とする、少なくとも1つのIII/N型窒化材料層を具備してなるハイブリッド基板の製造法であって;六方単結晶の結晶構造を有するIII/N型窒化材料でできた原材基板(1)を選択する工程;前記基板内部に多数のナノ空隙(12)を生じさせて活性層(14)の境界となる脆弱領域(13)を作ることを目的として、前記窒化材料の「c」結晶軸に平行もしくは略平行な平面内にある「注入面」(10)と呼ばれる面の一つを通して、1×1016He+/cm2から1×1017He+/cm2のヘリウムイオンHe+を前記原材基板(1)に注入する工程;および、少なくとも前記ナノ空隙を空隙(12’)へと成長させることが可能な熱授受を含む授受からなる、活性層(14)を原材基板(1)から分離させることが可能な全エネルギー授受を施すことによって前記活性層(14)を移設する工程;からなることを特徴とする製造法に関する。  (もっと読む)

(もっと読む)

窒化物半導体素子の製造方法

【課題】結晶性の良い窒化物半導体よりなる窒化物半導体基板を用い裏面に電極を形成した発光素子、受光素子等の窒化物半導体素子を提供する。

【解決手段】窒化物半導体と異なる材料よりなる基板の上に、窒化物半導体を100μm以上の膜厚で成長させ、前記基板を除去することによって得られた窒化物半導体基板であり、該窒化物半導体基板の表面の凹凸差が±1μm以下になるまで表面研磨した研磨面に成長される。好ましくは、前記表面の凹凸差が±0.5μm以下である。前記窒化物半導体基板はn型不純物がドープされている。

(もっと読む)

半導体基板の製造方法および半導体基板

【課題】 2枚のウェーハの接合により、DSB構造を有する半導体基板を製造する場合において、接合界面を半導体基板側に残さないことによって、接合界面のボイド発生に起因する素子の歩留まり低下を解消することを可能とする半導体基板の製造方法および半導体基板を提供する。

【解決手段】 第1の半導体ウェーハ102表面に非晶質(アモルファス)半導体層120を形成する工程と、第2の半導体ウェーハ104表面に多孔質半導体層118を形成する工程と、非晶質半導体層120と多孔質半導体層118を重ね合わせた状態で、第1の半導体ウェーハ102と第2の半導体ウェーハ104とを接合する工程と、非晶質半導体層120を単結晶化する熱処理工程と、接合する工程において形成された半導体基板114を、多孔質半導体層118において分離する工程を有することを特徴とする半導体基板の製造方法および半導体基板。

(もっと読む)

歪み半導体基板の製造方法および歪みMOSFETの製造方法

【課題】歪み緩和バッファ層を設けることなく、結晶構造を有する半導体基板の表面に歪み半導体層を形成でき、したがって、簡単かつ低コストで歪み半導体基板を作製できる歪み半導体基板の製造方法を提供すること。

【解決手段】結晶構造を有する半導体基板の表面に絶縁膜を形成する(S1)。半導体基板の材料とは格子定数が異なる元素をその絶縁膜中にイオン注入する(S2)。その元素が絶縁膜中からはじき出されて半導体基板中に拡散して、その元素を要因とした歪みが半導体基板に生じるように熱処理を行う(S3)。

(もっと読む)

結晶成長方法及び結晶成長装置

【課題】 結晶成長方法及び結晶成長装置に関し、基板とエピタキシャル層との格子定数の差を、用いられる物質により一義的決定されることなく一定程度の範囲で任意に設定する。

【解決手段】 湾曲させた基板1上にエピタキシャル成長をさせる。

(もっと読む)

歪み補償の準安定化合物ベースヘテロ接合バイポーラトランジスタ

歪み補償原子種を置換配列することにより、例えば、SiGe NPN HNTの電子装置(100)へ、その場で添加した歪み補償の準安定化合物基部(107)を電子装置(100)に擬似格子整合を増大し統一するための方法。本発明は歪みSiGe、MOSアプリケーションのSi、垂直薄膜トランジスタ(VTFT)、および様々なその他の電子装置型などの、その他の電子装置の歪み層にも適用する。例えば、GaAs、InP、およびAlGaAsの、SiGe以外の化合物半導体から形成される装置も本願に記載する有益な工程に適している。  (もっと読む)

(もっと読む)

結晶化度が改善された歪シリコン層を有する歪シリコンオンインシュレータ(SSOI)構造

本発明は、一般に歪シリコンオンインシュレータ(SSOI)構造とその製造方法に関するものである。この方法は、歪シリコン層の歪を維持しつつその結晶化度を改善するための高温熱アニールを含む。  (もっと読む)

(もっと読む)

Ge微結晶核付き基板の作製方法及びGe微結晶核付き基板

【課題】 基板上に、成長の核となる微結晶を作製し、その粒径と密度を制御し、大粒径多結晶Si薄膜を作製できるGe微結晶核付き基板の作製方法及びGe微結晶核付き基板を提供する。

【解決手段】 電子工業用ガラス基板、石英ガラス基板、熱酸化したSiウェーハ又はSiO2膜付き基板の上に固相成長法により島状に独立したGe微結晶を形成し、次いで酸素エッチングによってGe微結晶の粒径と密度とを、300〜600℃の範囲のエッチング温度とエッチング時間とで制御する。前記基板の上に粒径が1〜40nmのGe微結晶を、密度が1×105〜1×107個/cm2となるように分散配置した。

(もっと読む)

1 - 19 / 19

[ Back to top ]