Fターム[5F152NQ13]の内容

再結晶化技術 (53,633) | 動作層、活性層、素子構成層の材料 (2,604) | 結晶性 (160) | 非晶質 (41)

Fターム[5F152NQ13]に分類される特許

1 - 20 / 41

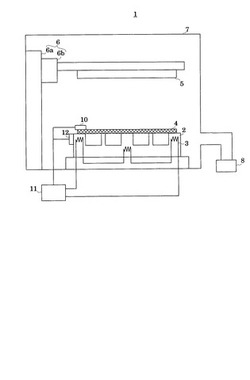

半導体膜蒸着装置および半導体膜蒸着方法

【課題】半導体膜の表面欠陥の発生を抑制する半導体膜蒸着装置および半導体膜蒸着方法を提供する。

【解決手段】

半導体原料を収容するるつぼ2と、るつぼ2と対向して基板5を支持する基板支持器6と、るつぼ2と基板5との間でるつぼ2の開口を覆って配置されるマスク4と、るつぼ2およびマスク4を加熱する加熱器3と、るつぼ2、基板支持器6、およびマスク4を収容する真空チャンバ7とを備える半導体膜蒸着装置。るつぼ2から飛散した半導体分子はマスク4内部を衝突しながら通過することで基板5上に表面欠陥が抑制された状態で成膜される。

(もっと読む)

薄膜トランジスタおよびその製造方法

【課題】 水分に起因するTFT特性の変化を抑制した薄膜トランジスタおよびその製造方法を提供する。

【解決手段】 本発明の薄膜トランジスタは、基板上に、少なくともゲート電極、ゲート絶縁膜、活性層、ソース電極、およびドレイン電極が設けられ、活性層上にソース電極およびドレイン電極が設けられたものである。活性層は、アモルファス酸化物半導体により構成されており、ゲート絶縁膜内に存在する第1の水分量が活性層に存在する第2の水分量よりも少ない。

(もっと読む)

微結晶シリコン膜の作製方法および薄膜トランジスタの作製方法

【課題】絶縁膜と微結晶シリコン膜との密着性を向上させた微結晶シリコン膜の作製方法を提供する。

【解決手段】絶縁膜55上に、後のプラズマ酸化等により完全に酸化される高さ(例えば0nmより大きく5nm以下)の微結晶シリコン粒、または後のプラズマ酸化等により完全に酸化される膜厚(例えば0nmより大きく5nm以下)の微結晶シリコン膜もしくはアモルファスシリコン膜を形成し、前記微結晶シリコン粒または前記微結晶シリコン膜もしくはアモルファスシリコン膜に酸素を含むプラズマ処理またはプラズマ酸化を施すことにより、前記絶縁膜上に酸化シリコン粒57aまたは酸化シリコン膜を形成し、前記酸化シリコン粒または前記酸化シリコン膜の上に微結晶シリコン膜59を形成する微結晶シリコン膜の作製方法である。

(もっと読む)

光起電力素子、TFT、及びi型半導体層の形成方法

【課題】 低コストで、優れた性能をもつシリコン系薄膜を提供するために、タクトタイムが短くて、高速の成膜速度で特性のすぐれたシリコン系薄膜と、それを含む半導体素子。さらにこのシリコン系薄膜を用いた密着性、耐環境性などに優れた半導体素子を提供することを目的とする。

【解決手段】 i型半導体層と前記i型半導体層の下地層である前記p型半導体層またはn型半導体層との界面領域であって前記i型半導体層と前記p型半導体層またはn型半導体層との界面から1.0nm以上20nm以下の界面領域の微結晶が(100)面に優先配向しており、前記i型半導体層の層厚方向における前記微結晶のエックス線または電子線による(220)面の回折強度の全回折強度に対する割合である(220)面の配向性が前記i型半導体層の下地層である前記p型半導体層又は前記n型半導体層側では小さく、前記下地層から離れるに伴って大きくなるように変化する。

(もっと読む)

半導体基板の作製方法及び光電変換装置の作製方法

【課題】低温での固相エピタキシャル成長法を用いて、結晶性の高いシリコン層を厚く形成した半導体基板を提供することを課題の一とする。その際、従来の気相エピタキシャル成長法と比べ、結晶成長速度を大きくすることを課題の一とする。

【解決手段】絶縁層を介してベース基板に設けられた単結晶シリコン層上に、堆積初期の一部で、単結晶シリコン層と結晶面の配列の揃った針状シリコン層が気相エピタキシャル成長するようにシリコン層を形成し、針状シリコン層を種結晶として、シリコン層の他部を固相エピタキシャル成長させて、単結晶及び前記結晶シリコン層の厚さが厚い半導体基板を作製する。

(もっと読む)

炭化珪素基板、半導体装置、炭化珪素基板の製造方法

【課題】炭化珪素基板を用いた半導体装置の製造コストの低減を実現可能な炭化珪素基板、半導体装置および炭化珪素基板の製造方法を提供する。

【解決手段】炭化珪素基板1は、炭化珪素からなるベース層10と、単結晶炭化珪素からなり、ベース層10上に配置され、ベース層10よりも不可避不純物の濃度が低いSiC層20と、炭化珪素からなり、ベース層10の、SiC層20とは反対側の主面10D上に形成され、ベース層10よりも不可避不純物の濃度が低い被覆層90とを備えている。

(もっと読む)

半導体薄膜基板および半導体薄膜基板を用いた半導体装置の作製方法

【課題】一層の半導体層から膜厚の異なる半導体層を有する半導体薄膜基板を提供することを目的の一とする。または、半導体薄膜基板を適用した半導体装置を提供することを目的の一とする。

【解決手段】基板上に半導体層を形成し、半導体層を加工して第1の島状半導体層および第2の島状半導体層を形成し、第1の島状半導体層にレーザー照射を行うことにより第1の島状半導体層を溶融させ、第1の島状半導体層から第2の島状半導体層より膜厚が厚い第3の島状半導体層を形成する、半導体薄膜基板の作製方法である。

(もっと読む)

半導体装置及びその製造方法

【課題】第1のコンタクトプラグのゲート電極への短絡を防止する。第1の不純物拡散層と第1のコンタクトプラグの接続抵抗、及び第1と第2のコンタクトプラグの接続抵抗を低減することにより、縦型MOSトランジスタのオン電流を増加させる。

【解決手段】シリコンピラー上部に、非晶質シリコン層及び単結晶シリコン層を形成する。次に、2度の選択エピタキシャル成長法により、シリコンピラー上に順に非晶質シリコン層、及び非晶質シリコンゲルマニウム層を形成する。この後、熱処理により、シリコンピラー上部に単結晶シリコン層を有する第1の不純物拡散層を形成すると同時に、シリコンピラー上に単結晶シリコン層及び多結晶シリコンゲルマニウム層を有する第1のコンタクトプラグを形成する。次に、第1のコンタクトプラグに接続されるように、金属から構成される第2のコンタクトプラグを形成する。

(もっと読む)

窒化ガリウム系半導体基板の製造方法

【課題】貫通ピットの無い窒化ガリウム系半導体基板を安価に得ることができる窒化ガリウム系半導体基板の製造方法を提供する。

【解決手段】窒化ガリウム系半導体基板の製造方法であって、気相成長装置内に、表面にピット25を生じた窒化ガリウム系半導体層20を有する基板を準備する第1の工程と、前記気相成長装置内で、前記窒化ガリウム系半導体層20上に、非晶質又は多結晶のIII族窒化物のピット埋込層30を形成して前記ピット25を埋める第2の工程と、前記ピット埋込層30を研磨により除去して前記窒化ガリウム系半導体層20の表面を露出させる第3の工程と、を具備する。

(もっと読む)

エピタキシャル構造、その形成方法、および、それを含むデバイス

薄膜トランジスタおよびその製造方法

【課題】しきい値電圧の経時変化およびホットキャリア劣化が可及的に小さく、かつオン特性の低下が可及的に小さい薄膜トランジスタおよびその製造方法を提供する。

【解決手段】ゲート電極32上に、ゲート絶縁膜36として、第1ゲート絶縁膜50と、第2ゲート絶縁膜51とを形成する。第1ゲート絶縁膜50を窒化シリコン膜で形成し、第2ゲート絶縁膜51を酸化シリコン膜で形成し、第2ゲート絶縁膜51の表面部にAr含有層52を形成する。Ar含有層52に接するように、微結晶シリコン膜62を形成し、さらにi型非晶質シリコン膜63およびN型非晶質シリコン膜61を形成して、活性層37を形成する。これによって、高密度に均一に結晶を成長させることができるので、均一でボイドの少ない微結晶シリコン膜62を形成することができる。

(もっと読む)

多結晶薄膜、その成膜方法、及び薄膜トランジスタ

【課題】十分に結晶化された多結晶薄膜を提供する。

【解決手段】インジウム元素及び酸素元素を含有した非晶質膜をスパッタリング装置で成膜し加熱することで、X線回折測定において2θが25deg〜35degの範囲に観測される(222)配向のロッキングカーブの半値全幅が0.4deg以下である多結晶薄膜を形成する。又、金属酸化物をスパッタリングによって成膜するに際し、プラズマの照射を2〜5秒間隔として成膜しその後結晶化する。

(もっと読む)

半導体装置の製造方法

【課題】 格子定数が異なる複数種類の半導体素子を同一の基板上に混載することが可能な半導体装置の製造方法を提供する。

【解決手段】 半導体装置の製造方法は、シリコン基板21の一部に絶縁膜22を形成し、シリコン基板21と絶縁膜22上にアモルファスSiGe層23を形成し、シリコン基板を熱処理し、アモルファスSiGe層23を絶縁膜22上に横方向に固相若しくは液相成長させて結晶化し、シリコン基板22と絶縁膜22上に格子定数が後に形成される材料層の格子定数に整合されたSiGe層23bを形成する。

(もっと読む)

3次元集積回路装置及びその製造方法

【課題】ガラス基板上に薄膜半導体層を形成した3次元集積回路装置を提供する。

【解決手段】ガラス基板11上に、単結晶もしくは準単結晶の2層の薄膜半導体層13,16が層間絶縁層14を介して積層され、2層の薄膜半導体層13,16は、下層の第1層の薄膜半導体層13と上層の第2層の薄膜半導体層16とが異なる材料であり、2層の薄膜半導体層13,16が、層間絶縁層14に形成された開口内を埋めて形成された、エピタキシャル層15によって接続され、エピタキシャル層15の表面部は、第2層の薄膜半導体層16と同じ材料の層であり、第1層の薄膜半導体層13及び第2層の薄膜半導体層16のうち、1層以上に能動素子Tr21,Tr22が形成されている3次元集積回路装置10を構成する。

(もっと読む)

所望の基板への単結晶材料からなる薄層の移動方法

【課題】第1の単結晶の基板から第2の基板へ、単結晶の薄層を移動する方法であって、層分割に必要とされる水素の注入量が低減された移動方法が実現される。

【解決手段】第1の単結晶の基板から第2の基板へ、単結晶の薄層を移動する方法は、水素のトラップを誘導するイオンを水素イオンと共注入すること、高温で水素を注入すること、またはこれらの組み合わせを実施し、次に、第1の基板の注入された層と残りの基板との結合を弱めるために熱処理を施し、さらに、注入された第1の基板と第2の基板との強力な接着を形成し、最後に、水素が充填された微小亀裂を形成、成長させることで単結晶の薄層が第1の基板の残りから分割するように別の熱処理を施すことを含む。

(もっと読む)

混合層の部分的再結晶化によるハイブリッド基板生成方法

【課題】下地基板と、複数の群の異なる隣接エリアから形成された混合層とを含むハイブリッド基板を簡単かつ確実に生成する方法を提案する。

【解決手段】ハイブリッド基板生成方法が

単結晶の第1の基板が、2つの表面部分11および12を得るように分離されるステップと、

表面部分11に沿って延び、第1のエリア13で形成され、かつアモルファス材料の異なる第2のエリアに隣接する混合層を含む仮基板が準備され、これらの第2のエリアが、この第1の基板の自由表面の少なくとも一部を形成するステップと、

少なくともこれらのアモルファスエリア全体の分子接合によって、第1の表面部分と同じ結晶配向の他の表面部分12がこの第1の基板に接合されるステップと、

2つの表面部分の結晶配向にしたがったアモルファスエリアの少なくとも一部の固相再結晶化が第1のエリアに対して選択的に生じ、2つの表面部分が有利には分離されるステップとを含む。

(もっと読む)

薄膜トランジスタの作製方法

【課題】絶縁層上に結晶性の高い微結晶半導体層を形成することを課題とする。また、電気特性が良好な薄膜トランジスタを、生産性高く作製する方法を提供することを課題とする。

【解決手段】基板上にゲート電極を形成し、ゲート電極上に、窒素を含む絶縁層を形成する。次に、窒素を含む絶縁層上に、シリコンを含む堆積性気体と、窒素を含む酸化気体と、水素とを用い、プラズマを発生させて、酸化珪素層を形成する。次に、酸化珪素層上に、シリコンまたはゲルマニウムを含む堆積性気体と、水素とを用い、プラズマを発生させて、微結晶半導体層を形成する。

(もっと読む)

シリコン膜の形成方法、pn接合の形成方法、及びこれを用いて形成されたpn接合

【課題】マイクロヒーターを利用して、多結晶シリコンからなるシリコン膜を形成する方法、pn接合を形成する方法、及びこれを用いて形成されたpn接合を提供する。

【解決手段】シリコン膜は、基板10及び基板と離間した金属パターン30を含むマイクロヒーターを利用して形成されうる。マイクロヒーターの金属パターンに電圧を印加して金属パターンを加熱し、シリコンを含むソース気体にマイクロヒーターを露出させて金属パターン上にシリコン膜100を形成することができる。シリコン膜は、多結晶シリコンからなりうる。pn接合は、基板10、基板上の導電層20、及び基板と離間した金属パターン30を含むマイクロヒーターを利用して形成されうる。マイクロヒーターの金属パターンに電圧を印加して金属パターンを加熱することで、金属パターンと導電層との間にpn接合を形成することができる。pn接合は、多結晶シリコンを含みうる。

(もっと読む)

薄膜トランジスタの作製方法

【課題】電気特性が良好な薄膜トランジスタを、生産性高く作製する方法を提供する。

【解決手段】基板上にゲート電極を形成し、ゲート電極上にゲート絶縁層を形成し、ゲート絶縁層上に、シリコンまたはゲルマニウムを含む堆積性気体と、水素と、ヘリウム、アルゴン、ネオン、クリプトン、キセノン等の希ガスとを用い、プラズマを発生させて、厚さ3〜10nm、好ましくは3〜5nmの第1の半導体層を形成する。次に、シリコンまたはゲルマニウムを含む堆積性気体と、水素と、窒素を含む気体とを用い、プラズマを発生させて、非晶質半導体と、第1の半導体層を種結晶として部分的に結晶成長させて、形成される微結晶半導体で形成される複数の錐形状の凸部を有する第2の半導体層を形成する。次に、一導電型を付与する不純物元素が添加された半導体層を形成し、導電層を形成して、薄膜トランジスタを作製する。

(もっと読む)

薄膜トランジスタ及びその作製方法

【課題】オン電流が高くオフ電流が低い薄膜トランジスタを提供する。

【解決手段】絶縁表面を有する基板上に、ゲート電極を覆うゲート絶縁層と、該ゲート絶縁層に接し、非晶質構造の中に複数の結晶領域を含みチャネル形成領域を構成する半導体層と、ソース領域及びドレイン領域を形成する一導電型を付与する不純物半導体層と、該半導体層と該一導電型を付与する不純物半導体層との間の非晶質半導体により構成されるバッファ層とを有し、前記結晶化領域は、前記ゲート絶縁層と前記半導体層との界面から離れた位置から、前記半導体層が堆積される方向に向けて、前記一導電型を付与する不純物半導体層に達しない領域内において略放射状に成長した逆錐形状の構造を有する薄膜トランジスタとする。

(もっと読む)

1 - 20 / 41

[ Back to top ]