Fターム[5H007BB11]の内容

Fターム[5H007BB11]の下位に属するFターム

Fターム[5H007BB11]に分類される特許

1 - 20 / 101

電力変換装置

フィルタコンデンサの放電方法

スイッチングシステムおよびスイッチングシステムの制御方法

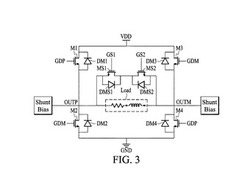

【課題】EMIを低減できるスイッチングシステムを提供する。

【解決手段】本発明は、スイッチングシステムを提供する。スイッチングシステムは、Hブリッジ、電流ルーターおよび制御回路を含む。Hブリッジは、第一出力ノードに結合される第一スイッチと第二スイッチおよび第二出力ノードに結合される第三スイッチと第四スイッチを含み、ロードは、第一出力ノードと第二出力ノード間に結合される。電流ルーターは、第一出力ノードと第二出力ノード間に結合される第一シャントスイッチと第二シャントスイッチを含む。制御回路は、第一制御信号を生成して、第一スイッチと第四スイッチを制御し、第二制御信号を生成して、第二スイッチと第三スイッチを制御し、第三制御信号を生成して、第一シャントスイッチを制御し、第四制御信号を生成して、第二シャントスイッチを制御する。

(もっと読む)

インバータ装置およびMR装置

【課題】直列に接続された複数のインバータブリッジを備えたインバータ装置において、インバータブリッジ間の利用率を変えて、インダクタンス性負荷を効率よく駆動する際に、インバータブリッジの入力電源電圧を安定させる。

【解決手段】制御部52が、所望の電流波形における電流値Iの正負および電流微分値dIt/dtの正負に基づいて、インバータブリッジ直列回路25がインダクタンス性負荷30に与える電力のインバータブリッジ21,22間のバランスと、インダクタンス性負荷30からインバータブリッジ直列回路25に回生される電力のインバータブリッジ21,22間のバランスとの不均衡を是正するよう、各インバータブリッジ21,22のオンデューティを制御する。

(もっと読む)

パワーモジュールおよび電力変換回路

【課題】電力変換回路の性能を高める。

【解決手段】ユニット10は、半導体スイッチ素子1,2と、ダイオード3,4とを備える。ダイオード3は、半導体スイッチ素子2がオン状態である時に逆バイアスされ、半導体スイッチ素子2がオフ状態である時に導通する。ダイオード4は、半導体スイッチ素子1がオン状態である時に逆バイアスされ、半導体スイッチ素子1がオフ状態である時に導通する。ダイオード3,4は、窒化ガリウム(GaN)ダイオードまたはダイヤモンドダイオードである。ユニット10を備えるパワーモジュールは、コンバータ、インバータ等の電力変換回路に適用される。

(もっと読む)

インバータの制御方法

【課題】スイッチングパターンが採用される期間が短いときに、キャリアの周期を長くすることなく当該期間を拡大できるインバータの制御方法を提供する。

【解決手段】3相の指令値Vu*,Vv*,Vw*のうち例えば一対の指令値Vv*,Vw*と、第1キャリアCとの比較によって決まるスイッチングパターンが採用される期間t61’が所定値以下であることが当該期間よりも前に推定されたときに、一対の指令値の一方、例えば指令値Vw*と比較される第2キャリアCwを生成する。第1キャリアCが増大する若しくは低減する方向において所定の変化率で一対の指令値の一方と交差する第1時点tc’に対して、第1キャリアCが当該方向で一対の指令値の他方、例えば指令値Vv*と交差する第2時点tbとは反対側の第3時点tcにおいて、第2キャリアCwが当該方向かつ当該変化率とは異なる変化率で一対の指令値の一方と交差する。

(もっと読む)

半導体電力変換装置

【課題】運転周波数にかかわらず高調波の少ない電圧を出力でき損失を低減した小型の半導体電力変換装置を提供する。

【解決手段】n(nは自然数)個の互いに絶縁された3レベルの電圧を出力する逆変換装置INVU1〜INVUnと、逆変換装置INVU1〜INVUnの入力直流電圧VDCの2分の1あるいは3分の1の電圧VDCSを入力直流電圧として逆変換装置INVU1〜INVUnと絶縁された3レベルの電圧を出力する逆変換装置INVUSとを有する。そして、逆変換装置INVU1〜INVUnと逆変換装置INVuとを直列従属接続し、最大VDC×n+VDCSを出力する。

(もっと読む)

負荷駆動回路

【課題】ブリッジ回路を構成する一対のMOSFETの内蔵ダイオードに流れる負荷電流の逆回復を速くする。

【解決手段】ブリッジ回路3は内蔵ダイオード4a、5aを内蔵したMOSFET4、5により構成される。MOSFET4、5はスイッチング制御回路6によりゲート駆動回路7、8を介して駆動制御される。負荷電流ILがコイル1からブリッジ回路に向けて流れる状態であって、例えば内蔵ダイオード4aを介して環流電流を流す状態からMOSFET5を介して負荷電流を流す状態への移行期間の終盤にMOSFET4をオンして内蔵ダイオード4aをオフさせ、電流I1がゼロ相当になったらMOSFET4をオフ、MOSFET5をクランプ状態で一定時間オンする。その後、MOSFET5を通常のオン状態に移行させる。

(もっと読む)

電源装置

【課題】出力電流偏差(設定電流値と出力電流値との差)を効果的に抑制する。

【解決手段】大容量インバータ回路10A,10Bと小容量インバータ回路20A,20Bとが誘導性負荷30を介して直列に接続されている。大容量インバータ回路10A,10Bは互いに並列に接続され、小容量インバータ回路20A,20Bは互いに並列に接続されている。大容量インバータ回路10A,10Bのスイッチング素子はIGBTであり、小容量インバータ回路20A,20Bのスイッチング素子はFETである。

(もっと読む)

超電導コイルの電源装置

【課題】電源装置の小型化が可能なスイッチング制御を採用し、スイッチングした際発生するスイッチングノイズを低減させることができる超電導コイルの電源装置を提供する。

【解決手段】超電導コイル2を励磁する電源装置101を、交流電力を直流電力にする直流電源手段51と、スイッチング信号に基づいて直流電力を交流状のスイッチング電力とする第1・第2スイッチング部52・53を並列接続したスイッチング手段56と、スイッチング電力を一定電圧の平滑化電力にして超電導コイル2に出力する平滑手段55と、第1・第2スイッチング部52・53に対して、所定の周波数でスイッチング信号をそれぞれ出力することにより所定の平滑化電力を形成し、第2スイッチング部53に出力するスイッチング信号を第1スイッチング部52に出力するスイッチング信号に対して位相差を持たせて出力するスイッチング制御手段54とを備えた構成とする。

(もっと読む)

半導体素子の駆動装置及び方法

【課題】半導体素子のスイッチング時において、スイッチング損失の増加を抑制しつつ、サージ電圧を低減すること。

【解決手段】ターンオフ用di/dt帰還部23OFFは、IGBT11Uがターンオフするときに、IGBT11Uのコレクタ電流Icの時間変化に基づいて、帰還電圧VFBを生成する。ターンオン用di/dt帰還部23ONは、IGBT11Uがターンオンするときに、FWD12Dの転流電流IFWDに基づいて、帰還電圧VFBを生成する。この場合、ターンオン用di/dt帰還部23ONは、転流電流IFWの方向が、リバースリカバリー区間に対応する方向、即ち図13に示すFWD12Dのカソードからモータ等の負荷L側に流れる方向である場合、帰還電圧VFBを生成し、それ以外の場合、帰還電圧VFBの生成を禁止する。

(もっと読む)

半導体素子の駆動装置

【課題】半導体素子のスイッチング時において、スイッチング損失の増加を抑制しつつ、サージ電圧を低減すること。

【解決手段】電子回路1の半導体素子駆動回路13は、ゲート抵抗21と、電圧源22と、di/dt帰還部23と、バッファ111と、を備えている。バッファ111は、従来良く使われる方式であるトランジスタ111ta,111tbで構成されるIGBT駆動用のバッファ回路の少なくとも一部である。di/dt帰還部23は、トランス121と、抵抗122と、を備えている。即ち、トランス121が、di/dt検出部及びゲイン部に対応する。なお、電圧源22とバッファ111とを結ぶ経路に抵抗122が直列接続され、抵抗122の両端が、トランス121の2次側に接続されており、当該経路上の抵抗122の両端の間が、電圧源に対応する。

(もっと読む)

負荷駆動装置

【課題】デッドタイムを正確に設定する。

【解決手段】第1の駆動制御部(11H)は、第1の切替タイミングが到来した場合に、出力電圧(Vout)が基準電圧(VrefL1)に到達したことを検出した後に、第1の駆動素子(SWL)をオフ状態からオン状態に切り替え、第2の切替タイミングが到来した場合に、第1の駆動素子(SWL)をオン状態からオフ状態に切り替える。第2の駆動制御部(13H)は、第1の切替タイミングが到来した場合に、第2の駆動素子(SWH)をオン状態からオフ状態に切り替え、第2の切替タイミングが到来した場合に、第2の駆動素子(SWH)をオフ状態からオン状態に切り替える。

(もっと読む)

インバータ電源装置

【課題】 本発明では、変圧器の1次側の入力電流値に影響されず精度の良い偏磁判別を行うことができるインバータ電源装置を提供することを目的とする。

【解決手段】 インバータ回路と、負荷に適した電圧に変圧する変圧器と、変圧器の入力電流値を検出する入力電流検出回路と、出力電流値を検出する出力電流検出回路と、インバータ回路を制御する出力変調制御回路と、入力電流値が偏磁電流基準値以上になると偏磁と判別する偏磁判別回路と、偏磁が判別された時点からインバータ周波数の半周期が終了するまで出力変調制御を禁止する禁止回路と、を備え、偏磁電流基準生成回路は変圧器の入力電流値をインバータ周波数の半周期ごとにサンプルホールドした値に予め定めた偏磁電流値を加算して半周期ごとの偏磁電流基準値を生成し、偏磁判別回路は入力電流値と半周期前の偏磁電流基準値とを比較する、ことを特徴とするインバータ電源装置である。

(もっと読む)

電力変換装置、及び、制御方法

【課題】交流電圧源から所望の周波数の交流電流を負荷に供給可能で、負荷に供給される電圧のピーク値の変動が小さく、低損失な電力変換装置及び制御方法を提供する。

【解決手段】電力変換装置10は、三相交流電源21の各相に接続されるリアクトルLac1乃至Lac3と、三相ブリッジ型MERS100と、直流交流変換回路200と、制御回路300と、から構成される。制御回路300が、三相ブリッジ型MERS100を構成する6つの逆導通型半導体スイッチのオン・オフを制御することで、三相ブリッジ型MERS100のコンデンサCMにパルス状の直流電圧が繰り返し発生する。コンデンサCMに発生するパルス状の直流電圧が、直流交流変換回路200を介して交流電圧に変換されて誘導性負荷LD1,LD2,LD3に印可される。

(もっと読む)

電力変換装置

【課題】半導体電力変換装置を氷点下に下がるような寒冷地に設置すると、水冷の電力変換システムでは、冷却水が凍結して冷却水を流せなくなり、半導体を冷却できなくなる可能性がある。また、風冷の電力変換システムでも冷却フィンが結露して凍結するとそれが障害となり、風の流れが設計時の想定と変わってしまい、そのまま運転すると十分な冷却効果を得られない可能性がある。本発明は交流系統への影響を最小限にして冷却フィンに付着した凍結物を安全に溶解することを目的とする。

【解決手段】双方向チョッパ回路などで構成された単位セルをカスケードに接続した構成を有するカスケード変換器システムにおいて、U相,V相,W相をデルタ結線に接続されたカスケード変換器システムであり、かつ、デルタ結線されたカスケードアームに零相循環電流を通流することにより、接続された系統に影響を与えることなく、冷却フィンの水を溶かして冷却性能を回復できる。

(もっと読む)

誘導素子駆動回路

【課題】 低消費電流化と高速動作化のトレードオフを克服し、貫通電流防止と駆動効率向上を可能にする誘導素子駆動回路を提供する。

【解決手段】 PWM信号を入力する入力端子11と、ソースが第1の電源端子に接続されたPMOS高耐圧トランジスタM0と、ソースがGNDに接続され、ドレインがトランジスタM0のドレインに接続されたNMOS高耐圧トランジスタM1と、トランジスタM0のドレイン及びトランジスタM1のドレインの接続点に設けられ、誘導素子L1を駆動する信号を出力する出力端子12と、出力端子12の電位変化を検出してトランジスタM0をオフした後にトランジスタM1をオンする電圧検出回路9とを備える。この電圧検出回路9は、出力端子12の端子電圧VLXがLowになったことを検知し、Highを出力してトランジスタM1をオンするので、貫通電流を防止する。

(もっと読む)

電解水生成装置

【課題】 一定の直流電圧を利用して電解能力を制御可能であり、しかも、電解能力の調整による損失を抑えることで、放熱のためのヒートシンクを小さくでき、基板をコンパクトに構成できる電解水生成装置を提供する。

【解決手段】 通水路中に対向した電極を有する電解槽と、所定電圧の直流電源とアースとに接続されたHブリッジ回路と、前記スイッチング素子のオン状態とオフ状態との組み合わせを変化させることで、前記電極に印加される直流電圧の極性を切替える通電制御手段と、を備えた電解水生成装置において、

¥前記通電制御手段は、2つのスイッチング素子を利用して所定の極性で前記電極へ所定電圧を印加し、前記電極に流れる電流が所定電流値となると所定電圧の印加を停止することを周期的に繰り返して電解能力を制御可能であり、前記Hブリッジ回路には、前記電極と直列状態で通電される位置にインダクタが接続されていることを特徴とする。

(もっと読む)

振動型圧縮機の電源装置

【課題】振動型圧縮機を駆動しているインバータの入力側直流電源を、バッテリ入力とAC/DC入力の二系統の電源から供給する際、その電流路にダイオードOR接続、及びDC/DCコンバータの構成を介さずに優先的な自動切換昨日を有する振動型圧縮機の電源装置を得る。

【解決手段】バッテリ入力の電源は相互にソース端子が接続されゲート端子は共通のゲート電圧によって駆動されるよう直列接続された第1及び第2のMOS−FETで電流路を導通制御し、AC/DC入力の電源は制御部で第3のMOS−FETで電流路を導通制御するよう構成される。バッテリ入力の電源はインバータに直接供給可能とし、AC/DC入力の電源が接続された場合には、バッテリ入力の電源に優先してインバータに供給されるよう前記第3のMOS−FETを導通させる。更にバッテリ入力の電源からの供給とバッテリ入力の電源への充電を第1及び第2のMOS−FETで阻止する。

(もっと読む)

スイッチング素子の駆動回路

【課題】ブリッジ回路を構成する高速スイッチング素子を駆動対象とする場合でも、セルフターンオンの発生を防止できる駆動回路を提供する。

【解決手段】SJ−MOSFETであるNチャネルMOSFET3H,3LによりHブリッジ回路1を構成する場合に、駆動回路21を、NチャネルMOSFET3のソースとゲートとの間に磁気結合構造22を設け、NチャネルMOSFET3Hがターンオンした際に、オフ状態に維持されるNチャネルMOSFET3Lの寄生ダイオード5Lに短絡電流が瞬間的に流れると、NチャネルMOSFET3Lのソースに発生する電圧変動に基づいてゲートに誘導される電圧変動を打ち消すため、磁気結合構造22Lを、PNPトランジスタ8LのコレクタとNチャネルMOSFET3のゲートとの間を接続する駆動側配線24Lを、NチャネルMOSFET3Lのソース配線23Lに対して同相で磁気結合させて構成する。

(もっと読む)

1 - 20 / 101

[ Back to top ]