Fターム[5H420NB22]の内容

電気的変量の制御(交流、直流、電力等) (13,664) | 出力部 (2,015) | 出力制御回路に付加された素子 (700) | 抵抗 (138)

Fターム[5H420NB22]に分類される特許

21 - 40 / 138

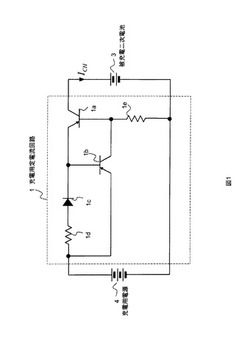

充電用定電流回路と充電装置

【課題】充電電流の温度依存性が小さい低コストの充電用定電流回路と、その充電用定電流回路を用いた過充電防止機能を備えた充電装置を提供する。

【解決手段】ベースとエミッタとコレクタとベースとがそれぞれ接続される同極性の第1のトランジスタと第2のトランジスタと、第1のトランジスタのベースに一端を順方向に接続するダイオードと、ダイオードの他端と当該第1のトランジスタのエミッタとの間に直列に接続される第1の抵抗素子と、第1のトランジスタのコレクタと第2のトランジスタのベースとの接続点に一端を接続する第2の抵抗素子と、を備え、第1のトランジスタのベース・エミッタ間電圧の温度変化をダイオードの温度変化で打ち消す。

(もっと読む)

半導体装置

【課題】トリミングデータによって調整可能な基準電圧発生回路を備えた半導体装置において、電源が立上がるまでの基準電圧のばらつきの影響を受けないようにする。

【解決手段】半導体装置10において、基準電圧生成部1は、外部電源電圧VCCに基づいて、トリミングデータTRM1に応じて調整された第1の基準電圧V1*およびこのトリミングデータTRM1に依存しない第2の基準電圧V2を生成する。不揮発性メモリ3は、第1の基準電圧V1*に基づく電圧によって動作し、上記のトリミングデータTRM1を記憶する。パワーオンリセット回路5は、電源立上げ時に外部電源電圧VCCが第2の基準電圧V2の定数倍に達したときにリセット信号の論理レベルを切替える。制御回路6は、リセット信号の論理レベルの切替に応答して、不揮発性メモリ3に記憶された上記のトリミングデータTRM1を基準電圧生成部1に読込ませる。

(もっと読む)

低雑音高効率バイアス生成回路及び方法

【課題】可変負荷デバイスへ安定した電圧及び電流信号を提供する。

【解決手段】装置は、無線周波数信号を変調するスイッチングモジュール22に対して、略定常状態の正電圧信号及び負電圧信号を生成し、正電圧信号及び負電圧信号は、スイッチングモジュール22のスイッチングイベントの間略安定なままである。装置は、正電圧信号よりも低い電圧レベルを有する略定常状態の基準電圧信号を生成するバイアス信号生成モジュール100と、正電圧信号を生成する正信号生成モジュール300と、負電圧信号を生成する負信号生成モジュール400とを有する。正信号生成モジュール300は、第1のキャパシタを用いて基準電圧信号に基づき正電圧信号の一部を生成し、負信号生成モジュール400は、第2のキャパシタを用いて基準電圧信号に基づき負電圧信号の一部を生成する。

(もっと読む)

差動増幅回路、レギュレータモジュール及びハイパワーアンプ

【課題】製造時の工程及び製品の消費電力の点で優れたレギュレータモジュール、及びそれを用いたバイアス回路を提供する。

【解決手段】パワーアンプモジュールとレギュレータモジュール801を含むパワーアンプをバイポーラトランジスタと電界効果トランジスタとを同一基板上に備える技術によって1チップで構成する。レギュレータモジュール801はデプリーション型トランジスタによる差動増幅回路を内包する。該差動増幅回路の一方のFETQ4のソース端子を、ダイオード接続したバイポーラトランジスタQ7を介して、FETQ3のソース端子と接続することで、バイポーラトランジスタQ7の電位差をレギュレータの出力電圧とすることが可能となる。

(もっと読む)

基準電圧発生回路とこれを用いた駆動装置、プリントヘッド及び画像形成装置

【課題】電源電圧の変動による基準電圧の変動を抑制し、駆動電流の変動をなくして印刷濃度むらを防止する。

【解決手段】基準電圧発生回路60では、PMOS61a,61bからなる第1のカレントミラー回路とNMOS61c,61dからなる第2のカレントミラー回路とを縦続接続して構成したカレントミラー回路部61を用いて、NPNTR65,66を駆動する構成にしている。そのため、カレントミラー回路部61の出力側のノードN3とノードN4の電位を略等しくすることができる。これにより、電源電圧VDDの値が変化しても、NPNTR66のコレクタ電位の変動を僅少にでき、基準電圧発生回路60から出力される基準電圧Vrefの変動を無視しうる程度にまで減少させることができる。

(もっと読む)

電流生成回路およびそれを用いた基準電圧回路

【課題】温度依存性を有する電流を生成可能な電流生成回路を提供する。

【解決手段】第1電流源42は、正の温度特性を有する第1電流I1を生成する。第2電流源44は、第2電流I2を生成する。第1カレントミラー回路46は、第2電流I2の経路上に設けられた、NPN型バイポーラトランジスタである補償用トランジスタQ5のベース電流Ibを第1係数(K1)倍して第3電流I3を生成する。第2カレントミラー回路48は、第1電流I1と第3電流I3の差に比例した第4電流I4’を生成する。電流生成回路40は、ベース電流Ibと比例した第5電流I5と第4電流I4’の合計電流を出力する。

(もっと読む)

電流源回路

【課題】矩形波の信号入力に応じて出力する出力電流の波形を矩形波に近づけることが可能な電流源回路を提供する。

【解決手段】電流源回路は、電圧端子に一端が接続された第1のMOSトランジスタと、第1のMOSトランジスタの他端に一端が接続され、出力端子に他端が接続された第2のMOSトランジスタと、電圧端子に一端が接続された第3のMOSトランジスタと、第3のMOSトランジスタの他端に一端が接続され、出力端子に他端が接続された第4のMOSトランジスタと、を備える。この電流源回路は、第1のMOSトランジスタおよび第4のMOSトランジスタに電流が流れるように第1の入力端子にバイアス電圧が印加された状態で、第2の入力端子に印加されるスイッチ電圧に応じて、第2のMOSトランジスタおよび第3のMOSトランジスタのオン/オフを同期して制御する。

(もっと読む)

バンドギャップリファレンス回路および回路を製造する方法

【課題】最低所要供給電圧が低く、小さいチップ領域を占め、電流消費が低く、供給電圧の変動に強いバンドギャップリファレンス回路を提供する。

【解決手段】電圧ジェネレータ(VG)と、供給回路(SC)と、バイアス要素(BB)および制御要素(CB)を含むバイアス回路(BC)とを、バンドギャップリファレンス回路は含む。供給回路(SC)の制御要素(CS)およびバイアス回路(BC)の制御要素(CB)のうちの一つは、擬似格子整合型高電子移動度トランジスタまたはヘテロ接合バイポーラトランジスタを含み、供給回路(SC)のバイアス要素(BS)およびバイアス回路(BC)のバイアス要素(BB)のうちの一つは、ロングゲート擬似格子整合型高電子移動度トランジスタまたは抵抗を含む。擬似構成整合型高電子移動度トランジスタおよびヘテロ接合バイポーラトランジスタは、GaAs BiFET技術プロセスを用いて製造される。

(もっと読む)

バンドギャップ回路、低電圧検出回路及びレギュレータ回路

【課題】オペアンプのオフセット電圧の影響を抑えたバンドギャップ電圧と最低動作電圧を抑えたバンドギャップ電圧とを得ることを目的とする。

【解決手段】開示の装置は、第1及び第2のPNPトランジスタ、第2のPNPトランジスタのエミッタに一端が接続された第1の抵抗、第1のPNPトランジスタのエミッタ及び第1の抵抗の他端が入力に接続され、負帰還制御が行われる第1のオペアンプを有する。また、開示の装置は、第1及び第2のPNPトランジスタのエミッタにベースが接続された第3及び第4のPNPトランジスタ、第4のPNPトランジスタのエミッタに一端が接続された第2の抵抗、第3のPNPトランジスタのエミッタ及び第2の抵抗の他端が入力に接続された、負帰還制御が行われる第2のオペアンプを有する。

(もっと読む)

電圧発生回路

【課題】低電源電圧で動作するバンドギャップ基準電圧発生回路は、分流パスを設けるため消費電流が多くなってしまう。公知技術の消費電流は、従来の低電源電圧動作のバンドギャップ回路から電流を削減したとはいえ、未だ多い。本発明では、低電源電圧で動作し、かつ、消費電流のさらに少ないバンドギャップ基準電圧発生回路を提供する。

【解決手段】本発明の基準電圧発生回路では、低電源電圧動作の本質を維持したまま、さらに分流パスを共通化することで、消費電流を削減する。

(もっと読む)

基準電圧生成回路及び半導体装置

【課題】交流的な電源電圧変動による基準電圧への影響を抑え、かつ、半導体装置に内蔵する場合にレイアウト面積を小さくできる基準電圧生成回路を提供する。

【解決手段】それぞれカソードが基準電位に接続された第1、第2のダイオードと、第2のダイオードのアノードに一端が接続された第1の抵抗素子と、第2の抵抗素子と、第1の抵抗素子の他端に一端が接続された第3の抵抗素子と、第1のダイオードのアノードに一端が接続された第4の抵抗素子と、第1、第2の差動入力端子と差動出力端子とを有する差動増幅回路と、を備え、第1の差動入力端子に第1の抵抗素子の他端が接続され、第2の差動入力端子に第2の抵抗素子を介して第1のダイオードのアノードが接続され、差動出力端子に第3の抵抗素子の他端と第4の抵抗素子の他端とが接続されている。

(もっと読む)

基準電圧回路

【課題】温度依存性を改善した基準電圧回路を提供する。

【解決手段】基準電圧回路100は、電源端子と接地端子の間に順に直列にスタックされた電流源30、第1バンドギャップリファレンス回路10および第2バンドギャップリファレンス回路20を備える。第1バンドギャップリファレンス回路10と第2バンドギャップリファレンス回路20はそれぞれ、互いに反対の温度係数を有する第1基準電圧Vref1、第2基準電圧Vref2を生成するよう構成される。基準電圧回路100は、第1基準電圧Vref1と第2基準電圧Vref2の和電圧Vref(=Vref1+Vref2)を出力する。

(もっと読む)

半導体集積回路およびそれを用いた差動増幅器およびバッファアンプ

【課題】バイアス信号を切りかえに伴う動作特性の悪化を低減した半導体集積回路を提供する。

【解決手段】半導体集積回路10は、入力電流Iinを受け、それに応じた出力電流Iout1を別の回路に供給する。第1可変抵抗R1の第1端子は、入力端子P1と接続される。第1トランジスタM1および第2トランジスタM2は、電源端子と第1可変抵抗R1の第2端子の間に順に直列に設けられる。第3トランジスタM3および第4トランジスタM4は、電源端子と出力端子P2との間に順に直列に設けられる。第1トランジスタM1および第3トランジスタM3それぞれのゲートは第1可変抵抗R1の第2端子に接続される。第2トランジスタM2および第4トランジスタM4それぞれのゲートは入力端子P1に接続されている。第1可変抵抗R1は、その抵抗値が入力電流Iinに応じて切りかえ可能に構成される。

(もっと読む)

電流源回路及びそれを用いた遅延回路及び発振回路

【課題】簡単な構成でデプレッション型MOSトランジスタの温度特性を補償する電流源回路を提供する。

【解決手段】2つのエンハンスメント型MOSトランジスタQ2、Q3から構成されたカレントミラー回路と、前記カレントミラー回路の入力側の前記エンハンスメント型MOSトランジスタQ2のドレインに接続され、定電流源として機能するデプレッション型MOSトランジスタQ1と、前記カレントミラー回路の入力側の前記エンハンスメント型MOSトランジスタQ2のソースに接続された負の温度特性を有する抵抗と、を含むことを特徴とする。

(もっと読む)

半導体装置及びその制御方法

【課題】半導体装置の内部電圧生成回路に供給されるグランド電圧の変動による影響を抑制すること。

【解決手段】内部回路は、内部電圧生成回路によって生成される内部電圧に基づいて動作する。また、内部電圧生成回路及び内部回路は、グランド配線を介してグランドに接続される。内部電圧生成回路は、内部電圧が出力される出力端子と、グランド配線に接続されるグランド端子と、電圧が基準電圧に応じた値に制御される中間ノードと、出力端子と中間ノードとの間に接続された第1抵抗部と、中間ノードとグランド端子との間に接続された第2抵抗部と、第1抵抗部の抵抗値R1と第2抵抗部の抵抗値R2の比率R1/R2を切り換えるスイッチ部と、を備える。スイッチ部は、内部回路が動作する時の比率を、内部回路が動作を停止している時の比率よりも大きくする。

(もっと読む)

半導体装置

【課題】所定レベルの電圧を早期に生成するとともに、回路規模の増大を防ぐことが可能な半導体装置を提供する。

【解決手段】半導体装置101は、第1の電源電圧が供給される第1電源ノードと第1の電源電圧よりも低い第2の電源電圧が供給される第2電源ノードとの間に接続され、第1電源ノードからキャパシタCが電気的に接続されるべき基準ノードへ電流を流すことにより、キャパシタCを充電し、基準ノードの電位を所定電圧レベルにするための基準電圧生成回路11と、第1電源ノードと基準ノードとの間に直列接続された抵抗およびスイッチ、または第1電源ノードと基準ノードとの間に接続されたトランジスタを含み、第1電源ノードから基準ノード経由でキャパシタCへ電流を流すことにより、基準電圧生成回路11よりも速くキャパシタCを充電することが可能な充電加速回路10とを備える。

(もっと読む)

参照電圧発生回路および受信回路

【課題】 電源電圧依存性および温度依存性の低い参照電圧発生回路を提供し、もって受信感度の良好な受信回路を実現する。

【解決手段】 受信回路は、AMI符号化された一対の信号を増幅する差動増幅回路(11)と、差動増幅回路の出力と所定の参照電圧とを比較して入力信号の論理レベルを判別する受信データ判定回路(12)と、前記参照電圧を発生する参照電圧発生回路(13)とを備え、参照電圧発生回路は電源電圧を基準にした温度依存性の低い参照電圧を発生するように構成した。

(もっと読む)

基準電流電圧発生回路

【課題】基準電流電圧発生回路の起動後には、起動回路が基準電流電圧発生回路の動作へ与える影響を軽減することができる基準電流電圧発生回路を提供すること。

【解決手段】本発明にかかる基準電流電圧発生回路は、複数のトランジスタにより自己帰還回路を構成し、基準電流または基準電圧を発生させる基準電流電圧発生回路であって、基準電流電圧回路の非動作時には、電位が第1の電源と実質的に等しく、基準電流電圧発生回路の動作時には、電位が、第1の電源の電圧から第2の電源VDDの電圧の方向に所定値以上変動する節点101と、第2の電源と、の間に接続され、ゲートが第1の電源に接続されているノーマリーオン型トランジスタ21、を備える

(もっと読む)

半導体集積回路装置

【課題】面積の大幅な増大なくレファレンス電圧生成回路を低消費電流化するとともに通常動作モード時とスタンバイモード時においてレファレンス電圧精度の大幅な劣化を抑制する。

【解決手段】スタンバイモード時に、分周制御回路14は発振回路5が生成したクロックから、基準電圧発生回路3、基準電圧生成回路4、容量充電レギュレータ11のON/OFFを決めるイネーブル信号VREFONと基準電圧発生回路3、基準電圧生成回路4、ならびに容量充電レギュレータ11がONの際に、保持容量回路6内の保持容量CHに充電し、OFF期間に保持容量CHに対してリーク電流パス以外は存在しないように制御するサンプリング/ホールド信号CHOLDSWを生成する。消費電流の大きい基準電圧発生回路3、基準電圧生成回路4、容量充電レギュレータ11を間欠動作させて低消費電流化を図る。

(もっと読む)

半導体装置

【課題】従来の分圧回路では、電源電圧の変動に対して分圧電圧を一定に保つことができないために定電圧発生回路が必要であり回路規模が大きくなる問題があった。

【解決手段】本発明の分圧回路は、第1の電源VCCと第2の電源VNEGとの間に直列に接続される第1の抵抗素子R1と第1のトランジスタN1とを備え、第1のトランジスタに流れる第1の電流iN1の大きさに応じて設定される第1の抵抗素子R1と第1のトランジスタN1との抵抗比に基づき第1の電源VCCの電圧と第2の電源の電圧VNEGとの電圧差を分圧して分圧電圧を生成する分圧電圧生成回路11と、第1のトランジスタN1とミラー接続され、第1の端子から第2の端子に流れる制御電流i3により第1の電流iN1の大きさを決定する第2のトランジスタN2を有し、第1の電源VCCと接地電源との電圧差の増減に応じて制御電流i3を増減させる電流制御回路12と、を有する。

(もっと読む)

21 - 40 / 138

[ Back to top ]