Fターム[5H420NB22]の内容

電気的変量の制御(交流、直流、電力等) (13,664) | 出力部 (2,015) | 出力制御回路に付加された素子 (700) | 抵抗 (138)

Fターム[5H420NB22]に分類される特許

61 - 80 / 138

基準電圧発生回路

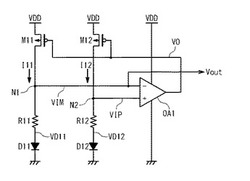

【課題】温度係数が実質的に零でありながら低い電源電圧で動作する基準電圧発生回路を、ディプレッション型トランジスタを使用せずに実現する。

【解決手段】基準電圧発生回路が、演算増幅回路OA1と、抵抗素子R11と、ダイオードD11と、抵抗素子R12と、ダイオードD12と、演算増幅回路OA1の出力をゲートに受けるPMOSトランジスタM11、M12とを具備する。ダイオードD12のPN接合の面積の、ダイオードD11のPN接合の面積に対する比をn11とし、PMOS

トランジスタM11のW/L比のPMOSトランジスタM12のW/L比に対する比をn12としたとき、これ等のパラメータは、R12・ln(n11・n12)/(R12−n12・R11)の値がほぼ23.25となるように調節され、これにより、演算増幅回路OA1の入力端子の電圧の温度係数が実質的に零に調節される。

(もっと読む)

基準電圧回路

【課題】 デプレッション型MOSFETとエンハンスメント型MOSFETとを用いた基準電圧回路において、基準電圧を低電圧化する。

【解決手段】 デプレッション型MOSFET(M1)のソースを、主トランジスタがn型であるソースフォロワ11の入力端子に接続し、ソースフォロワ11の出力端子を主トランジスタがp型であるソースフォロワ12の入力端子に接続し、ソースフォロワ12の出力はエンハンスメント型MOSFET(M2)のゲートに接続され、

ソースフォロワ12の出力を抵抗分割して所定の電圧を得ることを特徴とする基準電圧回路とする。

(もっと読む)

基準電圧発生回路

【課題】高電位の電源電圧が供給される場合であっても、回路面積の増大を招くことなく、安定して基準電圧を発生することができる基準電圧発生回路を実現する。

【解決手段】ノードn11とGND間の第1のトランジスタ301と、ノードn11とGND間の第2のトランジスタ302と、第6のトランジスタ313とGND間の第3のトランジスタ303と、ノードn12とノードn11間の第4のトランジスタ304と、VCC2とノードn12間の第5のトランジスタ305と、抵抗312と第3のトランジスタ303間の第6のトランジスタ313と、を備える基準電圧発生回路である。第5のトランジスタ305の制御端子は第6のトランジスタ313及び抵抗312の接続点に接続されており、第6のトランジスタ313の制御端子は第2のノードn12に接続されている。

(もっと読む)

分圧回路

【課題】電圧源からソース電流が流れず、かつ電圧源に対してシンク電流が流れ込まず、高い精度にて入力電圧を所定の比により分圧する分圧回路を提供する

【解決手段】本発明の分圧回路は、入力電圧に対応して第1抵抗に流れる電流を定電流として出力する定電流回路と、定電流が入力電流となり、第1出力電流を出力する第1カレントミラー回路と、第1出力電流が入力電流となり、第2出力電流を出力する第2カレントミラー回路と、第2カレントミラー回路の第2出力電流が出力される出力端子に接続された第2抵抗とを有し、第1カレントミラー回路及び第2カレントミラー回路のカレントミラー比と、第2抵抗及び第1抵抗の抵抗比とにより、第2抵抗の両端の電位差である分圧電圧を調整する。

(もっと読む)

半導体集積回路装置

【課題】プロセスバラツキの影響を抑制し、低電圧動作に適した基準電圧発生回路を提供する。

【解決手段】第1トランジスタ(以下、Tr)と大きなエミッタ面積を持つ第2Trを有し、第1増幅回路により第1Trのベースとコレクタ電圧が等しくなるよう第1と第2Trのベース電流を形成する。第1抵抗は、第2Trのエミッタと基準電位との間に設けられてバンドギャップ電圧が印加される。第3TrのエミッタとVSSとの間に第2抵抗が、コレタク,ベースとVSSとの間に第3抵抗が設けられる。第1と第2抵抗の比により、第3Trのコレタク,ベースから出力される基準電圧の温度補償を行う。第2増幅回路は、第1と第2Trのコレタクが等しくなるよう第1ないし第3MOSのゲート電圧を形成し、第1ないし第3Trのコレタク電流をそれぞれ形成する。第1ないし第3MOSのソース側に第4ないし第6抵抗を設ける。

(もっと読む)

定電圧発生回路およびA/D変換回路

【課題】定電圧発生回路に対して供給される電源電圧に変動があった場合でも、所定の差分を有する電圧を精度よく発生させる定電圧発生回路、および、その定電圧発生回路を備えたA/D変換回路を提供する。

【解決手段】第1入力端子11、第2入力端子12、第1出力端子21、第2出力端子22および入力コモン端子13を備えた全差動型OPアンプ50と、電源VDDとグランドとの間に直列接続された抵抗R2、抵抗R3および定電流源10と、電源VDDとグランドとの間に直列接続された抵抗R1,R1とを備える。抵抗R2の両端子は、第1入力端子11および第2入力端子12にそれぞれ接続され、抵抗R1,R1の接続点は、入力コモン端子13に接続されている。

(もっと読む)

基準電圧回路

【課題】半導体集積回路上に形成され、チップ面積が小さく、低電圧から動作し、温度特性の小さな1V以下の基準電圧を供給する基準電圧回路を提供する。

【解決手段】ダイオード(Q1)と抵抗(R4)の並列回路からなる第1の電流−電圧変換回路と、並列接続されたダイオード群(Q2)とダイオード群(Q2)の端子間に直列接続された抵抗(R1、R2)と、ダイオード群(Q2)とグランド間に接続された抵抗(R3)よりなる第2の電流−電圧変換回路と、前記第1、及び第2の電流−電圧変換回路に電流をそれぞれ供給するカレントミラー回路(M1、M2)と、記第1の電流−電圧変換回路の所定の出力電圧と前記第2の電流−電圧変換回路の所定の出力電圧とが互いに等しくなるように制御する制御手段(AP1)と、有し、第1、又は第2の電流−電圧変換回路の中間端子電圧を基準電圧Vrefとする。

(もっと読む)

基準電圧生成回路、集積回路装置および信号処理装置

【課題】 基準電圧生成回路と温度センサ回路を組み合わせたバンドギャップ回路において、基準電圧のばらつきと、温度センサ出力電圧のばらつきの双方の変動を抑えること。

【解決手段】 素子ばらつきによる基準電圧Vrefの「頂点温度ばらつき」と「出力電圧ばらつき」を抑えるために、基準電圧の生成に関与する第1の抵抗R3の抵抗値を微調整する場合、温度センサ出力VPTATを生成する第3の抵抗R4の抵抗値も同時に、同比率で微調整する。第1の抵抗R3および第3の抵抗R4は、共に可変抵抗回路で構成され、可変抵抗回路の抵抗値は、トリミング信号によって調整される。抵抗値を調整するためのトリミング信号は、例えば、トリミング回路(ICに搭載されるEEPROM等)300から出力する。

(もっと読む)

バンドギャップリファレンス回路

【課題】比較的簡単な回路構成を用いながら、カレントミラー回路を構成するMOSトランジスタのチャネル長又はチャネル幅に誤差が生じても基準電圧値のバラツキが少ない高精度な基準電圧を得ることができるバンドギャップリファレンス回路を提供する。

【解決手段】この回路は、PN接合を有し、N型半導体に電源電位VSSが接続された複数の第1の半導体素子と、複数の第1の半導体素子のP型半導体に複数の第1のNチャネルMOSトランジスタを介して電流をそれぞれ供給する複数の第1のPチャネルMOSトランジスタと、第1の半導体素子とは並列接続個数又はサイズが異なるPN接合を有し、N型半導体に電源電位VSSが接続された第2の半導体素子と、第2の半導体素子のP型半導体にインピーダンス素子及び第2のNチャネルMOSトランジスタを介して電流を供給し、複数の第1のPチャネルMOSトランジスタとカレントミラー回路を構成する第2のPチャネルMOSトランジスタとを具備する。

(もっと読む)

電流負帰還回路およびそれを用いるDC−DCコンバータ

【課題】簡便な回路で高速に電流モード制御のためのインダクタンス電流に略比例する、もしくはインダクタンスの充電電流の2次関数となる電流を生成・出力可能とし且つスイッチングノイズの影響を低減できる電流負帰還回路およびそれを用いるDC-DCコンバータを提供する。

【解決手段】カレントミラー回路を構成する第一のPch MOSFET 21と第二のPch MOSFET 22、電流調整抵抗20、電流検出抵抗12、および、定電流源23とで電流検出部300を構成し、定電流源24、第一のスイッチ素子であってキャパシタ27への充電経路となるPch MOSFET 25、第二のスイッチ素子であってキャパシタ27の放電経路となるNch MOSFET 26、及び、キャパシタ27でもって鋸歯状波生成部400を構成し、電流検出部300と鋸歯状波生成部400とで電流負帰還回路500を構成する。

(もっと読む)

基準電圧生成回路及びその起動制御方法

【課題】従来の基準電圧生成回路は、出力電圧が所定の電圧値を超えてしまう期間がある問題があった。

【解決手段】本発明にかかる基準電圧生成回路は、第1の電源Vddと第2の電源Vssとの間に設けられ、出力端子Voに対して出力電圧を出力する電圧生成回路10と、出力端子Voと第1の電源Vddの間に接続され、第1の電源Vddの電圧を出力端子Voに与える起動補助回路12と、出力端子Voの電圧の値に応じて起動補助回路12の動作状態と非動作状態とを切り替える制御回路13と、を有するものである。

(もっと読む)

負荷電流を温度に依存して調節するための回路構成

【課題】負荷電流を温度に依存して調節するための回路構成を提供すること。

【解決手段】差動増幅器は、負荷電流ILを温度の関数として調節するために第1および第2のトランジスタ(Q1、Q2)を有し、回路構成(2)は、2つのトランジスタ(Q1、Q2)が同じコレクタ−エミッタ電圧UCE1、UCE2にて、および1とは異なるコレクタ静止電流IC1、IC2の一定比率にて動作するように設計され、それにより回路構成(2)は、半導体の物理的特性によって決まる温度電圧によって制御され、負荷電流ILを規定された形で温度の関数として調節する。さらに、このような回路構成(2)を備える自動車用ファン、および関連する方法に関する。

(もっと読む)

温度補償バイアス回路

【課題】センサノードにおける待機時の低消費電力化を図るべく、クロック生成回路に用いられるバイアス回路の低消費電力化及び温度・電圧変動特性の改善を目的とする。

【解決手段】本バイアス回路は、カレントミラー型構造の第1と第2のPMOSトランジスタと、カレントミラー型構造の第3と第4のNMOSトランジスタと、第4のNMOSトランジスタと接地電圧間に接続された抵抗Rsにより構成されるリファレンス回路において、ドレインが第4のNMOSトランジスタと抵抗Rsの間のノードと連結され、かつ、ソース及びゲートが電源電圧に連結された第5のPMOSトランジスタを備える。この第5のPMOSトランジスタのリーク電流を用いて第4のNMOSトランジスタのゲート・ソース間電圧を制御する。このバイアス回路を水晶発振回路などのクロック生成回路の電流源とすることで、精度の高いクロックを低電力で生成することができる。

(もっと読む)

基準電圧発生回路

【課題】簡易な構成によって基準電圧発生回路の基準電圧の温度依存性を精度良く補正する。

【解決手段】第1及び第2バイポーラトランジスタQ1,Q2と、このQ1,Q2に定電流を供給するカレントミラー回路10とを備える。Q1のベースは、抵抗R1を介してカレントミラー回路10の第1電流供給側(M1)に接続され、Q1のコレクタは、抵抗R2を介してQ1のベースに接続される。Q2は、そのペースがQ1のコレクタに接続され、コレクタは、カレントミラー回路10の第2電流供給側(M2)に接続され、R1とM1との接続端に、基準電圧を出力する出力端子が設けられる。カレントミラー回路の第3電流供給側(M3)は、Q1のコレクタに接続され、M3に得られる電流I2により、基準電圧の温度依存性を補正する。

(もっと読む)

温度非直線性を補償した基準電圧回路

【課題】回路規模を増やさないでダイオードの持つ温度非直線性を補償した基準電圧を得、低電圧で動作する低消費電流の基準電圧回路を提供する。

【解決手段】第1、第2、第3の電流−電圧変換回路I−V1、I−V2、I−V3と、第1、第2、及び第3のカレントミラー回路M1,M2,M3と、第1の電流−電圧変換回路I−V1の出力電圧と第2の電流−電圧変換回路I−V2の出力電圧とを等する制御手段AP1とを有し、第3の電流−電圧変換回路I−V3の所定の電圧を基準電圧とし、第1の電流−電圧変換回路I−V1はダイオードに並列接続された抵抗を備え、第2の電流−電圧変換回路I−V2は並列接続された複数のダイオードと、複数のダイオードに並列接続された抵抗と、複数のダイオードと抵抗の並列回路に直列接続された抵抗と、並列回路と抵抗の直列回路に並列接続された抵抗とを備え、第3の電流−電圧変換回路(I-V3)は、抵抗を備る。

(もっと読む)

基準電圧回路、駆動回路、プリントヘッドおよび画像形成装置

【課題】LED発光パワーのマイナスの温度依存性とドライバIC内の基準抵抗の温度依存性を補償するもので、 所望の温度係数や出力電圧値を任意に設定可能な基準電圧発生回路、駆動回路、プリンタ及び画像形成装置を提供する。

【解決手段】本発明の基準電圧発生回路38は、所定電圧を出力するレギュレータ回路101、トランジスタ102、抵抗103、104、105、106で構成され、レギュレータ回路101の出力端子はトランジスタ102のコレクタおよび抵抗103と接続され、グランド端子はグランドに接続される。抵抗103はトランジスタ102のベースと抵抗104に接続され、抵抗104はトランジスタ102のエミッタと抵抗105に接続され、抵抗105は抵抗106および基準電圧出力端子Vrefに接続される。

(もっと読む)

基準電圧回路、駆動回路、プリントヘッドおよび画像形成装置

【課題】LED発光パワーのマイナスの温度依存性とドライバIC内の基準抵抗の温度依存性を補償するためのものであって、 所望の温度係数や出力電圧値を任意に設定可能な基準電圧発生回路、駆動回路、プリントヘッドおよび画像形成装置を提供する。

【解決手段】本発明の基準電圧発生回路39は、レギュレータ回路71、抵抗81、感温抵抗82を具備し、レギュレータ回路71の電源端子は電源VDDと接続され、出力端子は抵抗81の一端と接続され、グランド端子は抵抗81の他端と接続されている。またレギュレータ回路71のグランド端子は感温抵抗82の一端と接続され、基準電圧出力端子Vrefと接続される。感温抵抗82の他端はグランドに接続されている。

(もっと読む)

基準電圧回路

【課題】 電源電圧が低くても電源電圧変動除去比が大きい基準電圧回路を提供する。

【解決手段】 電源端子10の電源電圧が低くなり、NMOS71が非飽和動作し、NMOS71の出力抵抗ro71が低くなっても、差動増幅回路60の増幅度Aoが大きければ、電源電圧変動除去比PSRRLFも大きくなる。よって、基準電圧回路の最低動作電圧が低くても、電源電圧変動除去比PSRRLFは大きくなることができる。つまり、差動増幅回路60の増幅度Aoが電源電圧変動除去比PSRRLFに寄与するので、差動増幅回路60の増幅度Aoが大きければ、その分、電源電圧変動除去比PSRRLFも大きくなる。

(もっと読む)

起動回路

【課題】消費電力を比較的小さくして、確実に起動電流を制御する。

【解決手段】電源電圧Vddが立ち上がると、MOSトランジスタM1が電流を流し、MOSトランジスタM4がオンしてMOSトランジスタM5がオンし、バンドギャップ回路10に起動電流が供給される。バンドギャップ回路10が起動すると、MOSトランジスタM6にバンドギャップ回路10の定電流に応じた電流が流れ、これがMOSトランジスタM7に流れることによって、MOSトランジスタM2がオフして、MOSトランジスタM5がオフする。

(もっと読む)

定電圧発生回路および定電圧発生方法

【課題】負荷となる利得可変増幅回路の負荷電流が増加するような場合であっても、所望の定電圧を出力可能な定電圧発生回路を提供する。

【解決手段】定電圧発生回路の出力回路として、あらかじめ定めた値まで低減した低出力インピーダンスの回路構成とするために、1ないし複数個のトランジスタTF1,TF2,TF3を並列接続してなるエミッタフォロア回路を用いる。トランジスタTF1,TF2,TF3の並列接続数を、負荷となる利得可変増幅回路で流れる負荷電流の電流レベルに応じた任意の値に設定する。また、出力回路に、出力電圧微調整用のトランジスタTE1,TE2,TE3またはダイオードを、エミッタフォロア回路と電源電圧端子との間に、出力電圧の微調整レベルに応じて1ないし複数個挿入する。エミッタフォロア回路用または出力電圧微調整用のトランジスタとして、バイポーラトランジスタまたは電界効果型トランジスタのいずれかを用いる。

(もっと読む)

61 - 80 / 138

[ Back to top ]