Fターム[5H420NB22]の内容

電気的変量の制御(交流、直流、電力等) (13,664) | 出力部 (2,015) | 出力制御回路に付加された素子 (700) | 抵抗 (138)

Fターム[5H420NB22]に分類される特許

101 - 120 / 138

電圧発生回路

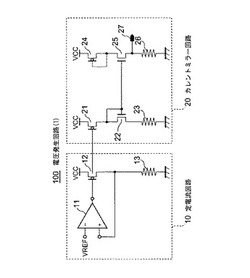

【課題】微小電圧で、且つ任意の供給電流を設定することができ、負荷の電圧遷移を高速に行うことが可能である、安定した微小電圧を発生する電圧発生回路の提供を目的とする。

【解決手段】演算増幅器11と、第1のPMOSトランジスタ12と、第1の抵抗13とからなる定電流回路と、第2のPMOSトランジスタ21と、第1のNMOSトランジスタ22と、第2の抵抗23と、第3のPMOSトランジスタ24と、第2のNMOSトランジスタ25と、第3の抵抗26と、出力端子27とからなるカレントミラー回路とを有する。

(もっと読む)

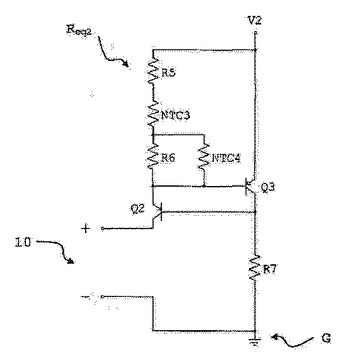

1V〜10Vインタフェース用の温度補償電流発生器

本発明は、ベース‐エミッタ接合領域を備えた少なくとも1つのトランジスタおよび当該のトランジスタに結合された抵抗回路網が設けられており、温度ドリフトに曝される前記ベース‐エミッタ接合領域での電圧降下と前記抵抗回路網の抵抗値とに基づいて出力電流の電流強度が定められる、入力電圧から出力電流を形成する装置に関する。本発明によれば、前記抵抗回路網はその抵抗値が温度にともなって変化する少なくとも1つの抵抗素子を含んでおり、前記出力電流の前記電流強度は前記ベース‐エミッタ接合領域での前記電圧降下の温度ドリフトから独立に一定に保持される。  (もっと読む)

(もっと読む)

温度依存性を有する内部電源発生装置

【課題】温度の変動によって一定、又は増減する特性を有する内部基準電圧を生成するバンドギャップ基準電圧生成装置を提供すること。

【解決手段】温度の変化に関係なく、一定の電位レベルを有する第1の電圧、温度の増加に対応して正(+)の特性を有する第2の電圧、及び温度の増加に対応して負(―)の特性を有する第3の電圧を生成する電圧生成手段と、前記第1の電圧ないし第3の電圧のうち、いずれか1つの電圧を選択し、該選択された電圧の温度特性を有する少なくとも1つ以上の内部基準電圧を生成する内部基準電圧生成手段とを備えることを特徴とする。

(もっと読む)

半導体集積回路装置

【課題】微細化されたMOSFETに好適な基準電圧発生回路を有する半導体集積回路装置を提供する。

【解決手段】第1電流密度とされる第1トランジスタと第1電流密度よりも小さな第2電流密度とされる第2トランジスタのベースを共通接続し、そのコレクタ差電圧に対応した出力電圧を増幅回路で形成して上記ベースに帰還する。第1抵抗素子に上記第1と第2トランジスタのベース,エミッタ間差電圧を印加して基準電流を形成する。上記基準電流に対応した電流を上記第1、第2及び第3トランジスタに供給する。上記第3トランジスタのベースとコレクタとを共通接続し、第2抵抗素子を直列形態に接続する。上記第3トランジスタのサイズ及び上記第1及び第2抵抗素子の抵抗値の設定により、上記第3トランジスタ及び第2抵抗素子で発生する電圧が、上記第1及び第2電源電圧及び温度変化に対して一定の基準電圧となるようにする。

(もっと読む)

基準電圧生成回路

【課題】外部電源のノイズの影響を阻止しつつ、基準電圧を生成する。

【解決手段】電流制御部30のトランジスタNM31のゲートは、トランジスタNM13,NM14のゲートに接続されて、トランジスタNM13,NM14にそれぞれ流れるドレイン電流と同じ量のドレイン電流がトランジスタNM31に流れる。このドレイン電流は、定電流回路部20のトランジスタPM22にも流れる。トランジスタPM21とトランジスタPM22のチャンネル幅の比は、3対1に設定され、トランジスタPM21には、トランジスタPM22の3倍の電流が流れる。トランジスタPM21,PM22は飽和領域で動作し、電圧VCの外部電源から供給された電流を定電流化し、基準電圧Vrefを生成するバンドギャップ回路部10に供給する。バンドギャップ回路部10に供給される電流が定電流化されるので、外部電源に重畳したノイズの影響は阻止される。

(もっと読む)

基準電圧発生回路

【課題】低消費電力で温度変動に対し安定した基準電圧を得る。

【解決手段】カレントミラー回路を負荷とする差動増幅器と、差動増幅器によって駆動される第1〜第4の電流源と、一端を第1の電流源および差動増幅器の反転入力端子と接続し、他端を接地するダイオードD1と、一端を第2の電流源および差動増幅器の非反転入力端子と接続し、他端を接地する、ダイオードD2と抵抗素子R1との縦続回路と、一端を第3の電流源および基準電圧の出力端子と接続し、他端を第4の電流源と接続する抵抗素子R3と、一端を前記第3の電流源と接続し、他端を接地する抵抗素子R4と、一端を第4の電流源と接続し、他端を接地するダイオードD3とを備える。カレントミラー回路および第1〜第4の電流源を構成するそれぞれの電界効果トランジスタP1〜P6にソース電位より深いバックゲートバイアスを与える。

(もっと読む)

基準電圧発生回路

【課題】絶対値が小さくても高い温度依存性を有する基準電圧を発生させることができる基準電圧発生回路を提供する。

【解決手段】電流経路P1は、入力端子14A側から見て、ダイオード11、及び抵抗12(抵抗R1)を直列接続して形成され、第2の電流経路P2は、入力端子14A側からダイオード13、抵抗14(抵抗R2)及び抵抗15(抵抗R3)を直列接続して形成される。オペアンプ20の反転入力端子には、ダイオード11のカソードと抵抗12との間の接続点の電圧V1が与えられ、非反転入力端子には、抵抗14と抵抗15との接続点の電圧V2が与えられる。

(もっと読む)

基準電位発生回路

【課題】低電源電圧で使用可能なCMOS集積回路用の基準電位発生回路を提供する。

【解決手段】シート抵抗12とダイオード接続されたNMOS13による電位Vnaと、ダイオード接続されたNMOS15による電位Vnbが同電位になるように、演算増幅器20の制御電圧CONによってPMOS11,14の駆動電流Ia,Ibを制御する。制御電圧CONを電流ミラーを構成するPMOS16に与え、このPMOS16に直列に接続されたシート抵抗17とダイオード接続されたNMOS18による電位を、基準電圧VREFとして出力する。電源電位VCCと接地電位GND間には、1組のPMOSとNMOSだけが接続されるので、1.5V程度の低電源電圧でも、電源電位VCCと周囲温度に依存しない一定の基準電圧VREFが得られる。

(もっと読む)

半導体集積回路

【課題】本発明は、バンドギャップ電圧に限定されることなく、任意の電圧を発生可能なバンドギャップ回路を提供することを目的とする。

【解決手段】半導体集積回路は、絶対温度に実質的に比例する第1の電流を発生する電流発生回路と、電流発生回路で発生した第1の電流に基づいて絶対温度に実質的に依存しない基準電圧を生成する電圧発生回路を含み、電圧発生回路は、絶対温度に実質的に負に比例する電圧を生成する第1の素子と、第1の素子に並列に接続される抵抗分圧回路と、第1の素子と抵抗分圧回路との並列接続に接続され第1の電流に比例する第2の電流を供給する第2の素子と、抵抗分圧回路の抵抗間のノードに接続され第1の電流に比例する第3の電流を供給する第3の素子を含むことを特徴とする。

(もっと読む)

基準電圧発生回路

【課題】電圧電源で動作可能であり、出力インピーダンスの低く、さらには安定した基準電圧を供給可能な基準電圧発生回路を提供することを目的としている。

【解決手段】本発明の基準電圧発生回路30は、ディプレッション型のトランジスタM3のゲートとソースが接続され、このトランジスタM3とエンハンスメント型のトランジスタM4のソースが接地された状態で、トランジスタM4のゲート電圧を出力電圧である基準電圧VrefHとした。

(もっと読む)

ダイオードの非直線性を補償した基準電圧回路

【課題】ダイオードが持つ温度特性の非直線性を相殺可能とする基準電圧発生回路の提供。

【解決手段】

第1、第2の電流−電圧変換回路101、102と、第1、第2の電流−電圧変換回路の所定の出力電圧が等しくなるように制御する制御手段(AP1)121と、第1、第2の電流−電圧変換回路に電流を供給する第1のカレントミラー回路111と、を備えた第1の基準電流回路1と、第3、第4の電流−電圧変換回路103、104と、第3及び第4の電流−電圧変換回路の所定の出力電圧が等しくなるように制御する制御手段(AP2)122と、第3、第4の電流−電圧変換回路に電流を供給する線形な入出力特性を持つ第2のカレントミラー回路112と、を備えた第2の基準電流回路2と、前記第1の基準電流回路の出力電流I3と前記第2の基準電流回路2の出力電流I6の差電流を出力する手段130と、を有し、前記差電流から第5の電流−電圧変換回路105を介して出力電圧Vrefを得る。

(もっと読む)

温度検出回路

【課題】低電圧動作や低消費電力化を図ることができる高精度な温度検出回路を得る。

【解決手段】2つの電界効果トランジスタのゲート電極の仕事関数差を用いて、負の温度係数を有する電圧VPNを生成する第1の電圧源回路2と、2つの電界効果トランジスタにおけるゲート電極の仕事関数差を用いて、正の温度係数を有する電圧VNNを生成する第2の電圧源回路3と、電圧VPNと電圧VNNとの減算を行い、該差分を増幅する減算回路5とを備えるようにした。

(もっと読む)

リファレンス電圧生成装置

【課題】 電源電圧変化,温度変化,デバイスばらつきに対して安定な基準電圧を生成する。

【解決手段】 電源電圧とデバイスばらつきに依存せず温度に依存する基準電圧を生成する温度依存電圧生成手段11と、電源電圧と温度に依存せずデバイスばらつきに依存する基準電圧を生成するデバイス依存電圧生成手段12と、電源電圧に依存せず温度とデバイスばらつきに依存する基準電圧を生成する温度・デバイス依存電圧生成手段13とを有し、温度依存電圧生成手段11によって生成された基準電圧VTと、デバイス依存電圧生成手段12によって生成された基準電圧VDと、温度・デバイス依存電圧生成手段13によって生成された基準電圧VVとを、所定の係数をもって加減算することによって、温度,電源電圧,デバイスのばらつきに依存しない基準電圧VREFを生成する。

(もっと読む)

基準電圧発生回路およびそれを内蔵した半導体集積回路

【課題】 低電圧で電圧変動が比較的大きい電源電圧であっても温度依存性がなくかつ精度の高い基準電圧を生成することが可能であり、特に無線タグICに内蔵するのに好適な基準電圧発生回路を提供する。

【解決手段】 電源電圧依存性のない電流を流す第1の定電流源(Mp3)と直列に第1のMOSFET(Mn3)を接続し、第1の定電流源が流す電流は該第1のMOSFETを飽和領域で動作させる大きさとし、第1のMOSFETとカレントミラー接続されて第1の定電流源と同一の電流を流す第2の定電流源として作用する第2のMOSFET(Mn4)を設ける。そして、該第2のMOSFETと直列に第1のMOSFETのしきい値電圧よりも小さなしきい値電圧を有する第3のMOSFET(MnL1)を接続して、第2のMOSFETと第3のMOSFETとの結合点から、上記第1のMOSFETと第3のMOSFETのしきい値電圧差に相当する電圧を取り出すように基準電圧発生回路を構成した。

(もっと読む)

基準電圧発生回路

【課題】高ビット数のA/Dコンバータにも利用可能な、温度変化による出力電圧の変化の少ない精密な基準電圧発生回路を提供する。

【解決手段】温度補償された基準電圧発生回路は、ゼロ温度係数点を有する基準電圧発生部1と補償回路部10とからなる。補償回路部10は、基準電圧発生部1の出力を入力として温度補償を行う。そして、補償回路部10には、ゼロ温度係数点より低い領域において温度の上昇に対してドレイン電流が増加する特性を有する第1MOSトランジスタ101と、ゼロ温度係数点より高い領域において温度の上昇に対してドレイン電流が減少する特性を有する第2MOSトランジスタ102とが含まれる。さらに、これらの2つのドレイン電流に対応する電流を加算して出力する、出力端子Vrefを有する加算回路110とを有する。

(もっと読む)

基準電圧発生回路および半導体集積回路並びに半導体集積回路装置

【課題】 温度依存性の低い約1.2V以下の基準電圧を発生可能で、差動アンプのオフセット電圧依存性も小さくしたバンドギャップ型の基準電圧発生回路。

【解決手段】 バンドギャップ部(10)は、電源電圧端子間に直列に接続された第1抵抗(R1)およびバイポーラトランジスタ(BT1)と、電源端子間に直列に接続された第2抵抗(R2)−バイポーラトランジスタ(BT2)−第3抵抗(R3)と、第1抵抗と第2抵抗でそれぞれ生じた電圧を入力とする差動増幅回路(AMP1)とからなり、差動増幅回路の出力がトランジスタ(BT1,BT2)のベースに印加される。出力部(20)は、差動増幅回路の出力がベースに印加されるバイポーラトランジスタ(BT3)と、トランジスタと直列接続された抵抗(R4)と、トランジスタ電流を転写するカレントミラー回路(21;MT1,MT2)と、電圧変換する抵抗(R5)およびダイオード(BT4)とを有する。

(もっと読む)

バンド・ギャップ基準から可変出力電圧を生成する方法及び装置

【課題】電圧基準回路から可変出力電圧を生成する方法及び装置を提供すること。

【解決手段】電圧基準回路は、負の温度係数を有する第1の電圧信号を生成する第1の電圧発生器と、正の温度係数を有する第2の電圧信号を生成する第2の電圧発生器とを備える。電圧基準回路は、基準電流を第1の電圧発生器及び第2の電圧発生器に供給する電流発生器を更に備える。第1の電圧信号を第2の電圧信号と比較する比較器が比較結果を生成し、比較結果に関係付けられた電流変化で基準電流を修正する。電圧基準回路は、電流発生器に結合された出力端末を備え、出力端末はバンド・ギャップ電圧より高い電圧差であって温度変化に実質的に依存しない電圧を含む。

(もっと読む)

基準電圧発生回路

【課題】 基準電流源となるデプレッション型のMOSトランジスタが基板バイアス効果やチャネル長変調効果の影響を受けることがないようにする。

【解決手段】 基板バイアス無しで基準電流源として働くデプレッション型のNMOSトランジスタMD1と、ダイオード接続のエンハンスメント型のNMOSトランジスタMN1と、制御入力端子1Bに入力する電圧に応じたバイアス電流をバイアス出力端子1C,1DからMOSトランジスタMD1、MN1のドレインに供給するバイアス回路1と、MOSトランジスタMD1のドレイン電圧とMOSトランジスタMN1のドレイン電圧の差分に対応する電圧をバイアス回路1の制御入力端子1Bに出力する差動増幅器3とを具備し、MOSトランジスタMD1のドレイン電流と同じ電流をMOSトランジスタMN1に供給し、両ドレイン電圧が同一となるよう制御して、MOSトランジスタMN1のゲート・ソース間の電圧を基準電圧Vrefとして出力する。

(もっと読む)

スイッチングレギュレータ及びこれを備えた電子機器

【課題】本発明は、変換効率の低下を招くことなく、ノイズ環境下での出力精度を向上することが可能なスイッチングレギュレータを提供することを目的とする。

【解決手段】本発明に係るスイッチングレギュレータ20は、センス抵抗Rsと、センス電圧Vsenseに応じたセンス電流Isenseを生成するセンス電流生成回路213と、ランプ波或いは三角波のスロープ電流Islopeを生成するスロープ電流生成回路214と、加算電流(Isense+Islope)に応じたスロープ電圧Vslopeを生成するスロープ電圧生成回路215と、出力誤差に応じた誤差電圧Verrを生成する誤差増幅器ERRと、誤差電圧Verrとスロープ電圧Vslopeを比較してPWM信号を生成するコンパレータCMPと、PWM信号に基づいて出力トランジスタN1のオン/オフ制御を行うスイッチング制御部CTRLと、を有して成る構成としている。

(もっと読む)

三相コンデンサを三相遮断機で同期開閉する装置

【課題】コンデンサを遮断機で開閉する装置とリアクトルをSCRで制御する装置を並列運転するにあたって、コンデンサの突入電流をなくし、リアクトル電流との連続性を保つようにするのが本発明の課題である。

【解決手段】コンデンサ開閉用の三相遮断機のある相にダイオードを接続し、他の相に抵抗を接続してコンデンサには波高値と同じ直流電圧を充電し、交流電圧が直流電圧と一致したとき三相遮断機を閉じる。

三相遮断機を開くタイミングは閉じるタイミングより、アーク時間、三相遮断機のばらつきを加算して決定する。

コンデンサの開閉タイミングを予知しリアクトルの通電電流を制御するSCRの制御遅れを加算してSCRを制御する。

(もっと読む)

101 - 120 / 138

[ Back to top ]