Fターム[5H420NB22]の内容

電気的変量の制御(交流、直流、電力等) (13,664) | 出力部 (2,015) | 出力制御回路に付加された素子 (700) | 抵抗 (138)

Fターム[5H420NB22]に分類される特許

121 - 138 / 138

電源回路

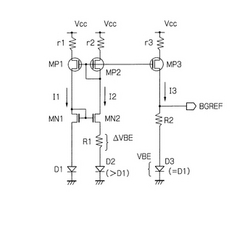

【課題】 デバイス特性のバラツキによる出力電圧への影響を低減した電源回路を提供する。

【解決手段】 電源回路は、カレントミラーを有する構成であり、基準電圧を発生させる。複数のトランジスタMP1〜MP3がカレントミラーを構成する。複数のバラツキ緩和用素子r1〜r3がトランジスタMP1〜MP3の各々に直列に接続されており、トランジスタMP1〜MP3の特性バラツキの影響を低減する。それにより、デバイス特性のバラツキによる電源回路の出力電圧への影響が低減される。

(もっと読む)

バンドギャップ基準電圧回路および温度曲率補正された基準電圧の生成方法

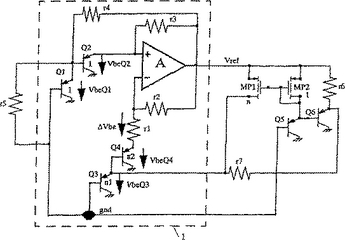

第1カレントミラー回路(10)は、PTAT電流(12ないし15)を第1および第2トランジスタ(Q1ないしQ4)に供給し、演算増幅器(A1)は、第1トランジスタスタック(8)の第1トランジスタ(Q2)のエミッタの電圧を抵抗(R1)と同じレベルに維持すると共に、第1カレントミラー回路(10)からPTAT電流を引き込む。主抵抗(R1)を通じて発生された補正PTAT電圧(dVbe)は、副抵抗(R3)でスケーリングされ、第1トランジスタ(Q1)の未補正ベース・エミッタ電圧CTATと合算される。CTAT補正電流はPTAT電流(13)と合算され、そして、主抵抗(R1)を通じて発生される補正PTAT電圧(dVbe)が第1トランジスタ(Q1)の未補正ベース・エミッタ電圧CTATのTlnT温度曲率と相補的なTlnT曲率を有するように、第2トランジスタ(Q3)のエミッタに印加される。  (もっと読む)

(もっと読む)

基準電圧回路

【課題】素子バラツキの影響が出力電圧特性のバラツキに現れるという問題を解決する。

【解決手段】第1の電流−電圧変換回路と第2の電流−電圧変換回路の電圧が等しくなるように制御する制御手段(AP1)を有し、前記第1または第2の電流−電圧変換回路に供給される電流値に比例する電流を出力する第1のカレントミラー回路を有し、前記第1のカレントミラー回路からの出力電流を第3の電流−電圧変換回路を介して電圧に変換して供給する基準電圧回路において、前記第1、第2および第3の電流−電圧変換回路は、第1のダイオード(またはダイオード接続された第1のバイポーラトランジスタ)と第1の抵抗R1が直列接続され、さらに第2の抵抗R2が並列接続されてなるか、あるいは、第1のダイオード(またはダイオード接続された第2のバイポーラトランジスタ)と第1の抵抗R2が並列接続され、さらに第2の抵抗が直列接続される。

(もっと読む)

基準電圧発生回路及びこれを用いた電源電圧監視回路

【課題】 低い電源電圧でも高精度な基準電圧を発生できると共に、外部から印加される初期化信号や複数の定電流源を必要とすることなく、回路の安定した起動を実現できる基準電圧発生回路を提供する。

【解決手段】 この基準電圧発生回路は、2つのPN接合を含む回路に発生する2つの電圧を入力して出力電圧を生成する差動増幅部と、2つのPN接合に電流を供給する電流供給部と、起動信号に従って差動増幅部の動作を第1の安定状態から第2の安定状態に移行させるために電流供給部を制御する制御部とを含み、差動増幅部の出力電圧に基づいて生成された第1の電圧を分圧して基準電圧として出力する定電圧回路20と、第1の電圧に基づいて差動増幅部の動作が第1の安定状態を経過するまで起動信号を活性化する起動回路10と、起動信号が活性化されているときに第1の電圧を減少させる起動促進回路30とを具備する。

(もっと読む)

基準電圧回路

【課題】 2個ダイオードを用い、チップ面積が小さいCMOS基準電圧回路を実現する。

【解決手段】 基準電圧回路は、第1電流−電圧変換回路13と、第2電流−電圧変換回路15の電圧が等しくなるように制御する制御部を有し、回路13または15に供給される電流値に比例する電流を出力する第1カレントミラー回路を有し、前記第1カレントミラー回路からの出力電流を第3抵抗を介して流すことにより電圧を供給する。回路13は第1ダイオードで構成され、回路15は第2ダイオードと第1抵抗が直列接続され、さらに第2抵抗が並列接続されてなる。

(もっと読む)

低電圧動作回路

【課題】バンドギャップ型基準電圧発生回路や定電流発生回路を効果的に動作させる低電圧動作回路を提供する。

【解決手段】電流ミラー回路と、前記電流ミラー回路の出力電流が供給される出力トランジスタと、を有するバンドギャップ型基準電圧発生回路を動作させる低電圧動作回路であって、前記電流ミラー回路を構成するダイオード接続された一方のトランジスタと直列接続される第1トランジスタと、前記出力トランジスタと直列接続されるとともに、前記第1トランジスタと制御電極が共通接続される第2トランジスタと、前記第1トランジスタの制御電極と、前記第1トランジスタの前記一方のトランジスタの側となる電極との電位差を、所定値以下とする複数の第3トランジスタと、を備え、前記第1トランジスタ、前記第2トランジスタ、前記複数の第3トランジスタは、電流ミラー回路を構成する。

(もっと読む)

定電流回路及びその定電流回路を使用したシステム電源装置

【課題】 製造プロセスの変動や温度変動に対する変動を低減させて高精度の複数の定電流を生成しバイアス電流として供給することができる定電流回路及びその定電流回路を使用したシステム電源装置を得る。

【解決手段】 PMOSトランジスタM1及びM2から流れる各電流i1及びi2の一方の電流の変動に対して負帰還がかけられてその変動を打ち消すように、演算増幅回路AMPがPMOSトランジスタM1及びM2の動作制御を行い、PMOSトランジスタM1及びM2から対応して電流が供給される2つのpnpトランジスタQ1及びQ2に流れる電流密度の差によって生じる電位差に接続した抵抗R1に流れる定電流を基準電流とし、演算増幅回路AMPによって動作制御されたPMOSトランジスタMA1〜MAnで該基準電流に比例した各電流をそれぞれ生成して出力するようにした。

(もっと読む)

高電源電圧除去比(PSRR)を有し曲線補正されたバンドギャップ型電圧基準回路

PTATおよびCTAT生成構成要素を含む、電圧基準回路が提供される。CTAT構成要素は、演算増幅器の回りのフィードバック構成内に設けられ、増幅器の入力に結合された、PTAT生成構成要素と組み合わされる。このCTAT構成要素とPTAT構成要素の組み合せは、回路の出力電圧の温度曲線補正を提供するように、実現される。  (もっと読む)

(もっと読む)

基準回路

基準回路(200,300)は、第2のトランジスタ(Q2,222)に動作可能に結合された第1のトランジスタ(Q1,220)を備え且つ基準回路の正の温度依存性に対応するそれぞれのベース電流(IbQ1,IbQ2)を有する第1の電流発生器を備える。抵抗(r3228)は、第1の電流発生器に動作可能に結合され、且つ基準回路の負の温度依存性に対応する第2の電流(Ir3)を与えるよう構成されている。第2の電流発生器(m4224)が、抵抗及び第1の電流発生器に動作可能に結合され、第2の電流(Ir3)及びベース電流(IbQ1,IbQ2)の和として組み合わされた電流(I2)を発生する。このようにして、湾曲補償した電圧及び/又は電流基準回路の出力電圧は、実質的に線形であり、そして当該基準回路の動作温度に対して実質的に独立である。  (もっと読む)

(もっと読む)

半導体装置及びその半導体装置を使用したボルテージレギュレータ

【課題】 モニタトランジスタを使用してドライバトランジスタに流れる電流を正確に検出することができる半導体装置及びその半導体装置を使用したボルテージレギュレータを得る。

【解決手段】 ドライバトランジスタM1に流れる電流を検出するため、ドライバトランジスタM1に並列に接続された複数のPMOSトランジスタQ1〜Q4で形成したモニタトランジスタM11を備え、半導体チップ21において、各PMOSトランジスタQ1〜Q4が形成された領域AQ1〜AQ4をドライバトランジスタM1が形成されている領域AM1の周囲、又は該領域AM1内に配置するようにした。

(もっと読む)

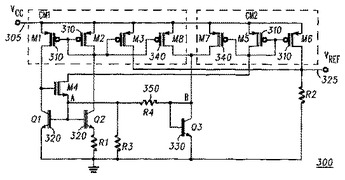

バンドギャップ型基準電圧発生回路

【課題】任意の出力電圧を供給する基準電圧発生回路を提供する。

【解決手段】MOSトランジスタM1、M2は第1のカレントミラーを構成する。MOSトランジスタM2、M3は第2のカレントミラーを構成する。MOSトランジスタM3のドレインは、抵抗R4を介して接地に接続される。MOSトランジスタM4、M5は第3のカレントミラーを構成する。MOSトランジスタM4のドレインは抵抗R1を介してBIPトランジスタQ1に接続され、MOSトランジスタM5のドレインはBIPトランジスタQ2〜QK+1に接続される。BIPトランジスタQ1のベ−スはMOSトランジスタM5と抵抗R1の接続点に接続される。前記接続点は抵抗R2を介して接地に接続される。BIPトランジスタQ2〜QK+1のベ−スはBIPトランジスタQ1に接続される。MOSトランジスタM5とBIPトランジスタQ2〜QK+1の接続点は抵抗R3を介して接地へ接続される。

(もっと読む)

基準電圧発生回路

【課題】 出力電圧の温度特性を改善して,保証温度範囲を特に高温側に広げた基準電圧発生回路を提供すること。

【解決手段】 トランジスタQ1のベース−エミッタ間電圧に差動増幅器Tの出力電圧を加えた電圧VBGを出力するバンドギャップ回路1に対し,補償電流印加回路2を付加した。補償電流印加回路2は,高温域で,逆方向電圧の掛かったPN接合のリーク電流を増幅した電流をバンドギャップ回路1に印加する。これにより,バンドギャップ回路1の出力電圧VBGの温度特性が負となる高温域において,補償電流印加回路2の印加電流によりトランジスタQ1のベース−エミッタ間電圧を増加させ,温度特性を緩和している。かくして,より広い温度範囲内で,許容範囲内の出力電圧VBGが得られるようになっている。

(もっと読む)

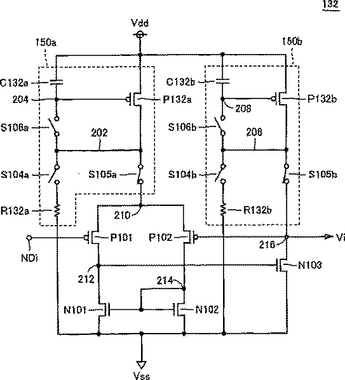

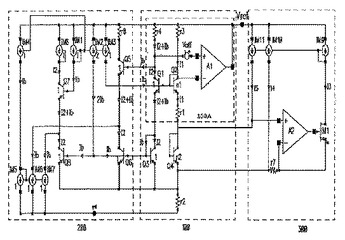

定電流回路、駆動回路および画像表示装置

電圧発生回路114に含まれる第1の増幅回路(132)は、P型TFT素子(P101,P102)およびN型TFT素子(N101,N102)によって構成される差動回路と、定電流回路(150a,150b)と、N型TFT素子(N103)とを含む。定電流回路(150a;150b)は、P型TFT素子(P132a;P132b)と、キャパシタ(C132a;C132b)と、スイッチ(S104a〜S106a;S104b〜S106b)と、抵抗素子(R132a;R132b)とからなる。キャパシタ(C132a;C132b)は、電圧設定時、すなわちダイオード接続されるP型TFT素子(P132a;P132b)に電流が供給されているときのノード(204;208)の電圧を保持する。  (もっと読む)

(もっと読む)

カレントミラー回路

【課題】 接地との間に入力電流を形成するタイプのカレントミラー回路であって、npn型トランジスタを用いて構成されるものを提供すること。

【解決手段】 トランジスタQ1のエミッタとトランジスタQ2のベースとトランジスタQ3のベースとが互いに接続され、トランジスタQ2のコレクタには抵抗器の一端が接続され、抵抗器の他端には電源が接続され、トランジスタQ1のベースには抵抗器の前記一端が直接又は間接的に接続され、トランジスタQ1のコレクタが電源に接続され、トランジスタQ2のエミッタとトランジスタQ3のエミッタとが共に直接又は間接的に接地され、トランジスタQ1のベースと接地との間に入力電流を形成することで、トランジスタQ3のコレクタ電流として出力電流を形成する。

(もっと読む)

基準電圧発生回路

【課題】低消費電力化が図れる基準電圧発生回路を実現する。

【解決手段】基準電圧発生回路は、出力端に所定の電圧を出力するバンドギャップ回路11と、複数のカレントミラー回路を含み、少なくとも一つのカレントミラー回路のゲート電極は一方の電流経路に接続され、少なくとも他の1つのカレントミラー回路のゲート電極は他方の電流経路に接続され、かつ、一方又は他方の電流経路に流れる電流に応じた出力電流を出力端に供給するようにバンドギャップ回路に接続された複数カレントミラー回路32と、バンドギャップ回路の出力端の出力電圧を検出し、検出した出力電圧に応じて、一方の電流経路と他方の電流経路の少なくとも一方に流れる電流を制御する制御手段31とを有する。

(もっと読む)

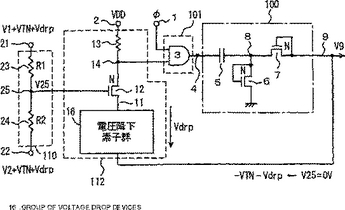

電圧検出回路およびこれを用いた内部電圧発生回路

所望の電圧の内部電圧を安定に生成する内部電圧発生回路及び電圧検出回路を提供する。電圧検出回路は、基準電圧をゲートに受ける絶縁ゲート型電界効果トランジスタと、この絶縁ゲート型電界効果トランジスタと直列に内部ノードの間に接続される電圧降下素子群を含む。基準電圧は、この絶縁ゲート型電界効果トランジスタのしきい値電圧と降下電圧を電圧成分として含む電源電圧を抵抗分割して生成される。基準電圧と内部電圧との差が所定値以上となると、この電圧降下素子群および絶縁ゲート型電界効果トランジスタに電流が流れ、検出ノードの電圧が低下し、内部電圧の低下が検出される。基準電圧はこのトランジスタのしきい値電圧及び電圧降下素子群の降下電圧を構成要素として含んでおり、これらのパラメータのばらつきを相殺して抵抗分割に所望の電圧を設定する。  (もっと読む)

(もっと読む)

改良型バンドギャップ基準電圧

ノイズおよび増幅器オフセットに対する感受性が低減された、バンドギャップ基準電圧が記載されている。バイアスが印加されたときに構成要素のトランジスタのベース幅が変化しないように回路を構成することにより、アーリー効果を取り除くことが可能となる。

(もっと読む)

(もっと読む)

定電流回路、記録素子基板及び記録装置

【課題】 温度変化や駆動素子の特性に影響されず、負荷に流れる電流を一定とする。

【解決手段】 負荷101と、負荷に直列に接続された駆動用トランジスタ102と、定電流源103と、PMOS差動対を構成し、それぞれのソースが定電流源103の出力に共通に接続され、それぞれのドレインがカレントミラー回路を構成するNMOSトランジスタ106及び107のドレインにそれぞれ接続されたPMOSトランジスタ104及び105とを設け、駆動用トランジスタ102のドレインの電位を一定とすることにより、負荷101に流れる電流を一定とする。

(もっと読む)

121 - 138 / 138

[ Back to top ]