Fターム[5H730BB02]の内容

DC−DCコンバータ (106,849) | 主変換部の型式 (20,669) | 充放電型(直並列切換) (1,313) | 昇圧型 (836)

Fターム[5H730BB02]に分類される特許

1 - 20 / 836

半導体装置

半導体装置

【課題】作製工程が簡略化され、容量素子の面積が縮小化された昇圧回路を有する半導体

装置を提供することを課題とする。

【解決手段】直列に接続され、第1の入力端子部から出力端子部へ整流作用を示す複数の

整流素子と、第2の入力端子部に接続され、互いに反転する信号が入力される第1の配線

及び第2の配線と、それぞれ第1の電極、絶縁膜及び第2の電極を有し、昇圧された電位

を保持する複数の容量素子とから構成される昇圧回路を有し、複数の容量素子は、第1の

電極及び第2の電極が導電膜で設けられた容量素子と、少なくとも第2の電極が半導体膜

で設けられた容量素子とを有し、複数の容量素子において少なくとも1段目の容量素子を

第1の電極及び第2の電極が導電膜で設けられた容量素子とする。

(もっと読む)

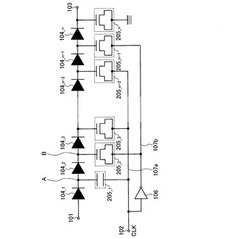

チャージポンプ回路及びこれを用いた電源装置

【課題】容易にかつ適切にFETのオン/オフ制御を行う。

【解決手段】チャージポンプ回路1は、キャパシタC1の充放電用スイッチとして用いられるFET103(104)と、FET103(104)に流れる電流またはFET103(104)の両端電圧に応じて検出信号S11(S12)を生成する検出部109(110)と、検出信号S11(S12)に応じてFET103(104)の駆動信号G11(G12)を生成する駆動部107(108)と、を有する。

(もっと読む)

チャージポンプ回路およびそれを用いた半導体装置

【課題】起動時の消費電流を小さく抑制できるチャージポンプ回路を提供する。

【解決手段】このチャージポンプ回路30では、ポンプ回路10の起動期間は分周クロック信号CLKDをポンプ回路10に与えてポンプ回路10の電流供給能力を低く設定し、起動期間の終了後はクロック信号CLKをポンプ回路10に与えてポンプ回路10の電流供給能力を高く設定する。したがって、起動期間はポンプ回路10の消費電流を小さく抑制し、起動期間の終了後はポンプ回路10の電流供給能力を高めることができる。

(もっと読む)

昇圧回路及びその給電方法

【課題】簡略化された回路構成でノイズ低減効果を持つ多相駆動型の昇圧回路を実現する。

【解決手段】昇圧回路は、所定周期のクロック信号を出力する発振回路と、前記クロック信号の1本の配線に直列接続され、トータル遅延時間が前記所定周期よりも長い複数の遅延回路と、前記複数の遅延回路に対応して前記1本の配線に接続された複数の分割昇圧回路と、を含む。

(もっと読む)

過電圧保護回路

【課題】外部から供給される直流電圧が低下した場合における電源電圧の低下を抑制するとともに、負荷に対する過電流制限機能を実現する。

【解決手段】主トランジスタT1は、コレクタが直流電源線3に接続される。主トランジスタT1のエミッタおよび直流電源線4を通じて負荷回路6に対して電源電圧Vdが供給される。定電圧回路7は、直流電源線3、4間の直流電圧VBをクランプ値でクランプした定電圧Vaを出力する。昇圧回路8は、電源電圧Vdを昇圧した昇圧電圧Vbを出力する。電圧選択回路9は、定電圧Vaおよび昇圧電圧Vbのうち、高い電圧を主トランジスタT1のベースに与える。昇圧回路は、直流電圧VBがクランプ値以上であるときに昇圧動作を停止する。

(もっと読む)

チャージポンプ及びこれを用いた電源装置

【課題】プリント配線基板上の実装面積削減やコスト削減を実現することのできるチャージポンプを提供する。

【解決手段】チャージポンプ100は、フライングキャパシタ120の充放電用スイッチとして、半導体装置110に集積化されたフローティングNMOSFET111及び112のボディダイオード111d及び112dを用いる。

(もっと読む)

半導体装置及びこれを備える情報処理装置

【課題】安定したチャージポンプ動作を行う。

【解決手段】ノードA,Bを有するコンデンサC1と、VDDレベルからVSSレベルの間で振幅するポンピング信号PUMP1をコンデンサC1のノードAに供給するポンピング回路110と、コンデンサC1のノードBをVPPextレベルにプリチャージし、ポンピング信号PUMP1がVSSレベルからVDDレベルに変わった時に、コンデンサC1のノードBをVPPextレベルよりも高いレベルに駆動する出力回路120とを備える。本発明によれば、コンデンサC1のノードAをポンピングするための電圧と、コンデンサC1のノードBをプリチャージするための電圧が異なっていることから、昇圧電圧を効率よく生成することできる。

(もっと読む)

半導体集積回路及びその制御方法

【課題】デカップリング容量素子の信頼性と、フラッシュメモリの動作モードに対応した供給電流の補償を損なわずに、フラッシュメモリの面積増加を抑制する。

【解決手段】本発明に係る半導体集積回路10は、フラッシュメモリ部12と、フラッシュメモリ部12に電圧を供給する昇圧回路13と、昇圧回路13の出力に一端が接続されたデカップリング容量素子15と、フラッシュメモリ部12の動作モードに応じて、デカップリング容量素子15の他端の電位を制御する制御回路14とを備える。

(もっと読む)

撮像素子モジュール及びその電源回路

【課題】インダクタを備える昇降圧スイッチング回路の昇降圧動作によって、インダクタで発生する電磁ノイズが撮影画像に影響を与えないようにする。

【解決手段】撮像素子モジュールの電源回路5-4であって、スイッチングトランジスタ22,23及びインダクタ6により入力直流電圧を降圧して出力する降圧回路部20と、降圧回路部20と並列に設けられトランジスタ31のリニア定電圧動作によって入力直流電圧を降圧して出力するリニアレギュレータ回路部30と、降圧回路部20の前段又は後段に直列に接続され入力直流電圧をチャージポンプ動作又はチャージポンプ動作と昇圧スイッチング動作の切替によって昇圧して出力する昇圧回路部40と、撮像素子モジュールの撮影記録モード時に降圧回路部20の動作を停止させると共にリニアレギュレータ回路部30を動作させて撮像素子の駆動に必要な定電圧を供給させる制御コントロール部56とを備える。

(もっと読む)

チャージポンプ回路およびその制御回路、オーディオ信号処理回路、電子機器

【課題】昇圧率の切りかえの際に、電流の逆流を防止する。

【解決手段】コントローラ10は、第1スイッチSW1から第7スイッチSW7のオン、オフ状態を制御することにより、(1)第1モードにおいて、第3端子P3に入力電圧VDDを、第4端子P4に入力電圧VDDを反転した負電圧−VDDを発生させ、(2)第2モードにおいて、第3端子P3に入力電圧VDDの略1/2倍の電圧を、第4端子P4に、入力電圧VDDの略1/2倍の電圧を反転した負電圧−VDD/2を発生させる。コントローラ10は、第1モードから第2モードへの移行を指示されると、遷移期間にわたり、第3スイッチおよび第5スイッチをオンする第1状態と、第2スイッチおよび第4スイッチをオンする第2状態と、を交互に繰り返す第3モードで動作し、その後、第2モードで動作する。

(もっと読む)

オーディオ信号処理回路および電子機器

【課題】アンプに対する電源電圧を好適に制御する。

【解決手段】メインアンプ4は、オーディオ信号S1を増幅する。電源回路2は、アンプの上側電源ラインに正の電源電圧CPVDDを、下側電源ラインに負の電源電圧CPVSSを供給する。電圧検出部32は、アンプにより増幅されたオーディオ信号S2の振幅が所定のしきい値より大きいときアサートされる電圧検出信号S21を生成する。電流検出部34は、メインアンプ4の出力段に流れる負荷電流ILが所定のしきい値電流ITHより大きいときアサートされる電流検出信号S22を生成する。電圧制御部30は、電圧検出信号S21がネゲートされると、電源回路2が生成する正および負の電源電圧の絶対値を低下させる。また電圧検出信号S21がアサートされ、または電流検出信号S22がアサートされると、電源回路2が生成する正および負の電源電圧の絶対値を増大させる。

(もっと読む)

昇圧回路

【課題】損失を抑制すると共により迅速に昇圧を行なう。

【解決手段】チャージポンプ20からの出力電圧VCがトリガ電圧を超えると、スイッチ70がオンし、クロック信号供給回路30は出力電圧VCの振幅のクロック信号CKmos,CKBmosをチャージポンプ20に出力し、クロック信号供給回路40は出力電圧VCの振幅のクロック信号CKmosを用いてクロック信号CKcap,CKBcapを生成してチャージポンプ20に出力し、チャージポンプ20では、各トランジスタのゲートへ出力電圧VCの振幅のクロック信号CKmos,CKBmosが供給され、各キャパシタの他端へ立ち上がり時間の小さいクロック信号CKcap,CKBcapが供給される。これにより、昇圧回路10全体の損失を抑制すると共により迅速に出力電圧VCを目標出力電圧に昇圧することができる。

(もっと読む)

マルチレベルインバータ回路

【課題】4レベル以上のダイオードクランプ形マルチレベルインバータであっても、DCリンクコンデンサの電圧均一性を確保することのできるマルチレベルインバータ回路を提供する。

【解決手段】本発明に係るマルチレベルインバータ回路は、共振形スイッチトキャパシターコンバータを用い手いることを特徴のひとつとする。また、マルチレベルインバータ回路は、マルチレベルインバータ部と、マルチレベルインバータ部とDCリンクコンデンサ部を介して接続されるRSCC部と、を有することを特徴とする。

(もっと読む)

キャパシタプリチャージ回路、モータ駆動システム、電動パワーステアリングシステム、エアバッグシステム

【課題】キャパシタプリチャージ回路における損失(発熱)を低減させ、回路を小型化する。

【解決手段】本発明に係るキャパシタプリチャージ回路は、スイッチドキャパシタ分圧回路を用いて電源電圧を分圧することにより、チャージ対象であるキャパシタの両端電圧を抑制しながら充電する。

(もっと読む)

チャージポンプにおいて電流をクランプする回路

【課題】

チャージポンプにおいて電流をクランプする回路が開示される。

【解決手段】

チャージポンプは、複数のスイッチング回路トランジスタを有するスイッチング回路を備える。同回路における第1及び第2の対のトランジスタの各々は、スイッチング回路トランジスタの内の対応する1つからの電流に対して、電流におけるスパイクが、同スイッチング回路トランジスタとチャージポンプのキャパシタとの間を通る経路を通って部分的にだけ伝送されるように、そのトランジスタがオフに切り替わっている間に追加経路を提供することができる。

(もっと読む)

昇圧回路

【課題】負荷電流に応じて昇圧能力を調整することにより、過剰な昇圧回路出力リップルを抑制する。

【解決手段】昇圧回路1は、昇圧部出力CPOの電圧を変動させて昇圧回路出力VPPを生成し、昇圧回路出力VPPの負荷電流の大きさに応じて制御電圧CON1を生成する制御部2と、制御電圧CON1に応じて電源VDDP1の電圧を変動させることにより昇圧部電源VDDPを生成する電源降圧部3と、昇圧回路出力VPPの電圧と目標電圧との差分に応じて昇圧部電源VDDPの電圧を変動させることにより昇圧部出力CPOを生成する昇圧部4とを備える。

(もっと読む)

半導体装置

【課題】昇圧効率を向上させた昇圧回路を提供することを課題の一とする。または、昇圧効率を向上させた昇圧回路を用いたRFIDタグを提供することを課題の一とする。

【解決手段】単位昇圧回路の出力端子に当たるノード、または当該ノードに接続されたトランジスタのゲート電極をブートストラップ動作により昇圧することで、当該トランジスタにおけるしきい値電位と同等の電位の低下を防ぎ、当該単位昇圧回路の出力電位の低下を防ぐことができる。

(もっと読む)

電圧生成回路、半導体装置及び電圧生成回路の制御方法

【課題】外部電圧に応じた能力にて内部電圧を生成すること。

【解決手段】昇圧部20は直列接続された3つのポンプ回路21〜23を備える。各ポンプ回路21〜23は、発振部31にて生成されたクロック信号CLK1に基づいてポンピング動作し、入力電圧を昇圧した電圧を生成する。従って、昇圧部20は、外部電圧Vddを、各ポンプ回路21〜23により昇圧して内部電圧Vppを生成する。制御部32は、内部電圧Vppの変化量を検出し、その検出結果(変化量)に応じて昇圧部20に含まれるポンプ回路21〜23の段数を制御する。

(もっと読む)

電圧増倍回路

【課題】入力電圧を上げ、電気的な負荷に、その閾値電圧よりも低い低電圧の入力から電力供給し、従来技術による回路よりも消費電流が少なく製造が安価で小型である、電圧増倍回路を提供すること。

【解決手段】電圧Vdcが回路の第1の入力に印加される増倍回路(100)であって、第1のキャパシタ(104)および第2のキャパシタ(106)と、第1の状態において、各キャパシタの第1の端子をゼロ電位に、各キャパシタの第2の端子をVdcに等しい電位に電気的に結合でき、第2の状態において、第1のキャパシタの第1の端子を電位Vdcに、第2のキャパシタの第2の端子をゼロ電位に、第1のキャパシタの第2の端子を第1の出力端子に、第2のキャパシタの第1の端子を第2の出力端子に電気的に結合できる、結合手段(108、110、112、114)と、一方の状態からもう一方の状態への変化を制御できる、制御手段(116)と、を含む、増倍回路。

(もっと読む)

1 - 20 / 836

[ Back to top ]