Fターム[5H740AA04]の内容

Fターム[5H740AA04]に分類される特許

81 - 100 / 444

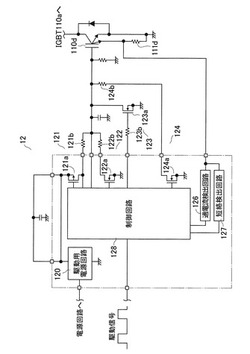

電子装置

【課題】オン駆動用スイッチング素子がオン故障等した場合であっても、スイッチング素子の熱破壊を防止することができる電子装置を提供する。

【解決手段】オン駆動用抵抗121bとオフ駆動用抵抗122bの抵抗値は、オン駆動用FET121aとオフ駆動用FET122aがともにオンした場合に、IGBT110dのゲート電圧が、オン電圧が増加するオン、オフの閾値電圧付近の所定範囲外であって、オン、オフの閾値電圧より低くなるように設定されている。そのため、オン駆動用FET121aがオン故障等したときにオフ駆動用FET122aがオンしても、オン電圧が増加してIGBT110dの発熱が増大することなく、IGBT110dをオフすることができる。従って、IGBT110dの熱破壊を防止することができる。

(もっと読む)

電力変換装置

【課題】自己インダクタンスを有する接続ラインを用いてなる電力変換装置において、スイッチング素子をターンオンまたはオフしたときに、電流経路とスナバコンデンサとが共振することを抑制することができ、配置の自由度を向上させることができる電力変換装置を提供する。

【解決手段】一対の接続ライン20、30の少なくとも一方の接続ラインに、当該接続ラインよりも自己インダクタンスが低いと共に抵抗値が高い補助配線21〜23、31〜33を備える。そして、補助配線21〜23、31〜33を含んで構成される電流経路の自己インダクタンスを、一対の接続ライン20、30を含んで構成される電流経路の自己インダクタンスより小さくする。

(もっと読む)

電子装置

【課題】オン駆動用スイッチング素子がオン故障してスイッチング素子をオフできない異常状態になっても、スイッチング素子の熱破壊を防止することができる電子装置を提供する。

【解決手段】制御回路128は、オン駆動用FET121aのゲート電圧がオンしない電圧であるにもかかわらず、ドレイン−ソース間電圧がオンした際の電圧であるとき、オン駆動用FET121aがオン故障していると判断する。そして、駆動用電源回路120の動作を停止させ、駆動用電源回路120からの電圧の供給を遮断する。その結果、ゲート電圧がオン、オフする閾値電圧より低くなり、IGBT110dがオフする。そのため、オン駆動用FET121aがオン故障してIGBT110dをオフできない異常状態になっても、IGBT110dの熱破壊を防止できる。

(もっと読む)

駆動装置

【課題】消費電力を低減した駆動装置を提供する。

【解決手段】コイルに電流を供給する第1N型MOSFETと、前記第1N型MOSFETと直列接続され、前記コイルから電流が供給される第2N型MOSFETと、前記第2N型MOSFETがオフしているときに前記第1N型MOSFETをオンするように第1駆動信号を出力する第1駆動回路と、前記第1N型MOSFETがオフしているときに前記第2N型MOSFETをオンするように第2駆動信号を出力する第2駆動回路と、ドレインソース路が前記第1駆動回路の出力及び前記第1N型MOSFETのゲートの間に接続されるP型MOSFETと、前記第1N型MOSFET及び前記P型MOSFETのゲートソース間電圧を共に所定電圧にクランプするクランプ回路と、前記P型MOSFETのドレインソースに並列接続される第1抵抗と、を備えた駆動装置である。

(もっと読む)

電源回路及び電力変換装置

【課題】本発明はキャリア周波数が増加しても出力電圧の低下を抑える電源回路を提供することである。

【解決手段】直流電力を交流電力に変換し、かつ上アームおよび下アームを構成する複数のスイッチング素子からなるインバータ回路と、前記複数のスイッチング素子を制御する制御回路と、前記制御回路からの信号に基づき、前記複数のスイッチング素子を駆動する駆動回路と、前記駆動回路に電力を供給する絶縁型電源回路と、を有し、前記制御回路は、前記電源回路から前記駆動回路に出力する電源電圧を制御し、前記駆動回路は、キャリア周波数、および前記電源電圧に基づいて前記複数のスイッチング素子を駆動し、前記電源回路は、前記駆動回路に出力された電圧を電源制御ICに出力するフィードバック回路を有し、前記フィードバック回路は前記キャリア周波数の変化に基づいて前記電源制御ICに出力する電圧を制御するダミー回路を有する。

(もっと読む)

電圧駆動型素子を駆動する駆動装置

【課題】出力電圧の異なる複数の電源を備えた、電圧駆動型素子を駆動する駆動装置で、駆動電源と電圧駆動型素子との接続部の電圧降下を抑制する。

【解決手段】 駆動装置の駆動電源は、複数の直流電源を備えており、複数の直流電源のうち、最も出力電圧の絶対値が大きい第1直流電源は、第1スイッチング素子を介して接続部と接続しており、複数の直流電源のうち、第1直流電源よりも出力電圧の絶対値が小さい1つ以上の第2直流電源の各々は、第2スイッチング素子および電流低減素子を介して接続部と接続している。第1スイッチング素子および第2スイッチング素子のそれぞれは、対応する直流電源と接続部とを導通状態と非導通状態とに切替えると共に、導通状態としたときに流れる電流と逆方向の電流の向きを順方向とする寄生ダイオードを有する半導体素子である。

(もっと読む)

ドライブ回路

【課題】1個のデッドタイム生成回路を用いて、直列に接続されている2つのスイッチング素子を駆動する2系統の信号のそれぞれ対してデッドタイムを設けることができ、IC化した場合に外付けコンデンサを1個にすることができるドライブ回路を提供する。

【解決手段】

コンデンサ13aを用いて信号Va0をデッドタイムよりも短い時間遅延させる遅延回路2aと、コンデンサ13bを用いて信号Vb0をデッドタイムよりも短い時間遅延させる遅延回路2bと、コンデンサ23を用い、信号Va0および信号Vb0の立ち上がりのタイミングからデットタイム分遅延させたタイミングで立ち上がる周期T/2のデッドタイム生成用信号V6を生成するデッドタイム生成回路3と、デッドタイム生成用信号V6に基づいてデッドタイムが設けられた信号Va7および信号Vb7とを生成するAND回路17a、17bとを設ける。

(もっと読む)

半導体素子の駆動装置及び方法

【課題】半導体素子のスイッチング時において、スイッチング損失の増加を抑制しつつ、サージ電圧を低減すること。

【解決手段】di/dt帰還部23は、IGBT11Uがターンオフするときに、IGBT11のコレクタ電流Icの時間変化に基づいて、帰還電圧VFBを生成する。また、di/dt帰還部23は、IGBT11がターンオンするときに、図示せぬFWDの転流電流IFWDに基づいて、帰還電圧VFBを生成する。このようなdi/dt帰還部23は、帰還電圧VFBを駆動信号の電圧の一部として印加するタイミングを遅延させる遅延フィルタとして、LPF回路201を備えている。LPF201の遅延量、即ちインダクタンスLdを適度に調整することで、還流ダイオードの電圧におけるサージ電圧を低減させることができる。

(もっと読む)

半導体素子の駆動装置及び方法

【課題】半導体素子のスイッチング時において、スイッチング損失の増加を抑制しつつ、サージ電圧を低減すること。

【解決手段】ターンオフ用di/dt帰還部23OFFは、IGBT11Uがターンオフするときに、IGBT11Uのコレクタ電流Icの時間変化に基づいて、帰還電圧VFBを生成する。ターンオン用di/dt帰還部23ONは、IGBT11Uがターンオンするときに、FWD12Dの転流電流IFWDに基づいて、帰還電圧VFBを生成する。この場合、ターンオン用di/dt帰還部23ONは、転流電流IFWの方向が、リバースリカバリー区間に対応する方向、即ち図13に示すFWD12Dのカソードからモータ等の負荷L側に流れる方向である場合、帰還電圧VFBを生成し、それ以外の場合、帰還電圧VFBの生成を禁止する。

(もっと読む)

半導体素子の駆動装置

【課題】半導体素子のスイッチング時において、スイッチング損失の増加を抑制しつつ、サージ電圧を低減すること。

【解決手段】電子回路1の半導体素子駆動回路13は、ゲート抵抗21と、電圧源22と、di/dt帰還部23と、バッファ111と、を備えている。バッファ111は、従来良く使われる方式であるトランジスタ111ta,111tbで構成されるIGBT駆動用のバッファ回路の少なくとも一部である。di/dt帰還部23は、トランス121と、抵抗122と、を備えている。即ち、トランス121が、di/dt検出部及びゲイン部に対応する。なお、電圧源22とバッファ111とを結ぶ経路に抵抗122が直列接続され、抵抗122の両端が、トランス121の2次側に接続されており、当該経路上の抵抗122の両端の間が、電圧源に対応する。

(もっと読む)

絶縁ゲート型デバイスの駆動回路

【課題】通常動作への影響(消費電流やRon)を低減しつつ、デバイスの誤オンの防止と高速ターンオフとを実現することができる絶縁ゲート型デバイスの駆動回路を提供する。

【解決手段】パワーMOSFET8のゲート−ソース間にパワーMOSFET8のゲート電圧を下げるためのゲート電圧制御用MOSFET14を設け、ゲート電圧制御用MOSFET14のゲート−ドレイン間にプルアップ素子としてN型デプレッションMOSFET25を設ける。そして、N型デプレッションMOSFET25を、パワーMOSFET8のドレイン電圧Vdが急激に持ち上げられたときに発生する、パワーMOSFET8のゲート−ドレイン間の寄生容量Cgdの充電電流Irによって駆動されるように構成する。

(もっと読む)

スイッチング素子の駆動装置

【課題】電圧制御形のスイッチング素子S*#の導通制御端子の電圧が正常時におけるシリーズレギュレータ22の出力電圧(ゲート印加電圧VgH)よりも低くなる中間電圧異常に対処できないこと。

【解決手段】ウィンドウコンパレータ70は、ゲート電圧Vgeが、スイッチング素子S*#がオン状態に切り替わる電圧とゲート印加電圧VgHとの間の中間電圧であると判断されることで、論理「H」の信号を出力する。この信号は、ローパスフィルタ72を介して中間電圧異常検出部74に取り込まれる。中間電圧異常検出部74では、ローパスフィルタ72の出力が論理「H」となることで、放電用スイッチング素子30、ソフト遮断用スイッチング素子42およびオフ保持用スイッチング素子60をオン操作して且つ、充電用スイッチング素子24およびシリーズレギュレータ22をオフ状態に切り替える。

(もっと読む)

ドライブ信号生成回路、制御装置、スイッチング電源装置、および、制御方法

【課題】発振信号にノイズが発生してデッドタイムパルスが短くなる場合でも、ハイサイドドライブ信号およびローサイドドライブ信号を切り替えて出力することが可能なドライブ信号生成回路を提供する。

【解決手段】ドライブ信号生成回路1は、第1のパルス信号を出力するデッドタイムパルス生成回路1aと、第2のパルス信号Aを出力するデッドタイム調整回路1bと、第3のパルス信号Bを出力する補償パルス生成回路1cと、第2のパルス信号Aと第3のパルス信号Bとの論理和を演算し、この演算結果に応じた第4のパルス信号Zを出力するOR回路1dと、第4のパルス信号Zに応じて、ハイサイドドライブ信号SHおよびローサイドドライブ信号SLを出力する論理回路1eと、を備える。

(もっと読む)

電力変換装置のゲートパルス誤配線検出方法

【課題】作業者のアームの誤解による電圧検出配線とスイッチング配線の誤配線を検出できる電力変換装置のゲートパルス誤配線検出方法を提供することにある。

【解決手段】複数の半導体素子で形成され、一方端を三相交流電源に接続され、他方端を直流端子として直流端子間に直流コンデンサを接続し、制御装置から半導体素子にゲートパルスを与える配線を備え、一方端の線間または星状にコンデンサを接続し、低減電圧を所定時間印加して直流コンデンサを充電した後、制御装置から半導体素子に所定の複数パターンでゲートパルスを与えてこのときの三相交流の各相電流を検知し、複数パターンでのゲートパルスを与えた半導体素子とこのときの三相交流の各相電流の関係を記憶し、制御装置から半導体素子にゲートパルスを与える配線が健全であるときの記憶された関係と、同じ手順により今回記憶された関係とからゲートパルスを与える配線の誤配線を検知する。

(もっと読む)

電力変換装置

【課題】 安定した高い信頼性のゲート駆動回路を有する電力変換装置を提供することを達成する。

【解決手段】 半導体スイッチング素子10によって構成される電力変換装置において、半導体スイッチング素子10の各々の制御電極を制御する制御回路が、半導体スイッチング素子10の主電極間に印加される電圧に比例する第一の電圧信号を生成する電圧検出手段21と、第一の電圧信号の低域信号を取り出して第二の電圧信号を生成する低域通過フィルタ22と、第一の電圧信号と前記第二の電圧信号との差分を第三の電圧信号として得る減算手段23と、第三の電圧信号に応じて半導体スイッチング素子10の制御電極に印加する電圧を調整することで、安定した高い信頼性のゲート駆動回路を有する電力変換装置を提供する。

(もっと読む)

電源装置

【課題】回路が複雑でなく、スイッチング素子の保護機能を向上することができる電源装置を提供する。

【解決手段】電源装置10は、一端が電源端子に接続され、他端が出力端子に接続された主スイッチング素子15と、カソード端子が主スイッチング素子の他端に接続され、アノード端子が接地された整流素子と、主スイッチング素子を制御する制御信号を電圧レベル変換して出力するレベルシフト回路と、ドライバ回路と、レベルシフト回路とドライバ回路に電源供給するブートストラップ回路と、電源からの電圧を所定の電圧に変換してブートストラップ回路に電源供給するレギュレータとを備えた電源装置であって、主スイッチング素子をオンする制御信号が入力されている期間中は、レギュレータからブートストラップ回路への電源供給を遮断するレギュレータ電源供給遮断手段23を設けた。

(もっと読む)

半導体電力変換装置の冷却装置

【課題】半導体電力変換装置内に設けられた半導体スイッチを冷却するヒートシンクと半導体電力変換装置内の空気との温度差により発生するヒートシンク表面の結露を防止する。

【解決手段】半導体スイッチを冷却するヒートシンク周囲に設けられたヒートシンク周囲の空気の温度を検出するヒートシンク周囲温度検出器と、ヒートシンク表面温度を検出するヒートシンク表面温度検出器により検出されたそれぞれの温度から、ヒートシンク表面温度とヒートシンク周囲温度との差を所定の値となるようにヒートシンクへ供給される冷却液の量を可変することで、ヒートシンク表面に発生する結露を防止する。

(もっと読む)

保護回路

【課題】

本発明は、FET1の劣化ないし破壊を防止するための保護回路を提供することを目的とする。

【解決手段】

主スイッチ2をONすると+電源3および−電源4に電圧が供給されコンデンサC3およびC4により+電源と−電源は徐々に立ち上がる。この時電子スイッチ21はOFFに設定されている。−電源4が規定値まで立ち上がると電子スイッチ21はONとなりFET1のドレインに+電源3が印加される。主スイッチ2をOFFとすると+電源3と−電源4はコンデンサC3およびC4により徐々に電圧は下がり始める。−電源が下がり始めると電子スイッチ21はOFFとなりFET1のドレイン電圧7はOFFとなる。

(もっと読む)

レベルシフト回路及びスイッチング電源装置

【課題】dv/dt印加時に誤動作を防止し且つローサイド側からハイサイド側へ信号を伝達し低電圧でも広い範囲で動作するレベルシフト回路。

【解決手段】dv/dt過渡信号が印加され且つ入力信号が入力されないとき第1抵抗R1を含むセット側負荷抵抗R1,R9,MP1のオン抵抗及び第2抵抗R2を含むリセット側負荷抵抗R2,R10,MP2のオン抵抗を第1抵抗及び第2抵抗よりも小さくし、トランジスタMN3がオンである場合にセット信号を生成し且つセット側負荷抵抗をリセット側負荷抵抗よりも大きくし、トランジスタMN4がオンである場合にリセット信号を生成し且つリセット側負荷抵抗をセット側負荷抵抗よりも大きくする制御部MN1,MN2,MP1,MP2,R1,R2,R9,R10、セット信号とリセット信号とに基づいて入力信号をレベルシフトした出力信号を出力するフリップフロップ12を備える。

(もっと読む)

レベルシフト回路及びスイッチング電源装置

【課題】dv/dt印加時に誤動作を防止し且つローサイド側からハイサイド側へ信号を伝達し低電圧でも広い範囲で動作するレベルシフト回路。

【解決手段】トランジスタMN3とトランジスタMN4とをオン/オフさせるパルス発生回路10、第1抵抗R1の両端に第3抵抗R9と非線形特性を有し且つ一定以上のdv/dt過渡信号が印加された場合にオンするダイオードD3〜D6とが接続された直列回路、第2抵抗R2の両端に第3抵抗と同じ抵抗値を有する第4抵抗R10とダイオードとが接続された直列回路、MN3がオンである場合にセット信号、MN4がオンである場合にリセット信号を生成し、MN3のドレインにおける電位とMN4のドレインにおける電位との間において電圧差が生じていない場合にはいずれの信号も生成しない制御部、セット信号とリセット信号とに基づいて入力信号をレベルシフトした出力信号を出力するフリップフロップ12を備える。

(もっと読む)

81 - 100 / 444

[ Back to top ]