Fターム[5H740AA04]の内容

Fターム[5H740AA04]に分類される特許

101 - 120 / 444

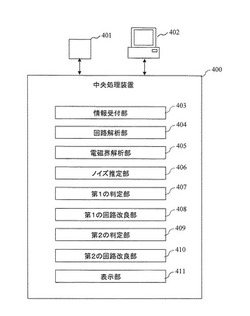

ゲート駆動回路の設計支援装置および設計支援方法

【課題】ゲート駆動回路の設計を、短TAT化する設計支援装置を提供する。

【解決手段】半導体素子のスイッチングを制御するゲート駆動回路に含まれる回路素子のパラメーを用いて前記半導体素子のスイッチング電圧を計算する回路解析部と、前記スイッチング電圧によって前記ゲート駆動回路を搭載するシステムに発生する電磁放射ノイズを計算する電磁界解析部と、前記電磁放射ノイズが目標値に収まっているか否か判定する第1の判定部と、前記電磁放射ノイズが目標値に収まっていない場合に、前記電磁放射ノイズを抑制するように前記回路素子のパラメータを改良する第1の回路改良部と、前記改良したパラメータを用いて前記回路解析部が計算したスイッチング電圧に基づいて電磁放射ノイズを推定するノイズ推定部と、を備え、中央処理装置が、前記回路素子のパラメータを最適化する。

(もっと読む)

駆動装置

【課題】駆動回路やトランジスタにおいてばらつきがあっても、PWM駆動信号の駆動デューティ成分が小さい場合にも、上側トランジスタと下側トランジスタのシュート・スルー(貫通状態)を防止する。

【解決手段】入力端子の第2レベルまたは第1レベル信号に応じてスイッチングデバイスの制御端子に駆動電流をシンク出力するシンク回路と、スイッチングデバイスのオフ期間中に制御端子を経て容量性の電流をシンクする電流シンクトランジスタと、入力端子の信号に応じてソース回路の入力駆動信号と、シンク回路あるいは前記シンクトランジスタへの入力駆動信号とを生成するI/F回路と、シンク回路または前記シンクトランジスタへの入力駆動信号をシンク回路かあるいはシンクトランジスタのどちらに入力駆動信号として出力するかを選択するセレクタと、この選択動作を制御するセレクタへの選択信号を受ける入力端子とを備える。

(もっと読む)

パワー半導体の温度を決定するための方法

【課題】パワー半導体の温度を決定するための方法を提供する。

【解決手段】パワー半導体12の温度を決定するための方法において、第1の制御コンタクト22aが、パワー半導体12に集積された直列抵抗器14の第1の極に接続され、直列抵抗器14の、パワー半導体12へ延びている第2の極が、第2の制御コンタクト22bに接続され、第1の制御コンタクト22aおよび第2の制御コンタクト22bが、それぞれのボンディングワイヤ16を介して、第1の接続端子24aおよび第2の接続端子24bに接続され、直列抵抗器14の抵抗値RVが、2つの接続端子24a、b間の電気測定によって決定され、直列抵抗器14の抵抗値RVおよび温度−抵抗特性曲線に基づいて、直列抵抗器14の温度が、パワー半導体12の温度として決定される。

(もっと読む)

電力変換装置のゲート制御回路

【課題】直列接続されたスイッチング素子の直流短絡事故などを防止するとともに、ゲートパルス信号用のライトガイドの本数を削減する。

【解決手段】直列接続されたスイッチング素子を駆動するゲート駆動回路と、このゲート駆動回路に与える基準信号を発生し、インターロック手段を備えたゲート信号発生手段と、このゲート信号発生手段から光伝送された信号を受光してゲート駆動回路に分配する光分配回路と、この光分配回路の出力をゲート駆動回路に夫々供給する手段と、ゲート駆動回路の出力を監視し、光分配回路にフィードバックするゲート信号監視手段と、ゲート信号監視手段のフィードバック信号が全てオフ状態であればオフ、1つでもオンであればオンとみなす論理演算手段と、論理演算手段の出力を光変換してゲート信号発生手段に供給する伝送手段とで構成する。この伝送手段の出力を、インターロック手段のインターロック条件に反映させる。

(もっと読む)

スイッチングゲートドライバ

【課題】スイッチングゲートドライバにおいて、スイッチング時間を短くして、スイッチング損失を低減すること。

【解決手段】本発明は、IGBT素子のスイッチングゲートドライバであって、IGBT素子のゲート電流を制御するための抵抗部、及び、前記IGBT素子のコレクタ−エミッタ間の電圧に応じて、前記抵抗部の可変抵抗を制御するための制御信号を前記抵抗部に出力する電圧検針部を含むスイッチングゲートドライバを提供する。

(もっと読む)

電力変換装置

【課題】冗長システムの中で待機系を構成する場合であっても光発光素子の寿命を短縮させない監視回路を有する電力変換装置を提供する。

【解決手段】電力変換器1を構成するパワーデバイス11と、第1の光絶縁回路を介して第1の電気信号に変換してパワーデバイス11にオンオフ信号を与えるゲート回路2と、パワーデバイス11のGE間電圧からパワーデバイスの健全性を監視する監視回路3とで構成する。監視回路3は、装置の運転モードが運転系であるときは、GE間電圧を光信号に変換し、第2の光絶縁回路を介して電気信号に変換して異常検出回路41に与えるようにし、運転モードが待機系であるときは、GE間電圧をパルス信号に変換し、これを光信号に変換して第2の光絶縁回路を介して第2の電気信号に変換し、その出力を復元手段40によって復元した後異常検出回路41に与えてパワーデバイス11の健全性を監視する。

(もっと読む)

電力変換装置

【課題】冷媒に含まれる気泡が冷却ケース内に溜まりにくい電力変換装置を提供する。

【解決手段】

底壁20と、該底壁20の周縁部から上方に立設した側壁21と、該側壁21の上端に取り付けられた金属製の上壁板22とを有する冷却ケース2を備える。側壁21には、冷媒導入管4および冷媒導出管5が設けられている。上壁板22に、半導体モジュール3が配置されている。冷媒導入管4から冷媒10をケース内空間Sに導入し、冷媒導出管5から冷媒10を導出することにより、上壁板22に配置された半導体モジュール3を冷却している。冷媒導出管5の、ケース内空間Sに開口した端部である導出側開口端部50は、その上端縁51が、上壁板22の下面220よりも上方に位置している。

(もっと読む)

シリーズレギュレータ

【課題】直列に接続した複数のトランジスタの耐圧を確実に分散できるシリーズレギュレータを提供することを課題とする。

【解決手段】複数の出力制御用トランジスタ5a,5bを直列に接続したシリーズレギュレータ5であって、複数の出力制御用トランジスタ5a,5bの耐圧を分散させるための分圧を設定する複数の分圧素子5e,5gと、複数の出力制御用トランジスタ5a,5bにそれぞれ設けられ、出力制御用トランジスタ5a,5bのゲート電圧を制御する分圧制御用トランジスタ5j,5kを備えることを特徴とする。

(もっと読む)

インバータ装置およびそれをファンモータの駆動装置に用いた電気掃除機

【課題】安価な構成で高効率、信頼性の高いインバータ装置を実現すること。

【解決手段】インバータ装置は、複数の上下アームから構成されるスイッチング回路とスイッチング回路を駆動する制御手段とを備え、上アーム側スイッチング回路を構成するスイッチング素子が電圧駆動型素子であり、下アーム側スイッチング回路を構成するスイッチング素子が電流駆動型素子であり、上アーム側スイッチング回路に素子を駆動する電源電圧を印加するブートストラップ回路を有することにより、低損失、高速のスイッチング素子での回路コストを低減すると共に、スイッチング素子の駆動制御を最適に行うことにより、インバータ回路損失を低減し効率向上を行うことを目的としている。

(もっと読む)

半導体電力変換装置

【課題】スイッチング素子のオンオフ切り替え時において、スイッチング素子のゲートに供給されるゲート電圧の変化を監視し、最適なタイミングで段階的にゲート電圧を切り替えることによって、スイッチング素子のオンオフ切り替え時における電圧・電流サージを発生させない半導体電力変換装置を提供する。

【解決手段】本発明の半導体電力変換装置は、スイッチング素子をオンオフさせる半導体電力変換装置であって、スイッチング素子に供給されるゲート電圧の変化を検出するゲート電圧変化検出手段と、入力される駆動信号に基づいて、スイッチング素子のゲートにゲート駆動電圧を出力するゲート駆動手段とを備え、ゲート駆動手段は、ゲート電圧変化検出手段によってゲート電圧の変化が検出されたタイミングで、ゲート駆動電圧を制御することを特徴とする。

(もっと読む)

画像形成装置

【課題】商用電源に周期的なノイズが入る場合でもゼロクロス点を正確に取得し、正確な定着温度制御を行うこと。

【解決手段】CPU3は、ハードウェアゼロクロス信号取得部7がハードウェアゼロクロス信号4を取得してから(S303 Y)所定時間以内に(S306)、ゼロクロス信号生成回路2が出力したゼロクロス信号の信号レベルとRAM9に保持された信号レベルとが一致するか否かの判断を行う(S312)。

(もっと読む)

電力変換装置

【課題】温度センサを取り付ける作業を容易に行うことができ、冷媒の測定温度が、特定の半導体モジュールの影響を受けにくい電力変換装置を提供する。

【解決手段】複数個の半導体モジュール20と冷却チューブ21とを積層した積層体2を備える。積層体2の積層方向Xにおける一方の端部に位置する冷却チューブ21aに、一対のパイプ3a,3bが接続されている。積層体2とパイプ3とは、収納ケース4に収納されている。また、固定部材5によって、一対のパイプ3が各々収納ケース4に固定されている。パイプ3には、冷媒を導入するための導入側パイプ3aと、冷媒が導出される導出用パイプ3bとがある。導入側パイプ3aを固定する固定部材5aと、導出側パイプ3bを固定する固定部材5bとのうち、少なくとも一方の固定部材5に、冷媒の温度を検出する温度センサ6が取り付けられている。

(もっと読む)

半導体装置

【課題】スイッチング素子による高温の悪影響を回避して、誤点弧を防止する回路をスイッチング素子と同一の基板上に配置した半導体装置を提供する。

【解決手段】基板5上の導電体パターン51,52上にNチャネル型のMOSFET10、及びNチャネル型で半導体材料が炭化珪素からなるJFET30を各別に近接して配置し、MOSFET10のゲート電極13とJFET30のドレイン電極31とをリード線61で接続する。MOSFET10をオン/オフに制御する外部からの駆動信号がJFET30のソース電極32及びドレイン電極31間を伝播するときに、ソース電極32及びゲート電極33間のゲート電圧の低/高に応じてJFET30のチャネル抵抗を大/小に変更することにより、MOSFET10のドレイン電極11及びソース電極12間のスイッチング波形の前縁を、後縁に比較して緩やかな傾斜にする。

(もっと読む)

電圧駆動型半導体素子のゲート駆動回路及び電力変換装置

【課題】高速なスイッチング動作が可能となりスイッチング損失の低減と誤点弧を防止することができるゲート駆動回路および電力変換装置を提供すること。

【解決手段】本発明のゲート駆動回路および電力変換装置は2つのトランジスタで構成されるプッシュプル回路を出力段に備えるゲート駆動回路と、プッシュプル回路(10)と直列に接続されるダイオード(5)を備え、プッシュプル回路とダイオードの直列回路と並列にゲート電源(1)が接続され、プッシュプル回路と並列に負電圧発生回路(6)を備え、負電圧発生回路の出力端子とゲート電源の負極端子間にトランジスタ(4)を接続し、プッシュプル回路とトランジスタのベース端子でプッシュプル回路の出力電圧を正負に出力することを特徴としたゲート駆動回路であり、このゲート駆動回路を使うことで達成できる。

(もっと読む)

スイッチング素子の駆動回路

【課題】ブリッジ回路を構成する高速スイッチング素子を駆動対象とする場合でも、セルフターンオンの発生を防止できる駆動回路を提供する。

【解決手段】SJ−MOSFETであるNチャネルMOSFET3H,3LによりHブリッジ回路1を構成する場合に、駆動回路21を、NチャネルMOSFET3のソースとゲートとの間に磁気結合構造22を設け、NチャネルMOSFET3Hがターンオンした際に、オフ状態に維持されるNチャネルMOSFET3Lの寄生ダイオード5Lに短絡電流が瞬間的に流れると、NチャネルMOSFET3Lのソースに発生する電圧変動に基づいてゲートに誘導される電圧変動を打ち消すため、磁気結合構造22Lを、PNPトランジスタ8LのコレクタとNチャネルMOSFET3のゲートとの間を接続する駆動側配線24Lを、NチャネルMOSFET3Lのソース配線23Lに対して同相で磁気結合させて構成する。

(もっと読む)

ゲート駆動回路

【課題】MOS−FETを確実にオフさせることができ、かつ、複雑な構成を追加することのない、ゲート駆動回路を提供する。

【解決手段】パワーMOS−FETを駆動するためのゲート駆動回路において、前記MOS−FETのゲート端子に第1の抵抗を介してオンさせるための電圧を印加する第1のスイッチング素子と、前記MOS−FETのゲート端子に第2の抵抗を介してオフさせるための電圧に接続させる第2のスイッチング素子とを備え、前記第1の抵抗の抵抗値は前記第2の抵抗の抵抗値よりも大きく設定されているものである。

(もっと読む)

半導体装置

【課題】従来の半導体装置は、出力電流の制限値のばらつきが大きくなる問題があった。

【解決手段】本発明の半導体装置は、電源端子と出力端子との間に接続される出力トランジスタ11と、出力トランジスタ11に流れる電流に比例した検出電流I12を生成する検出トランジスタ12と、検出電流I12に基づき検出電圧を生成する検出電圧生成部R10と、検出電圧に応じて出力トランジスタ11の制御端子から出力端子OUTに電流を引き抜く保護トランジスタ13と、保護トランジスタ13に電流が流れる状態において出力トランジスタ11に流れる電流を設定する制限設定電流I15を保護トランジスタ13の閾値電圧のばらつき及び検出電流I12に対する検出電圧のばらつきに応じて変換した制限電流I18を生成し、制限電流I18を保護トランジスタ13の第1の端子に供給する制限電流生成回路14と、を有する。

(もっと読む)

半導体装置

【課題】電流駆動型の半導体装置のゲートへの寄生インダクタンスによる外乱ノイズを低減し、ゲート駆動を高精度化及び安定化させる。

【解決手段】半導体装置100であって、電流駆動型の半導体素子3と、半導体素子3を制御するゲート駆動回路11と、接続端子部とを備え、半導体素子3は、窒化物半導体層の積層体の上に形成されたゲート電極パッド1と、オーミック電極パッド2及び5とを有し、接続端子部は、オーミック電極パッド2と接続されたオーミック電極端子6と、オーミック電極パッド5と接続されたオーミック電極端子10と、オーミック電極パッド2と接続されたゲート駆動用端子7と、ゲート電極パッド1と接続されたゲート端子8とを有し、ゲート駆動回路11の入力端子はゲート駆動用端子7に接続され、ゲート駆動回路11の出力端子はゲート端子8に接続され、ゲート駆動回路11の基準電位をオーミック電極パッド2の電位とする。

(もっと読む)

電源供給装置

【課題】トランジスタ素子のソース電極とドレイン電極との間の電圧変化がトランジスタ素子のオープン故障又は過電流のどちらによるものなのかを正確に判定すること。

【解決手段】制御回路50は、抵抗素子Rを流れる電流値を検出し、過電流検出回路40によって検出された電圧値が所定値以上である場合、電流値が第1判定値以上であるか否かを判別し、電流値が第1判定値以上である場合、トランジスタ素子Tのオープン故障が発生したと判定し、電流値が第1判定値未満である場合には、過電流が発生したと判定する。

(もっと読む)

スイッチング装置

【課題】簡素な構成で、サージ電圧を抑えつつ、リカバリー電流に伴う損失を抑えることができるスイッチング装置を提供する。

【解決手段】モータ制御装置を構成するインバータ回路は、平滑コンデンサと、FETと、スナバ回路とを備えている。スナバ回路は、コンデンサによって構成されている。スナバ回路102を構成するコンデンサ102aの一方の接続点a1から平滑コンデンサ100を経てコンデンサ102aの他方の接続点a2に至る経路r1のインダクタンスLr1が、直列接続されたFET101a、101d、及び、コンデンサ102aによって形成される経路r2のインダクタンスLr2の10倍となるような位置に、コンデンサ102aが接続されている。これにより、従来のように、リカバリー電流を抑える回路を別途設ける必要がなく、簡素な構成で、サージ電圧を抑えつつ、リカバリー電流に伴う損失を抑えることができる。

(もっと読む)

101 - 120 / 444

[ Back to top ]