Fターム[5H740AA04]の内容

Fターム[5H740AA04]に分類される特許

161 - 180 / 444

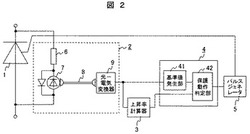

サイリスタ電力変換器の保護装置および方法

【課題】過大な順方向電圧上昇率のサージ電圧の印加による破損からサイリスタを保護する。

【解決手段】サイリスタと並列に電圧検出器を接続しサイリスタのアノード−カソード間電圧を測定する。印加電圧から電圧上昇率計算器で順方向電圧上昇率を求める。印加電圧と順方向電圧上昇率から保護動作判定器にて、印加電圧毎に規定された順方向電圧上昇率以上となった場合を判定したとき、パルスジェネレータから、保護ゲートトリガを当該サイリスタおよび当該サイリスタと直列接続された全サイリスタに出力することで、過大な順方向電圧上昇率からサイリスタを保護する。印加電圧ごとで順方向電圧上昇率の判定を行うことで、順方向電圧上昇率を1つで判定する場合と比較して、不要な保護動作回数を減らせる。

(もっと読む)

ドライブ回路

【課題】連続通弧により半導体スイッチが故障に至るような誤動作を回避するドライブ回路を提供する。

【解決手段】外部から入力された駆動信号に基づいて半導体スイッチ20を駆動させるドライブ回路10bであって、駆動信号に基づいて半導体スイッチ20の駆動制御を行うゲートドライバ16と、ゲートドライバ16による制御の状態にかかわらず、駆動信号の立ち上がりのタイミングに基づいて半導体スイッチ20のスイッチング周期の終了時までの所定期間に強制的に半導体スイッチ20をオフさせる強制オフ回路18とを備える。

(もっと読む)

電子スイッチ制御システム及び電子スイッチ駆動方法

本発明は、電子スイッチに電気的に接続される制御回路に基づいて、様々なタイプの負荷を駆動することができ、広く使用される電子スイッチに関する。制御回路は、本スイッチの少なくとも導通の時点で、制御回路に電力を供給するように設計された電圧レギュレータブロックに接続される。従って、少なくとも一つの交流電圧源(4)と、少なくとも一つの電子スイッチ(1)と、少なくとも一つの負荷(5)と、少なくとも一つの制御回路(3)とを備え、交流電圧源(4)は、第1の電力端子(20)を介して電子スイッチ(1)の第1の導通端子(25)と電気的に接続され、電子スイッチ(1)の第2の導通端子(35)は、第1の負荷端子(40)を介して負荷(5)と接続され、負荷(5)は、第2の負荷端子(80)を介して第2の電力端子(30)と接続され、制御回路(3)は、第1の電位端子(101)、第2の電位端子(102)及び第3の電位端子(103)を備え、制御回路(3)は、トリガー端子(100)を介して電子スイッチ(1)に命令を出すように配置され、制御回路(3)は、電圧レギュレータブロック(200)と電気的に接続され、電圧レギュレータブロック(200)は、第1の電気接続端子(104)及び第3の電気接続端子(106)と、第1の導通端子(25)及び第2の導通端子(35)とをそれぞれ介して電子スイッチ(1)と電気的に接続され、電圧レギュレータブロック(200)は、電子スイッチ(1)の少なくとも導通の時点で制御回路(3)を稼動するように、最小電圧(Vmin)を供給するように配置される、電子スイッチ制御システム(10)が記載される。 (もっと読む)

半導体装置、その駆動方法、及び駆動装置

【課題】共通のP型半導体基板上にNチャンネルDMOSFETを含む複数の素子を形成した半導体装置において、NチャンネルDMOSFETのソース端子が負電圧にバイアスされると、寄生NPNトランジスタにより誤動作を発生する問題があった。

【解決手段】本発明による半導体装置40は、P型半導体基板21と、P型半導体基板21上に形成された複数のn型ウェル22〜24と、複数のn型ウェル22〜24のすくなくとも1つのn型ウェル22上に形成されたNチャンネルDMOSFET31と、を備え、P型半導体基板21の電位がNチャンネルDMOSFET31が形成されたn型ウェル22の電位以下になるように負電位−Egeにバイアスされるように構成されたことを特徴とする。

(もっと読む)

ブートコンデンサの充電方法

【課題】直流電圧の低下を抑えつつ、各相のブートコンデンサの駆動電圧のバラツキを低減させるように充電することが可能なブートコンデンサの充電方法を提供する。

【解決手段】インバータにおいて、U相、V相、W相の各ブートコンデンサを電源回路30によって充電するブートコンデンサの充電方法であって、以下の3つのステップを備えている。第1ステップでは、トランジスタ41及びトランジスタ42が、前置充電期間において、トランジスタ42をオフ状態に維持して、トランジスタ41を介して電源回路30によってブートコンデンサ32等を充電する。前置充電期間とは、通常のスイッチングを行う通常動作期間よりも前の期間のことをいう。また、第2ステップでは、U相、V相、W相の各相のブートコンデンサそれぞれに対して、第1ステップによって行う充電を1〜20パルスずつ割り当てて行う。そして、第3ステップでは、第2ステップを繰り返す。

(もっと読む)

ドライバ装置

【課題】UVLO機能を内蔵したドライバ装置を提供する。

【解決手段】電源に接続された第1のスイッチ素子と、前記第1のスイッチ素子と直列接続された第2と、第3と、前記第3のスイッチ素子と並列接続された第4のスイッチ素子と、一端が前記第3及び第4のスイッチ素子に接続され、他端が前記第1のスイッチ素子の制御電極に接続された第1の抵抗と、前記第1の抵抗を介して前記第3のスイッチ素子の負荷となるカレントミラーと、前記カレントミラーに電流を流す放電回路と、外部から入力信号を受けて、前記第2と第3のスイッチ素子を介して前記第1のスイッチ素子と、を交互にオン、オフするように制御し、かつ、前記放電回路及び前記第4のスイッチ素子を、前記電源が立ち上がるときにオンさせて前記カレントミラーに電流を流すことにより、電源が立ち上がった後は前記第4のスイッチ素子をオフする制御回路を備える。

(もっと読む)

スイッチング素子の誤動作防止回路

【課題】 寄生発振を防止できて誤動作を防止でき、簡素な構成で従来の対策技術と併用でき、あるいは単独に適用し得るスイッチング素子の誤動作防止回路を提供すること

【解決手段】 スイッチング素子S1,S2,…はMOSFETとし、それらMOSFETはドレイン,ソースをそれぞれ接続して並列接続とし、ゲートも同様に並列接続するが各自ゲートとゲート集合点gとの間にゲート抵抗Rをそれぞれ直列に設けて接続する。ドレイン集合点dはトランスTの1次側の一端へ接続し、ソース集合点sは接地し、そしてトランスTの1次側の他端は回路電源Vccへ接続させ、ゲート集合点gへゲート制御信号を加えることでMOSFETをオン・オフ動作(並列動作)させる。各ゲートへ連なるゲート集合点gと各ソースへ連なるソース集合点sとの間にコンデンサCを渡して設ける。短い周期の電位変動がゲートへ加わったとき、コンデンサCが吸収する。

(もっと読む)

電力変換装置および電力変換方法

【課題】キャリア周波数の値を離散的に時間変化させる場合、キャリア周波数の高調波のスペクトルに形成される凸凹を低減し、ノイズのピークレベルを十分に低減した電力変換装置を提供する。

【解決手段】 PWMインバータ2により入力電力を三相交流に変換する電力変換装置において、PWMインバータ2を制御する制御装置5は、PWM制御の搬送波の周波数を、離散的かつ周期的に時間変化させるキャリア周波数変化部10と、キャリアをPWM比較部8a,8b,8cへ出力するキャリア出力部11とを備える。キャリア周波数変化部10は、所望の周波数帯域内において、キャリアの各次数の高調波の周波数スペクトルが連続するように、キャリア周波数の可変範囲を決定する。

(もっと読む)

レベルシフト回路、スイッチング素子駆動回路及びインバータ装置

【課題】レベルシフト回路の電圧変動等に起因するコモンモードノイズ発生時でもクランプすることなく、信号を伝達できるレベルシフト回路、スイッチング素子駆動回路及びインバータ装置を提供する。

【解決手段】セットパルス及びリセットパルスを発生するパルス発生回路と、セットパルスを電流に変換する第1スイッチング素子及びリセットパルスを電流に変換する第2スイッチング素子と、浮動電位側にあり、第1スイッチング素子で電流に変換された信号を電圧に変換するセット用負荷及び第2スイッチング素子で電流に変換された信号を電圧に変換するリセット用負荷と、セット用負荷の信号レベルおよびリセット用負荷の信号レベルから、制御パルス信号を再生するパルス再生回路を備えるレベルシフト回路において、セット用負荷及びリセット用負荷として非線形の負荷特性を有する回路を用いる。

(もっと読む)

半導体装置

【課題】還流ダイオードの導通時の損失並びに過渡動作時の損失は抑えつつ、逆回復動作時に生じる電流・電圧の振動現象を抑制することが容易に可能な電力用半導体装置を提供する。

【解決手段】ユニポーラ動作をする還流ダイオードと、キャパシタと抵抗との直列接続からなり、還流ダイオードに並列接続された半導体回路とを備え、半導体回路200は、抵抗220の少なくとも一部として機能する半導体基体11と、半導体基体の上面に接して設けられた容量低下防止領域1001と、容量低下防止領域1001上に設けられ、キャパシタ210の少なくとも一部として機能するキャパシタ誘電体膜12とを備え、容量低下防止領域1001が、還流ダイオードに逆バイアス電圧が印加された際に半導体基体11中への空乏層の伸張を緩和する。

(もっと読む)

信号伝送回路及び電力変換装置

【課題】磁界変化に伴うノイズの影響を除去し伝送信号の伝送精度を向上させる。

【解決手段】セット用絶縁トランスTL11の1次巻線M11の両端間にPチャネル電界効果型トランジスタTr11を接続し、入力信号S100の立ち上がりに同期したエッジ信号S102の立ち上がりエッジで1次巻線M11に励磁電流を供給し、励磁用のエッジ信号S102の立ち下がりエッジで1次巻線M11に蓄積された励磁電流をトランジスタTr11により強制的に消滅させ、2次巻線M12側から、エッジ信号S102の立ち上がりエッジで負の振幅パルス、立ち下がりエッジで正の振幅パルスが生じるセット用電圧信号S104を得る。この負の振幅パルス及び正の振幅パルスのパルス時間間隔が許容時間範囲内でないときには、ノイズによる振幅パルスであると判断し、許容時間範囲内であるときにのみノイズによる振幅パルスではなく正規の振幅パルスであると判断する。

(もっと読む)

半導体装置

【課題】半導体スイッチ素子に印加される電圧を簡易な構成で精度良く測定することが可能な半導体装置を提供する。

【解決手段】半導体装置101は、第1導通電極と、第2導通電極とを有する半導体スイッチ素子10と、半導体スイッチ素子10の第1導通電極および第2導通電極間の電圧を測定するための電圧測定回路31とを備え、電圧測定回路31は、半導体スイッチ素子10と並列に接続され、半導体スイッチ素子10の導通方向に印加される電圧を所定値に制限する定電圧素子3と、定電圧素子3と並列に接続された制御用スイッチ7と、半導体スイッチ素子10がオフされているときに制御用スイッチ7をオンし、半導体スイッチ素子10がオンされているときに制御用スイッチ7をオフするスイッチ制御部15とを含む。

(もっと読む)

スイッチング回路

【課題】従来の電力用半導体装置では、還流ダイオードが発生する逆回復電流により、回路内で電流、電圧の振動現象が生じるおそれがあったため、電流電圧の振動現象を抑制するスイッチング回路を提供する

【解決手段】ユニポーラダイオード101とバイポーラダイオード102とが同じ方向に並列接続された並列回路と、前記並列回路に接続されたスイッチング素子103とを備える

(もっと読む)

半導体スイッチ回路

【課題】電圧駆動型半導体素子の特性のばらつきによりターンオフ時にコレクタ電圧差が生じる場合であっても、電圧分担をほぼ均一にすることである。

【解決手段】直列接続された3個以上の電圧駆動型半導体素子のコレクタとゲート駆動回路との接続線を互いにコモンモードリアクトルで磁気結合させ、リアクトルの磁気結合巻線にコンデンサ及び抵抗を直列接続して一方が各々の電圧駆動型半導体素子のコレクタに接続され他方が各々のゲート抵抗に接続される電圧均一化回路22を設け、少なくともいずれか一つの電圧均一化回路22のリアクトルを自己以外の二つ以上の他の電圧均一化回路22のリアクトル16と磁気結合させたときは、自己の電圧均一化回路22は、磁気結合した各々のリアクトル16の磁気結合巻線にコンデンサ17をそれぞれ直列接続して並列接続し、その並列接続された磁気結合巻線に一つにまとめた抵抗18を直列接続する。

(もっと読む)

半導体スイッチング素子駆動回路

【課題】トランスの小形化を図ること。

【解決手段】トランス(7)は、一次巻線がコンデンサ(5)を介してパルス電圧源(1)に接続され、二次巻線の一端が逆阻止用ダイオード(9)を介して電圧駆動型半導体スイッチング素子(13)の第1のオン・オフ制御端子に接続されるとともに、二次巻線の他端が電圧駆動型半導体スイッチング素子(13)の第2のオン・オフ制御端子に接続されている。トランス(7)の二次巻線に一定値以上の負電圧が発生した際に、短絡手段(15,17)によって電圧駆動型半導体スイッチング素子(13)の寄生キャパシタンス(13a)が放電される。

(もっと読む)

電力調整器及び電力調整方法

【課題】複数の制御対象に対して、出力ピークの重なりを抑制することのできる電力調整器を得る。

【解決手段】出力信号演算手段102は、一つの制御対象への出力起動信号を任意のゼロクロス点に一致させると共に、別の制御対象への出力停止信号を次のゼロクロス点に一致させる。または、別の制御対象への出力起動信号を任意のゼロクロス点に一致させると共に、一つの制御対象への出力停止信号を次のゼロクロス信号に一致させて出力する。電力制御手段103は、出力信号演算手段102の出力起動信号と出力停止信号とに基づいて、各制御対象400−1〜400−nへの電力を開閉制御する。

(もっと読む)

半導体装置

【課題】本発明はハイサイドスイッチング素子へゲート駆動信号を伝送する高圧側駆動回路から誤出力がされることを弊害なく抑制できる半導体装置を提供することを目的とする。

【解決手段】電源電位とGND電位の間に直列に接続された、高圧側のスイッチング素子であってゲート、エミッタ、コレクタを有するハイサイドスイッチング素子および低圧側のスイッチング素子であるローサイドスイッチング素子と、該ゲートへゲート駆動信号を伝送する高圧側駆動回路と、該高圧側駆動回路に設けられた該高圧側駆動回路の基準電位を与えるVs端子と、一端が該ハイサイドスイッチング素子のエミッタと接続され他端が該Vs端子と接続される抵抗と、アノードが該抵抗の一端と接続されカソードが該抵抗の他端と接続されるダイオードとを備える。

(もっと読む)

電力変換回路の駆動装置及び電力変換システム

【課題】パワースイッチング素子Sw及びその入出力端子に逆並列に接続されたフリーホイールダイオードFDを備える電力変換回路を駆動対象とするものにあって、パワースイッチング素子Swが低温において信頼性が低下しやすいこと。

【解決手段】フリーホイールダイオードFDに電流が流れる場合、コンパレータ82から論理「H」の信号が出力される。この信号は、パワースイッチング素子Swを強制的にオフ状態とする指令信号となる。ただし、感温ダイオード90の温度が低い場合、ヒステリシスコンパレータ94の出力信号が論理「L」となるため、AND回路98を介して駆動IC60に出力される最終的な信号は、論理「L」となり、パワースイッチング素子Swの強制的なオフ操作はなされない。

(もっと読む)

スナバモジュール

【課題】浮遊インダクタンスを最小限に抑制するとともに、半導体スイッチ素子からスナバモジュールへの熱伝導を抑制したスナバモジュールを提供する。

【解決手段】電力変換回路に用いられる半導体スイッチ素子に、取付ネジによって接続されるスナバモジュールにおいて、前記スナバモジュールの端子2は、スナバ回路を収納するための筐体1から突設した突設部4と、前記突設部4の端部から折曲形成され、前記半導体スイッチ素子の主端子に接続される接続部6と、を備える。また、前記突設部4に形成された取付ネジ頭部を挿通するネジ頭部挿通孔7と、前記接続部6に形成された取付ネジ軸部を挿通するネジ軸部挿通孔3とを連通させる。

(もっと読む)

電力変換装置

【課題】

過熱等の異常状態が発生した直後に短絡電流が発生した場合において、短絡保護処理を行う前にスイッチング素子に流れる短絡電流を遮断してしまう事態を防止し、過大なサージ電圧から適切に保護することができる電力変換装置を提供する。

【解決手段】

スイッチング素子Qを駆動する駆動回路11と、スイッチング素子Qに流れる電流を検出する電流検出手段13と、短絡状態を検出したとき、スイッチング素子Qに流れる電流を所定範囲に制限して所定時間駆動を継続する短絡保護手段14と、を備え、スイッチング素子Qを停止すべき異常状態が検出されたときに、駆動回路11がスイッチング素子Qの駆動を停止する電力変換装置1において、異常状態が検出された後であって異常状態に基づく駆動停止が実行される前に短絡状態を検出した場合に、異常状態に基づく駆動停止よりも短絡保護手段14に基づく短絡保護処理を優先して実行する。

(もっと読む)

161 - 180 / 444

[ Back to top ]