Fターム[5H740BA11]の内容

電力変換一般 (12,896) | 主回路スイッチング素子 (1,744) | トランジスタ (1,563)

Fターム[5H740BA11]の下位に属するFターム

電界効果トランジスタ(FET) (722)

マルチエミッタトランジスタ (26)

Fターム[5H740BA11]に分類される特許

761 - 780 / 815

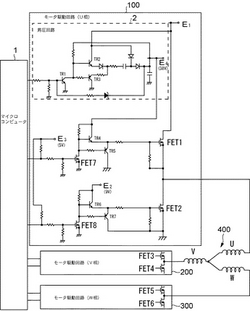

モータ駆動装置

【課題】 適切な昇圧電圧を発生でき、当該昇圧電圧を用いてモータを駆動するモータ駆動装置を提供する。

【解決手段】 昇圧回路2の昇圧端子E4の電圧は、トランジスタTR4を介してFET1のゲート端子に印加されており、当該38Vのゲート電圧が、24V電源E1によるFET1のソース−ドレイン電圧よりも高くなっている。FET1のオン状態に保持するためには、ソース−ドレイン電圧の24Vよりも4V高い28V以上であることが条件となるが、昇圧回路2からの38Vという高電圧をFET1のゲート端子に印加し、24Vという高電圧で三相ブラシレスモータ400を回転させる場合であっても、確実にFET1をオン状態に保持する。

(もっと読む)

半導体冷却装置

【課題】 互いに独立した二つの電力変換回路を構成する第1及び第2の半導体素子群が取り付けられる第1及び第2の素子取付面を有する受熱ブロックと、この受熱ブロックに接続された放熱部とを備えた半導体冷却装置において、一方の電力変換回路を構成する半導体素子が物理的に破損した場合に、破損した半導体素子の残骸が他方の電力変換回路を構成する半導体素子に接触して他方の電力変換回路に悪影響を及ぼすことがある。

【解決手段】 板状に形成された一つの受熱ブロック12の一方の面に、第1の半導体素子群G1の半導体素子1が取り付けられる第1の素子面12aと、第2の半導体素子群G2の半導体素子1が取り付けられる第2の素子取付面12bとを設ける。

(もっと読む)

パワー半導体スイッチを駆動するための集積回路装置

【課題】 単独パワー半導体スイッチ又はハーフブリッジ回路内のパワー半導体スイッチを駆動するための集積回路装置を紹介する。

【解決手段】 スイッチ(40)用の少なくとも1つの第1レベルシフタ(730)を少なくとも含んでいる複数の機能グループを有する第1駆動チップ(72)と、第2レベルシフタ(740)とスイッチ(40)のドライバ(746)とを少なくとも含んでいる複数の機能グループを有する少なくとも1つの第2駆動チップ(74)とから回路装置が構成されていて、少なくとも1つの第2駆動チップが第1駆動チップに後続接続されていて、第2駆動チップの基準電位が、第1駆動チップのレベルシフタの出力電位上に位置し、それらの駆動チップが互いに適切な絶縁状態をもって共通のハウジング(70)内に配設されていること。

(もっと読む)

容量結合による高電圧レベルのシフト

【課題】簡単な回路構成で、高電圧のレベルシフトを行う。

【解決手段】アース電圧(アース1)を基準とする入力回路(10)と、コンデンサ(C1またはC2)を介して入力回路に結合された別のアース電圧(アース2)を基準とする出力回路(12)とを備える回路構造である。

(もっと読む)

電圧駆動型半導体素子の故障検出回路

【課題】アーム当り複数個直列接続される半導体素子のスイッチングタイミングや特性のばらつき等がある場合でも、小形かつ簡単な回路で素子電圧をバランスさせつつ、素子故障の検出ができるようにする。

【解決手段】1アームあたり複数個直列接続される電圧駆動型半導体素子Q1〜Qnの各ゲート線を、ゲートタイミングバランス用磁気コアTg1〜Tg(n-1)により磁気結合させて電圧バランスを図るとともに、いずれか1つの磁気コアの端子電圧、ここでは磁気コアTg(n-1)の電圧VT2から素子異常を検出可能とし、回路の簡単化,小型化を図る。

(もっと読む)

ゲート駆動回路への信号伝送方式

【課題】電力変換器の各アーム毎に複数個直列接続される半導体スイッチング素子にオン,オフ信号を供給する場合に、各ゲート駆動回路を互いに縦続接続して伝送により順次供給する構成とすることで、絶縁トランスの容量を小さくし得るようにする。

【解決手段】電力変換器の各アーム毎に、例えばIGBT1〜4を複数個直列接続し、低圧側のゲート駆動回路24から高圧側ゲート駆動回路21まで、絶縁トランス14〜11を介し制御装置10から順々にオン,オフ信号を伝送する構成とすることにより、高圧側の絶縁トランス11の一次巻線と二次巻線間に印加される電圧を従来方式のものよりも低減させ、絶縁トランスの小容量化を図る。

(もっと読む)

電源装置

【課題】並列補償器の補償量を一定にする制御量を与えることで、運転条件によらず安定した電流リプル低減ができる電源装置を得る。

【解決手段】前記交直変換器3の直流出力に含まれる電流リプルを低減する受動フィルタ5と、受動フィルタ5の出力電流の電流リプルをさらに低減するインピーダンス素子及びスイッチ素子を含む並列補償器6と、並列補償器6のスイッチ素子に印加される直流電圧の指令値に対して、並列補償器6に印加される直流電圧及び前記並列補償器の補償電流の大きさが大きいときはゲインを小さくし、並列補償器6に印加される直流電圧及び前記並列補償器の補償電流の大きさが小さいときはゲインを大きくする制御器を備えた電源装置。

(もっと読む)

電源リップルフィルタ回路

【課題】スリープ状態からアクティブ状態になった時の電源リップルフィルタ回路の出力電圧の収束性の向上を提供する。

【解決手段】抵抗2と、容量3で構成されたCR積分回路4と、NPN型トランジスタ1と、前記NPNトランジスタ1のコレクタ−ベース間電流Ic電流12から前記NPNトランジスタ1のベース電流Ib電流10を検出するベース電流検出ディスチャージ回路6と、外部からの制御信号であるコントロール電圧Ec9をトリガとし、一定時間だけ前記ベース電流検出回路を動作可能に制御するタイマー回路7を備えている。

(もっと読む)

多直列接続された自己消弧型素子のゲート制御方法及びこれを用いた電力変換装置

【課題】 多直列接続された自己消弧型素子に過大な電流が流れた際に、通常のゲート駆動電源以外の電源を使用せず、過電流及び過電圧保護を簡単に且つ確実に行うことのできるゲート制御方法及びこれを用いた電力変換装置を提供する。

【解決手段】 多直列接続された自己消弧型素子11a乃至14cと、この自己消弧型素子夫々の主電極間の電圧を検出する電圧検出手段2と、この自己消弧型素子夫々のゲート端子に任意の電圧を印加するゲート制御部3と、夫々の自己消弧型素子11a乃至14cに過大な電流が流れたことを検出する過電流検出手段34とを備え、前記ゲート制御部3は、前記過電流検出手段34が過電流を検出したとき、オン動作中の前記自己消弧型素子のゲート電圧を低減させるとともに、前記電圧検出手段2の検出値が前記自己消弧型素子の耐電圧以下の所定値以上になったとき、前記自己消弧型素子のゲート電圧を上昇させるようにする。

(もっと読む)

ピーク電圧保護回路および方法

関連する高電圧NPNトランジスタ(T3)を破壊に対して保護するためのピーク電圧保護回路であり、この保護回路は、関連する高電圧NPNトランジスタ(T3)のベース−コレクタ電圧に関係づけられたセンサ電圧を感知するための低電圧NPN素子(T15)を含む。この回路はさらに、関連する高電圧NPNトランジスタ(T3)のベース−コレクタ電圧をトリガと同時に制限するための起動回路を含む。低電圧NPN素子(15)は、低電圧NPNトランジスタ(T15)の降伏電圧をセンサ電圧が超えると同時に起動回路をトリガするように起動回路に結合される。  (もっと読む)

(もっと読む)

半導体装置

【課題】 半導体パワー素子のみならずそれに逆並列接続されたフリーホイールダイオードの過熱判定も行えるようにする。

【解決手段】 IGBT11と、このIGBT11に逆並列接続されたフリーホイールダイオード21とからなるパワー部と、IGBT11の温度を検出する第1のダイオード12と、フリーホイールダイオード21の温度を検出する第2のダイオード22とを備え、第1、第2のダイオード12、22は、並列接続され、それによる検出温度電圧Vtempが温度検出回路40に入力されるようになっており、この温度検出回路40にて、検出温度電圧Vtempに基づき過熱判定を行う。

(もっと読む)

光結合パワー半導体素子

【課題】小型、軽量、高速かつ低損失のパワー半導体素子回路を構成するのに適した光結合パワー半導体素子を提供すること。

【解決手段】本発明の光結合パワー半導体素子は、実質的に同じバンドギャップを有するワイドギャップ半導体材料からなるp型層34とn型層33,35とが少なくとも三層交互に、複数層積層されたバイポーラ型のパワー半導体素子と、受光素子とを含む。パワー半導体素子は、複数層33,34,35のうち中間に挟まれた層34に通電電流を制御する制御端子16Aを備える。複数層33,34,35のうち少なくとも一層、例えば層34に、通電電流に応じて光を発生する再結合センターが含まれ、この再結合センターで発生した光が外部へ放射されるようになっている。受光素子は、その光を受けて、パワー半導体素子の通電電流に応じた出力を発生する。

(もっと読む)

プログラム可能なデッドタイム挿入機能を有するゲートドライバ

【課題】集積回路に組み込む新規なデッドタイム生成器であって、集積回路が、ハイサイドゲートドライバとローサイドゲートドライバとを含むものを提供すること。

【解決手段】本デッドタイム生成器は、ハイサイドゲートドライバとローサイドゲートドライバが、出力スイッチのオン時間の間にデッドタイムが生じるように出力スイッチを駆動する。また、デッドタイム設定要素が接続されている外部のデッドタイム設定端子を有する回路を集積回路の内部に備えている。更に、デッドタイム生成器は、デッドタイム設定端子におけるある範囲のデッドタイム設定値に対する段階的なデッドタイムを提供する回路を備えている。デッドタイム生成器は、デッドタイム設定端子における複数の範囲のデッドタイム設定値に対する、対応する複数の段階的なデッドタイムを生じさせる。

(もっと読む)

ゲート駆動装置への電力供給方式

【課題】電力変換器の各アーム毎に複数個直列接続される半導体スイッチング素子対応の各ゲート駆動装置に電力を供給する場合に、絶縁トランスの容量を大きくすることなく絶縁を確保できるようにする。

【解決手段】電力変換器の各アーム毎にIGBT等の半導体スイッチング素子1〜5を複数個直列接続し、低圧側のゲート駆動装置25から高圧側ゲート駆動装置21まで、絶縁トランス15〜11を介して順々に電力を分岐して伝達供給する構成とすることにより、高圧側の絶縁トランス11の一次巻線と二次巻線間に印加される電圧を従来方式のものよりも低減させ、絶縁トランスの小容量化を図る。

(もっと読む)

素子の駆動装置と制御方法

【課題】 素子の駆動電力の低減,駆動装置の重量および容積の小型化を可能にする素子の駆動装置および方法を提供する.

【解決手段】 電源B1は電力の供給と充電ができる電源で,電源B1に接続されるスイッチQ1,Q2によってスイッチQ1が導通でスイッチQ2が遮断の状態1と,スイッチQ1が遮断でスイッチQ2が導通の状態2の2種類の状態をもち,被駆動素子のゲート容量に充電されている電荷を放電をする過渡において,状態2としてゲート容量に充電されている電荷をインダクタンス素子L1を介し放電するとともにインダクタンス素子L1にエネルギーを蓄える状態を経て,状態1としてインダクタンス素子L1に蓄えられたエネルギーによりIGBT1のゲート容量に充電された電荷を放電するとともに電源B1に電流を回生し充電する.

(もっと読む)

ゲート駆動装置

【課題】 電力変換装置または電力変換装置の負荷側で、短絡事故などが発生したとき、これを検知して、IGBTに過大な電流が流れるのを阻止してIGBTの破壊を防止する。

【解決手段】 パルス発生回路6からパルスが出力されているにもかかわらず、IGBT3に印加されている電圧が低下しないとき、短絡検出回路9によって、これを検知させて、ゲート電圧クランプ回路10にIGBT3のゲート電圧をクランプさせ、また各IGBTの飽和電流特性のバラツキなどに起因して、IGBT3の飽和電流値が小さくなって、IGBT3の分担電圧が増大したとき、過電圧検出回路8によって、これを検知させて、ゲート電圧クランプ回路10にIGBT3のゲート電圧を増加させる。

(もっと読む)

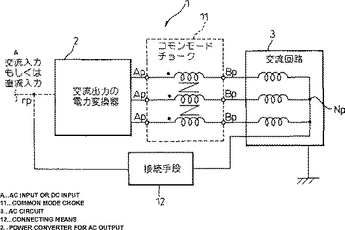

フィルタ装置

交流出力の電力変換器に接続される交流回路に発生する電磁障害を抑制するフィルタ装置である。このフィルタ装置は、電力変換器の入力側、出力側あるいは直流側のいずれかの端子と交流回路の入力端子との間に接続されるコモンモードチョークと、交流回路の中性点からの引出し線を、このコモンモードチョークに対してさらに上位側にある電位変動の少ない基準電位点に接続する接続手段と、を備える。  (もっと読む)

(もっと読む)

半導体電力変換装置

【課題】本発明はスナバ回路を必要とせずに、スイッチング動作時のピーク電圧の抑制を行う半導体電力変換装置を提供する。

【解決手段】ゲートに順バイアスと逆バイアスを印加し半導体素子のエミッタを中点電位とする電圧印加手段と、コレクタとエミッタ間の電圧を分圧する分圧手段とを備え、駆動信号がオフの場合にゲートに分圧手段により分圧された電圧が印加し、コレクタとエミッタ間電圧が分圧手段により定まる電圧以上となった場合に、コレクタとエミッタ間電圧に応じてゲート電圧を制御するようにする。

【効果】本発明によればスナバ回路を省略することによりスナバ損失がなくなり、電力変換装置の小形化,高効率化および低コスト化を達成できる。

(もっと読む)

電力用半導体装置の制御用回路および制御用集積回路

【課題】製造コストを低減できる電力用半導体装置の制御用回路および制御用集積回路を提供する。

【解決手段】シャント抵抗50において生じるシャント電圧は、過電流検出手段22に入力される。過電流検出手段22は、過電流を検出した場合には、電流異常を示す電流異常信号をリセット信号出力手段24に入力させる。リセット信号出力手段24は、入力される電流異常信号により異常の発生を記憶した後、異常の回復を待つ。そして、入力される電流異常信号により過電流が検出されなくなった場合には、異常が回復したと判断し、動作開始のためのHレベルのパルス信号からなるリセット信号を、リセット端子RESETからフォールト信号出力回路17に入力させる。リセット信号を入力されたフォールト信号出力回路17は、LレベルからHレベルに移行させたHレベルのフォールト信号を下アーム駆動回路14に入力させる。

(もっと読む)

ゲート指令装置、電動機指令機器及びターンオフ指令方法

【課題】 パルス幅変調(Pulse Width Modulation、PWM)インバーターへの使用における部品のターンオフプロセスを改良する。

【解決手段】 本発明は、IGBT型の電力用半導体部品11のゲート指令装置10に関する。ランプ波発生回路20は、基準ゲート電圧を出力で供給する。前記基準電圧の電流増幅段は、IGBT部品のゲート電流を送出し、この増幅段は、トリガー回路30と高速ターンオフ回路40を有する。低速ターンオフ回路50は、IGBT部品のゲートGと発生回路の出力との間に接続される。部品のコレクタ・エミッター間電圧検出回路60は、高速ターンオフ回路40と発生回路の出力22に作用する帰還信号71を供給する帰還回路70に接続されている。

(もっと読む)

761 - 780 / 815

[ Back to top ]