Fターム[5H740BA11]の内容

電力変換一般 (12,896) | 主回路スイッチング素子 (1,744) | トランジスタ (1,563)

Fターム[5H740BA11]の下位に属するFターム

電界効果トランジスタ(FET) (722)

マルチエミッタトランジスタ (26)

Fターム[5H740BA11]に分類される特許

61 - 80 / 815

スイッチング素子の駆動回路

【課題】オフ保持用スイッチング素子46をオフ状態とすべき期間において、この素子が誤ってオフ状態とされることに起因するスイッチング素子S*#の信頼性の低下を抑制することのできるスイッチング素子の駆動回路を提供する。

【解決手段】オフ保持回路48は、信号生成部26の操作信号INを入力としてゲートの充電処理の実行中であると判断された場合、オフ保持用スイッチング素子46をオフし、操作信号INを入力としてゲートの放電処理の実行中であると判断されて且つゲート電圧検出部50の出力信号GPRを入力としてゲート電圧Vgeが低いと判断された場合、オフ保持用スイッチング素子46をオンする。ここで、上記駆動回路は、ゲート電圧Vgeが閾値電圧を跨いでから出力信号GPRの論理が反転するまでの時間を、操作信号INを入力としてオフ保持回路48によって把握される充電処理指示時間の最小値以下とするように構成される。

(もっと読む)

半導体集積回路

【課題】絶縁ゲート型半導体素子を駆動する半導体集積回路内において、貫通電流の発生を抑制することが可能な技術を提供することを目的とする。

【解決手段】半導体集積回路は、制御信号Vinを遅延させて得られる遅延信号を、PMOS1及びNMOS2のゲート端子に出力する遅延回路19を備える。NMOS4が、第2出力信号の変化に応じてオンからオフに切り替えられるタイミング(t2)は、PMOS1が、遅延信号の変化に応じてオフからオンに切り替えられるタイミング(t2)よりも遅くなく、かつ、PMOS3が、第1出力信号の変化に応じてオンからオフに切り替えられるタイミング(t7)は、NMOS2が、遅延信号の変化に応じてオフからオンに切り替えられるタイミング(t7)よりも遅くない。

(もっと読む)

コンバータモジュールにおけるスイッチング損失の低減

【課題】スイッチング損失を低減した、DC入力電圧をDC出力電圧またはAC出力電圧に変換するコンバータを提供する。

【解決手段】コンバータは、入力端子101と出力端子103に電圧を供給するスイッチング素子104を備え、スイッチング素子104をオフしたとき、寄生インダクタンスLparasiticによって誘導されるエネルギをキャパシタC110に一時的に蓄えるために、ダイオードD110およびキャパシタC110の第1の直列回路110が設けられている。ダイオードD110は一方の入力端子101に結合され、並列に結合されている能動回路120によって、第1の直列回路110のキャパシタC110に一時的に蓄えられているエネルギを解放制御する。

(もっと読む)

半導体装置の短絡保護装置

【課題】半導体素子、特にIGBTの特性の違いや温度変化があっても、最適なパラメータを自動的に設定することのできる半導体装置の短絡保護装置を提供する。

【解決手段】IGBTのゲート電荷QGに対応する電圧VQGを検出する電荷検出手段22と、IGBTの定格動作時の入力部の電荷から負荷短絡が発生したかどうかを判断するための基準電圧VREFを発生する基準電圧発生手段25と、電荷検出手段22で検出された電圧VQGがIGBTの定格動作時の電荷に対応する電圧か、あるいは負荷短絡時の電荷に対応する電圧かを判断する判断手段27と、判断手段27が短絡状態を検出したときにIGBTを動作停止する信号を出力するゲート駆動手段21とを持つ半導体装置の短絡保護装置において、基準電圧発生手段25に、IGBTの定格動作時の入力部の電荷に対応するゲート電荷電圧VQGのハイレベルで安定した電圧VPEAKを検出して記憶する記憶手段26を設ける。

(もっと読む)

ゲート駆動回路

【課題】絶縁ゲート型半導体スイッチ素子のターンオフ時の遅延時間短縮、遮断電流のdi/dtによるサージ電圧を抑制することができるゲート駆動回路を提供する。

【解決手段】半導体スイッチ素子のゲート端子とゲート補助端子間にオン用ゲート電源とオン用スイッチとオン用ゲート抵抗の直列体よりなるオン回路を接続し、半導体スイッチ素子のゲートとゲート補助端子間に第1のオフ用ゲート抵抗とオフ用スイッチとターンオフ用電源を直列に接続し第1のオフゲート抵抗と並列にコンデンサと第2のオフ用ゲート抵抗の直列体を接続したオフ回路を備えてなる。第1のオフ用ゲート抵抗より第2のオフ用ゲート抵抗の抵抗値が小さく、コンデンサと第2オフ用ゲート抵抗で構成するCR回路の時定数が絶縁ゲート型半導体スイッチ素子のターンオフ遅れ時間と同等である。

(もっと読む)

電力変換装置

【課題】新たな部品を追加することなく、スイッチングサージを抑えることができる電力変換装置を提供する。

【解決手段】モータ制御装置1は、電源配線10と、平滑コンデンサ11と、インバータ回路12と、制御回路13とを備えている。平滑コンデンサ11は、コンデンサ110、111を並列接続用配線112、113によって並列接続して構成されている。並列接続用配線113のインダクタンスLs1及びコンデンサ110、111がループ状に接続され、LC共振回路が構成される。LC共振回路の共振周波数が、サージ電圧に含まれる周波数成分のうち、抑制しようとする所定周波数になるようにインダクタンスLs1、コンデンサ110、111の容量の少なくともいずれかが調整されている。これにより、新たな部品を追加することなく、スイッチングサージを抑えることができる電力変換装置を提供する。

(もっと読む)

負荷駆動装置

【課題】複数の駆動回路とスイッチング素子との接続点を通じて、内部回路や基準点に電流が回り込むことを防止する。

【解決手段】電流の回り込みが発生し得る回り込み防止対象となる内部回路16、26とスイッチング素子であるIGBT1との間に回り込み防止回路15、25を配置する。そして、駆動回路10、20のうち作動させられない側の回り込み防止回路15、25をオフすることで、回り込み防止対象となる内部回路16、26にスイッチング素子となるIGBT1のゲート電圧が印加されないようにする。これにより、各内部回路16、26内で電流の回り込みが発生することを防止することが可能となる。

(もっと読む)

半導体装置と、それを用いたインバータ、コンバータおよび電力変換装置

【課題】ターンオン時間のばらつきが小さな半導体装置を提供する。

【解決手段】この半導体装置は、ノードN1,N2間に直列接続された高耐圧、高GmのトランジスタQ1および低耐圧、低GmのトランジスタQ2と、トランジスタQ2に並列接続された低耐圧、高GmのトランジスタQ3とを含む。トランジスタQ2をオンさせるとトランジスタQ1がオンし、さらにトランジスタQ3をオンさせるとノードN1,N2間が導通状態になる。したがって、低耐圧のトランジスタQ2をオンさせて高耐圧のトランジスタQ1をオンさせるので、ターンオン時間のばらつきが小さくなる。

(もっと読む)

スイッチング装置、スイッチングモジュール

【課題】本発明は、サージ電圧の低減及び発生ノイズの低減を可能とするスイッチング装置、スイッチングモジュールを提供することを目的とする。

【解決手段】本発明にかかるスイッチング装置は、スイッチング素子1と、エミッタ電極100と、エミッタ電極100を外部の主配線に接続するための主配線用エミッタ端子4と、エミッタ電極100と主配線用エミッタ端子4との間の主電流経路に介在する、複数の制御用エミッタ端子5、制御用エミッタ端子6、制御用エミッタ端子7と、隣接する制御用エミッタ端子間の主電流経路に介挿されたインダクタンス8、インダクタンス9とを備えることを特徴とする。

(もっと読む)

半導体スイッチング素子駆動装置

【課題】半導体スイッチング素子の温度変化によるサージ電圧の発生および変動を抑制すると共にスイッチング損失を低下させることができる半導体スイッチング素子駆動装置を提供する。

【解決手段】各切替スイッチ42a、42bが駆動信号に従ってオン/オフすることにより、駆動手段40が半導体スイッチング素子10の制御端子11に駆動電流を供給する。一方、温度検出手段20によって半導体スイッチング素子10の素子温度または半導体スイッチング素子10の動作環境温度を検出する。そして、駆動手段40は、温度検出手段20によって検出された素子温度または動作環境温度に従って制御端子11に印加する駆動電流の大きさを変更する。これにより、半導体スイッチング素子10の温度変化によるサージ電圧の発生および変動が抑制され、スイッチング損失が低下する。

(もっと読む)

交流電圧の位相角を調整する調整回路

【課題】 広範囲の応用が可能な交流電圧の位相角を調整する調整回路を提供する。

【解決手段】 交流限流回路装置Z10は、負荷L101及び双極性固体スイッチ素子1000を直列接続するとともに交流電源に並列に接続する。双極性固体スイッチ素子1000は、双極性の駆動電圧信号を出力する双方向サイリスタ素子、及び双極性の駆動電圧信号を出力する電界効果パワーデバイスによって構成される。調整回路PD100は、交流電源電圧を入力するとともに回路調整機能と交流限流回路装置Z10を流れる電流値と負荷L101の端電圧値とに基づいて双極性の駆動電圧信号を出力し、双極性固体スイッチ素子1000のオン位相角及びオフ位相角を制御する。これにより、抵抗、交流電気エネルギーが印加される抵抗を含む誘導性負荷、容量性負荷、または直列に接続されている抵抗を含む誘導性負荷及び容量性負荷を制御することができる。

(もっと読む)

鉄道車両用ゲートドライブ回路

【課題】 ゲートドライブ回路のゲート指令部とゲート電源部内の高圧側と低圧側の絶縁を可能とし、さらにゲートドライブ回路の小型化を図ることができる鉄道車両用ゲートドライブ回路を提供することを目的とする。

【解決手段】 実施形態の鉄道車両用ゲートドライブ回路は、架線と接続されるトランス103と、トランス103の架線側に接続され、鉄道車両の電力変換器のスイッチング素子を駆動する2つのスイッチ102a、102bと、トランスの架線とは反対側で接続する整流回路104を介してゲート電源を供給し、トランスの架線とは反対側で接続する信号検出回路106を介してゲート指令を出力する鉄道車両用ゲートドライブ回路を有している。

(もっと読む)

太陽光発電用電力変換装置

【課題】従来の電力変換装置では、ゲート抵抗切り替え回路部に速い応答性が要求されるため、ノイズにより誤動作し易く、場合によっては、誤動作により装置の保護機能が働き、動作停止してしまうことがあった。

【解決手段】太陽電池1の直流電圧を交流電圧に変換し、交流の系統電源に電力を供給する電力変換装置2であって、電力変換装置2は、複数のパワー半導体スイッチSH、SLと、これらのパワー半導体スイッチSH、SLをオン/オフ動作させるゲート駆動回路GH、GLと、これらのゲート駆動回路に挿入されたゲート抵抗RG1、RG2と、ゲート駆動回路GH、GLにオン/オフ信号を供給すると共に、ゲート抵抗値を変更する制御信号を出力する制御回路22とを備え、制御回路22は、予め設定された時刻にゲート抵抗値変更信号を出力するようにした。

(もっと読む)

半導体スイッチング素子駆動装置

【課題】サージの発生を抑制すると共に半導体スイッチング素子のスイッチング速度を向上しつつ、回路規模を小さくすることができる半導体スイッチング素子駆動装置を提供する。

【解決手段】時間設定手段40から短絡検出区間が終了したことを示す時間設定信号を入力すると、この時間設定信号の入力をトリガとして駆動手段60に対して半導体スイッチング素子10の制御端子11に印加する駆動電流を増加するための電流制御信号を出力する。これにより、サージの発生が予想されるミラー区間後に行われる短絡状態の検出が終了した後は制御端子11に印加される駆動電流iが増加するため、サージの発生を抑制しつつ、スイッチング速度が向上する。また、時間設定信号を利用して制御端子11に流す駆動電流iの電流量を制御しているため、制御端子11の電圧を検出するための構成が不要となり、回路規模が小さくなる。

(もっと読む)

半導体スイッチ回路の電圧バランス回路

【課題】スイッチング過渡時のスイッチング損失と偏りを低減でき、オン・オフ定常時の電圧アンバランス抑制を容易にし、電圧バランス制御の応答性に優れ、多数のスイッチング素子の直列接続回路に対応できる。

【解決手段】抵抗分圧回路RD1、RD2は、各スイッチング素子S1、S2のエミッタ−コレクタ間に、それぞれ同等抵抗値で同等分圧比の分圧抵抗を並列接続し、スイッチング素子の直列接続点を中点Nとしてスイッチング素子のエミッタ−コレクタ間電圧に比例した電圧を負担電圧としてそれぞれ検出する。電圧バランス制御回路(VD1,VD2,DAMP,VAC)は、各検出電圧の電圧偏差がゼロ(零)になるよう、スレーブ側のスイッチング素子S1のゲート電流を補正して各スイッチング素子の負担電圧をバランスさせる。

(もっと読む)

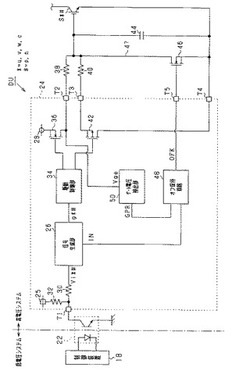

スイッチング素子の駆動回路

【課題】スイッチング素子S*#の駆動異常の有無を適切に判断することのできるスイッチング素子の駆動回路を提供すること。

【解決手段】スイッチング素子S*#のゲートの充電経路を流通する電流を一定値に制御する定電流制御を行う。そして、定電流制御の開始が指示されてから充電経路における電流の流通が開始されるまでの時間が規定時間を上回ると判断された場合、スイッチング素子S*#の駆動異常が生じている旨判断する。また、定電流制御によって充電経路を電流が流通する時間が下限時間未満になると判断されたり、上記流通する時間が上限時間を上回ると判断されたりした場合、スイッチング素子S*#の駆動異常が生じている旨判断する。

(もっと読む)

スイッチング素子の駆動回路

【課題】一対のスイッチング素子S*#a,S*#bを同一の駆動信号によって駆動する場合、駆動に異常が生じることでそれらの温度同士の乖離が大きくなるものの、これを迅速に検出する手段がないこと。

【解決手段】スイッチング素子S*#a,S*#bの温度を検出する感温ダイオードSDa,SDbの出力電圧は、端子T6a,T6bに印加される。端子T6a,T6bの電位差は、差動増幅回路50を介してウィンドウコンパレータ52に取り込まれる。ウィンドウコンパレータ52では、これらの差が大きい場合に、異常が生じている旨判断する。

(もっと読む)

ゲート回路

【課題】本発明は、パワー素子の過電流を速やかに抑制しつつ、di/dtを小さくしてパワー素子をオフすることができるゲート回路を提供することを目的とする。

【解決手段】本発明に係るゲート回路は、パワー素子の過電流発生と同時にパワー素子のゲート電圧の一部を抵抗素子に負担させる過電流抑制手段を有する。さらに、パワー素子の過電流を抑制した後は、抵抗値の高い抵抗素子を用いてパワー素子をゆっくりオフするオフ動作遅延手段を有する。

(もっと読む)

ゲート駆動回路、およびパワー半導体モジュール

【課題】 スイッチング素子を誤動作させずに高速低損失動作が可能なゲート駆動回路を部品点数の少ない簡易な回路構成で実現する。

【解決手段】 トランス15の1次側をローサイドゲート駆動回路2の出力端子に接続し、トランス15の2次側をハイサイドスイッチング素子5のゲート入力側に接続する。ローサイド駆動回路2から正極性のゲート駆動電圧が出力されるとハイサイドスイッチング素子5のゲート‐ソース間には負極性の電圧が印加されてゲート電圧は閾値以下に抑えられるため、ローサイドスイッチング素子がターンオンする際にハイサイドスイッチング素子はオフ状態を維持する。

(もっと読む)

パワーモジュール

【課題】センス電流を抵抗で検出する場合であっても、カレントミラー回路を用いて検出する場合であっても、誤検出や電流検出精度の低下を起こさないパワーモジュールを提供する。

【解決手段】IGBT1の電流センス素子STのセンスエミッタにエミッタが接続されたトランジスタQ5と、トランジスタQ5のコレクタに一方端が接続され、他方端が共通接続部BPに接続された電流検出抵抗SRとを有し、トランジスタQ5のベースがGNDに接続された電流検出回路C3と、電流検出抵抗SRによって発生する共通接続部BPを基準とした電位差を電流検出電圧Vsとして検出し、所定の閾値電圧との比較を行い、両者の大小関係によってIGBT1に過電流が流れているか否かを判定する。

(もっと読む)

61 - 80 / 815

[ Back to top ]