Fターム[5H740BA12]の内容

電力変換一般 (12,896) | 主回路スイッチング素子 (1,744) | トランジスタ (1,563) | 電界効果トランジスタ(FET) (722)

Fターム[5H740BA12]に分類される特許

221 - 240 / 722

パワートランジスタを制御する装置

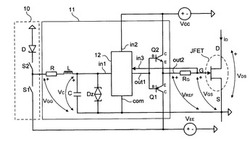

【課題】トランジスタがスイッチ・オンされた時、スイッチング・ロスと、電磁干渉(電磁妨害)と、を削減するのに最適化された動作特性を有する、JFETタイプのトランジスタの制御装置を提案する。

【解決手段】本発明は、ゲート、ドレイン及びソースを備えるJFETタイプのトランジスタのゲート制御装置に関し、前記装置は、前記トランジスタの前記ゲート(G)に接続された出力(out2)を備える電圧生成回路11を備え、前記回路は、前記出力にて、所定の電圧ランプに追随する、基準ゲート・ソース電圧(VREF)を生成するように設計され、前記基準ゲート・ソース電圧(VREF)を所定の最大値(VGS_max)に、前記JFETトランジスタの端子におけるゲート・ソース電圧(VGS)が前記最大値に到達した時、制限するように設計された、電圧制限回路12を備える。

(もっと読む)

スイッチング素子制御装置およびモータ駆動装置

【課題】1個のスイッチング素子を制御して負荷に電流を供給する場合でも、スイッチングノイズおよびスイッチング損失を低減する。

【解決手段】スイッチング素子制御装置(1)は、第1の信号を受けて、低電圧でスイッチング素子(SW1)をオン制御する第1の制御回路(11)と、スイッチング素子(SW1)が低電圧でオン制御されてから第2の信号を出力するオンタイミング制御回路(12)と、第2の信号を受けて、低電圧よりも高い電圧でスイッチング素子(SW1)を引き続きオン制御する第2の制御回路(13)と、を備えている。

(もっと読む)

電源回路、及び電子機器

【課題】FET内で発生するオン抵抗の上昇を抑制することで、使用するFETの耐性を下げ、以ってコストを低減する

【解決手段】FETをオン・オフするためのゲート電圧を所定タイミングで供給するゲートドライブ回路と、第一入力ラインと前記ゲートドライブ回路との間に介在して、第一入力ラインに供給されるゲートドライブ電圧の電圧値が一定の値になった場合に第一入力ラインとゲートドライブ回路とを導通させる第一のスイッチ回路と、スタート信号が前記FETのスイッチング動作をオフにすることを示すローレベルに変化した場合に、この信号変化に応じて第一入力ラインからゲートドライブ回路へのゲートドライブ電圧の供給を遮断する第二のスイッチ回路と、を有する。

(もっと読む)

電力変換装置

【課題】逆回復電流に起因するスイッチング損失ならびに発熱損失を減少することができる電力変換装置を提供する。

【解決手段】電力変換装置において、ノーマリーオン型スイッチング素子4とノーマリーオフ型スイッチング素子5とを、電気的に直列接続し、カスコード接続用ダイオード7を介して、ノーマリーオン型スイッチング素子4のゲート端子とノーマリーオフ型スイッチング素子5のソース端子を接続したカスコード素子21と、このカスコード素子21と電気的に並列接続され、正極端子にカソード領域が接続され、負極端子にアノード領域が接続された高速ダイオード6とを備える。

(もっと読む)

半導体スイッチング素子のドライブ回路

【課題】パルス信号を停止した場合に半導体スイッチング素子のオン期間の増大を防止できる半導体スイッチング素子のドライブ回路。

【解決手段】ドライブ回路は、直列に接続された第1半導体スイッチング素子Q1と第2半導体スイッチング素子Q2とを交互にオン動作させ、第1,第2半導体スイッチング素子の制御信号となるパルス信号を生成するパルス信号発生回路2の両端に接続され、コンデンサCとトランスT1の一次巻線Pとの直列回路と、一次巻線とは逆方向に巻回され、発生した電圧を第1半導体スイッチング素子の制御端子に印加するトランスの第1の二次巻線S1と、一次巻線と同方向に巻回され、発生した電圧を第2半導体スイッチング素子の制御端子に印加するトランスの第2の二次巻線S2と、パルス信号が停止されたときにオンすることにより第1半導体スイッチング素子のオン期間を短くさせるスイッチング素子Q3とを備える。

(もっと読む)

逆耐圧を有するIGBTの過電流保護回路

【課題】逆耐圧を有するIGBTの短絡保護回路として、ゲート駆動回路とIGBTのコレクタとの間にダイオードを接続して、過電流時コレクタ電圧が上昇した時、ゲート遮断する方式では、駆動回路に逆電圧がかかり破壊される。

【解決手段】ゲート駆動回路とIGBTのコレクタとの間にダイオードと抵抗の直列回路を接続し、さらにゲート信号遮断用トランジスタのエミッタと制御端子に接続した定電圧ダイオードのカソードとの間にダイオードを設ける。

(もっと読む)

電源装置

【課題】 電源装置に内蔵されているインバータ回路の導通時間が最少近傍のとき、出力電流の制御が不安定になる。

【解決手段】 商用交流電源を整流・平滑して直流電圧を出力する直流変換回路と、直流電圧を高周波交流電圧に変換するインバータ回路と、高周波交流電圧を負荷に適した電圧に変換する変圧器と、インバータ回路を制御する出力制御信号を出力する出力制御回路と、出力制御信号に応じてインバータ回路を駆動するスイッチング素子駆動回路と、を備えた電源装置において、スイッチング素子駆動回路は、出力制御信号のオンデューチイが予め定めた基準値未満のとき予め定めた第1の駆動電圧を供給し、出力制御信号のオンデューチイが前記基準値を超えたときから第1の駆動電圧を高くし予め定めた第2の駆動電圧として供給し、インバータ回路を駆動すること、を特徴とする電源装置である。

(もっと読む)

高周波交流電源装置

【課題】ゲート用電源の構成を改善し、インバータ等を構成する複数の半導体スイッチのスイッチング周波数とスイッチング電圧を向上できる高周波交流電源装置を提供する。

【解決手段】多出力ゲート用電源7は、各ゲートドライブ回路19に相互に、絶縁された電圧源を供給する複数のトランス15と、これらのトランスに駆動電力を供給するトランスドライブ回路14を含み、トランスは、閉じた磁路を形成するトランスコア18と、このトランスコアに巻回された2次巻線17と、トランスコアの中空部を貫通する1次巻線16とで構成され、2次巻線は各ゲートドライブ回路に接続され、複数のトランスの1次巻線は直列に接続され、直列1次巻線16と2次巻線17が空間距離を設けて配置され、かつ、直列1次巻線16がプリント基板28に配置されている。

(もっと読む)

三相交流電動機の制御装置

【課題】基板上におけるデッドスペースを有効に利用して基板面積を低減することができる三相交流電動機の制御装置を提供する。

【解決手段】電力供給回路80は、一次回路81と、一次回路81に第一上段トランスT1を介して結合されるとともに第一上段駆動回路21に接続される上段二次回路82と、上段二次回路82に第二上段トランスT2を介して結合されるとともに第二上段駆動回路22に接続される上段三次回路83とを有し、一次回路領域7と、第一上段回路領域61と、第二上段回路領域62とを備え、第一上段トランスT1は、一次回路領域7と第一上段回路領域61との間に形成された絶縁領域を架け越して配置されるととともに、第二上段トランスT2は、第一上段回路領域61と第二上段回路領域62との間に形成された絶縁領域を架け越して配置されている。

(もっと読む)

インバータ駆動用電源回路

【課題】一次巻線の故障が発生した場合であっても、二次巻線の出力電圧の低下を抑制し、正常なインバータの動作を行うことが可能なインバータ駆動用電源回路を実現する。

【解決手段】プッシュプル方式に対応したN個(Nは2以上の整数)のトランスT1〜T6を備え、N個の一次巻線T11〜T61の第一巻線T1A〜T6A同士が第一電源制御部5により制御される一次側電源4に並列接続されると共に、第二巻線T1B〜T6B同士が第二電源制御部6により制御される一次側電源4に並列接続され、各トランスT1〜T6のコアの飽和磁束密度が、N個のトランスT1〜T6を構成する回路内に欠損箇所がない正常状態で一次巻線T11〜T61に流れる電流の最大値によっても磁気飽和を起こさないために最低限必要とされる必要飽和磁束密度に対して{1+1/(N−1)}倍以上に設定されている。

(もっと読む)

スイッチ素子の制御手段

【課題】スイッチ素子のスイッチングを高速化できるスイッチ素子の制御手段について、小型化および高効率化すること。

【解決手段】スイッチ素子Qを制御するスイッチ素子制御回路1は、トランスTおよびツェナーダイオードDを備える。ツェナーダイオードDのアノードには、トランスTの2次巻線T2の一端が接続され、ツェナーダイオードDのカソードには、スイッチ素子Qのゲートが接続される。スイッチ素子Qは、ゲート−ソース間に入力容量Cissを内蔵する。

(もっと読む)

スイッチング装置及びその制御方法

【課題】負荷を安定に制御できるスイッチング装置を提供する。

【解決手段】スイッチング素子(2)と、前記スイッチング素子をPWM制御する制御回路(8)と、を有し、前記スイッチング素子のスイッチング動作により入力電力を負荷に供給するスイッチング装置であって、

前記制御回路が、前記PWM制御のデューティ比率の保持とリセットとを周期的に繰り返し、前記スイッチング装置が異常状態になる直前と異常状態から正常状態に復帰した直後とにおいて、同一のデューティ比率でスイッチング素子をPWM制御することを特徴とするスイッチング装置。

(もっと読む)

電力変換装置

【課題】電力損失が小さな電力変換装置を提供する。

【解決手段】この電力変換装置では、マイクロコンピュータ20は、NチャネルMOSトランジスタ42,43の飽和電圧がIGBT6,9の飽和電圧よりも低くなる低電流域では、NチャネルMOSトランジスタ42,43およびIGBT7,10をオン/オフ制御し、IGBT6,9の飽和電圧がNチャネルMOSトランジスタ42,43の飽和電圧よりも低くなる高電流域では、IGBT6,7,9,10をオン/オフ制御する。したがって、トランジスタの直流損失を低減できる。

(もっと読む)

ノーマリオントランジスタを有する整流器を使用する電力変換器

【課題】電力変換器の始動時または電力変換器の故障時にノーマリオン型トランジスタを使用する整流器が変換器の入力およびバスキャパシタを短絡させることができない。

【解決手段】直列に接続される2つのトランジスタ(T1,T2)が設けられる少なくとも1つのスイッチレッグを備える整流器を備えた電力変換器に関する。トランジスタは、ノーマリオン電界効果型、例えばJFETであり、それぞれがゲート制御装置(CT1,CT2)によって制御される。各ゲート制御装置は、特に、制御トランジスタのゲートGに接続される出力と、制御装置の出力と変換器の入力in1との間に接続される電圧整流素子と、トランジスタのソースSと、制御装置の出力と電圧整流素子との間に位置する点との間に接続されるキャパシタC11と、を備える。

(もっと読む)

半導体装置

【課題】新たな部品追加や駆動方式を変更することなく、セルフターンオン現象を防止することができるDC/DCコンバータを提供する。

【解決手段】非絶縁型のDC/DCコンバータにおいて、ローサイドMOSFET3のゲートを駆動するローサイド用のプリドライバ5の基準電位は、ハイサイドMOSFET2とローサイドMOSFET3とを通る主回路以外から印加されていることで、主回路の寄生インダクタンスの合計は大きくすることなく、ローサイドMOSFET3のソースとプリドライバ5の基準電位の間の寄生インダクタンスが大きくなり、部品追加や駆動方式の変更をせずに、ローサイドMOSFET3のゲートの負電位駆動ができ、セルフターンオン現象を防止できる。

(もっと読む)

半導体装置

【課題】ESD耐性に優れ、保護素子の新たな作製を要さない半導体装置を提供する。

【解決手段】この発明にかかる半導体装置は、主電流を制御するゲート端子22に接続されたゲート電極と、主電流を流すドレイン端子21に接続されたドレイン電極と、主電流を流すソース端子23に接続されたソース電極とを有する主MOSFET素子31と、ゲート端子22に接続されたゲート電極と、ドレイン端子21に接続されたドレイン電極と、電流検出用のセンスソース端子24に接続されたソース電極とを有するセンスMOSFET素子32と、ソース端子23に接続されたゲート電極と、ドレイン端子21に接続されたドレイン電極と、センスソース端子24に接続されたソース電極およびボディ電極とを有するESD保護素子A33と、ゲート端子22に接続されたカソード電極と、センスソース端子24に接続されたアノード電極とを有するESD保護素子D41とを備える。

(もっと読む)

非絶縁ゲート半導体デバイスのゲート駆動回路

【課題】広バンドギャップの半導体デバイス及び/または非絶縁入力を有する半導体デバイス向けにカスタマイズした効率がよくかつ費用対効果がよいゲート駆動回路を提供する。

【解決手段】非絶縁入力を有する半導体デバイス(62)をスイッチングするゲート駆動回路(60)は、半導体デバイス(62)の本来性寄生ダイオードを順バイアスするように半導体デバイス(62)のゲート上に電流を印加することによって半導体デバイス(62)をターンオンする第1の回路(64)を有する。半導体デバイス(62)の寄生ダイオードを逆バイアスするように半導体デバイス(62)のゲート上に電流を印加することによって半導体デバイス(62)をターンオフする第2の回路(66)を存在させており該第1の回路(64)及び第2の回路(66)はそれぞれ第1のスイッチ及び第2のスイッチを通して半導体デバイス(62)に結合されている。

(もっと読む)

スイッチング制御回路

【課題】発熱がダイオードに集中することを抑制できるスイッチング制御回路を提供する。

【解決手段】スイッチング素子の順方向導通時に流れる電流の向きと逆方向で、スイッチング素子に並列接続されるダイオードと、スイッチング素子又はダイオードの少なくとも一方の温度を検出する温度検出手段と、温度検出手段の検出温度に応じて、スイッチング素子の逆方向導通時に流れる電流を制御する制御手段を有する。

(もっと読む)

電力変換回路

【課題】電力変換回路において、電圧変化率を抑制できるようにする。

【解決手段】直流電源V0の正・負極側に接続されるスイッチング素子M1,M2と誘導性の負荷LLとの間にそれぞれインダクタL1,L2を設け、これらインダクタL1,L2のスイッチング素子M1,M2の側に、クランプダイオードD0を、スイッチング素子M2からスイッチング素子M1に向かって導通する方向に接続する。クランプダイオードD0は、ターンオフ時にインダクタL1,L2を流れる電流を短絡するので、大きなサージ電圧が発生しなくなる。一方、ターンオン時は、インダクタL1,L2のために、主回路はいわゆる電流共振型ソフトスイッチング方式の回路と同様の動作をするので、ターンオンしつつあるスイッチング素子M1またはM2に流れる電流は、ゆっくり増加するようになり、その結果、電圧変化率は抑制されることになる。

(もっと読む)

パワーエレクトロニクスシステムにおける妨害輻射を低減するための装置

【課題】パワーエレクトロニクスシステムの不要輻射を低減する装置を提供する。

【解決手段】パワー半導体モジュール又は少なくとも1つのパワー半導体モジュールの構成部と、第1形成体を備えている基準電位と、パワー半導体構成素子を外部接続するために付設されている端子要素と接続するため、装置内に配されている異なる極性の少なくとも2つの直流負荷接続要素とを有している。異なる極性の2つの直流負荷接続要素は少なくとも夫々1つの部分を有し、この部分においてこれらの接続要素は平面状に形成され、これらの部分は互いに平行で隣接して延び電気絶縁されている。平面状の第1部分形成体を有する少なくとも1つの第2形成体を有し、この第2形成体は直流負荷接続要素の2つの平行する部分間の範囲でこれらの接続要素から電気絶縁されて配されている。同様に第2部分形成体は第1形成体と導電接続されている。

(もっと読む)

221 - 240 / 722

[ Back to top ]