Fターム[5H740BA12]の内容

電力変換一般 (12,896) | 主回路スイッチング素子 (1,744) | トランジスタ (1,563) | 電界効果トランジスタ(FET) (722)

Fターム[5H740BA12]に分類される特許

281 - 300 / 722

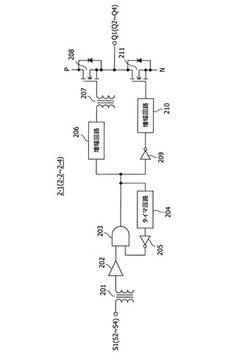

電力変換器のゲート駆動回路

【課題】ゲート信号のオン状態が所定期間以上継続することを防止すること。

【解決手段】電力変換器(3)のスイッチング素子(301〜304)のオン期間を規定するパルス信号(S1〜S4)を絶縁用のトランス(201)に入力し、トランス(201)から出力される信号を用いてスイッチング素子(301〜304)のゲートに与えるゲート信号を形成するゲート駆動回路である。トランス(201)から出力される信号を整形する整形手段(202)と、整形手段(202)によって整形された信号が所定期間オン状態を継続した場合に前記ゲート信号をオフ状態にさせる信号オフ手段(203、204、205)とを備える。

(もっと読む)

半導体装置

【課題】従来の半導体装置は、負荷のインダクタンス成分等による出力トランジスタの電位差変動を制御できないという問題があった。

【解決手段】本発明にかかる半導体装置は、ゲートに印加される制御電圧に応じて負荷への電源供給が制御される出力トランジスタT1と、T1のゲート−ドレイン間に接続され、T1のソース−ドレイン間の電位差に応じて導通状態が制御される電圧制御回路SBと、SBの導通状態に基づいて電圧制御検出信号を出力する電圧制御検出回路SDと、T1のゲートとソースとの間に接続され、電圧制御検出信号に応じてオンオフが制御されるトランジスタT4と、T4に直列に接続され、T1の温度状況に応じてオンオフが制御されるトランジスタT5と、T4及びT5に並列に接続されたトランジスタT3と、を備える。このような回路構成により、T1の電位差変動を制御することが可能である。

(もっと読む)

電力変換装置

【課題】主スイッチ素子に並列に接続されているダイオードまたは主スイッチ素子の寄生ダイオードに還流電流が流れないようにする。

【解決手段】ハイサイド及びローサイドの各主スイッチ素子19、29に並列にMOSFET11、21と可飽和インダクタ12、22からなる直列回路を接続し、MOSFETに並列にコンデンサ16、26を接続し、MOSFET11、21のゲートと可飽和インダクタ12、22のMOSFET11、21が接続されている端子と反対側の端子との間に第2のダイオード13、23を接続し、第2のダイオード13、23に並列に短絡用スイッチ素子14、24を接続し、短絡用スイッチ素子14、24の制御電極をMOSFET11、21と可飽和インダクタ12、22の接続点に接続した。

(もっと読む)

低電圧電力供給

入力DC電圧V+を出力DC電圧レベルに変換するバックレギュレータは、DC電圧レベルを出力する結合インダクタと、出力DC電圧レベルの誤差を感知するオペアンプと、誤差に対応するデューティサイクルを有するパルス波形を提供するパルス幅変調器(PWM)として動作するコンパレータとを含む。パルス波形に応答してV+電圧レベルを出力するV+電圧ドライバと、パルス波形に応答してV+電圧レベルよりも高く、V+電圧レベルを補完するスーパー電圧レベルVssを出力するVss電圧ドライバとを含む。スーパー電圧レベル、及びV+電圧レベルをそれぞれ受信するゲートを有し、結合インダクタを駆動して、DC電圧レベルを出力するデュアルMOSFETを含む。PWMと電圧ドライバとの間に結合されるパルス整形器は、パルス波形より立ち上がり時間が速く、電圧ドライバ駆動用制御信号として提供されるシャープなパルスを形成する。 (もっと読む)

スイッチング回路

【課題】大型化を招くことなく損失を低減できるスイッチング回路を提供する。

【解決手段】主及び従MOSFET1a,3aはソース端子s同士、ゲート端子g同士が接続され、ボディダイオード2aと同極性に外付けダイオード5が接続されるとともに、駆動回路6aにより主及び従MOSFET1a,3aが同時にスイッチング制御される。主ボディダイオード2aに環流する電流は従ボディダイオード4aによって遮断されるので、環流電流及びリカバリ電流はともに外付けダイオード5に流れることになり、全体の損失を低減できる。また、従MOSFET3aには電圧吸収手段が施されているので、外付けダイオード5の導通直後に従MOSFET3aに印加されるサージ電圧を吸収でき、従MOSFET3aのドレイン端子d、ソース端子s間の耐電圧を低くできるので、従MOSFET3aの損失を軽減できる。

(もっと読む)

半導体装置

【課題】半導体集積回路への電源供給がなくても、負荷駆動システムにおける負荷開放状態が検出できる半導体装置を提供する。

【解決手段】半導体装置10は、負荷装置4をスイッチング制御するためのパワー半導体素子1、および負荷装置4の異常を検出する半導体集積回路2を備え、さらにパワー半導体素子1の出力端子電圧を抵抗分圧するプルダウン用の分圧回路20、分圧回路20を構成するプルダウン用抵抗14,15から電源供給を受けて負荷装置4の開放検出を行うMOSFET16、および半導体集積回路2から出力される異常信号によってオン、あるいはオフ動作するMOSFET17が内蔵されている。また、負荷装置4の開放状態の検出結果を外部に出力する状態出力端子18を備えている。

(もっと読む)

負荷駆動装置

【課題】浮遊容量の存在に起因する現象を回避することが可能な負荷駆動装置を提供すること。

【解決手段】電位差検知回路9は、負荷駆動電圧VBPから制御電圧VBBを減じたものを両者の電位差として演算し、その電位差が所定の閾値を超えるとき、Hレベルの信号をスイッチング素子8のゲート端子に出力する。前記所定の閾値は、負荷駆動用電源3が定格出力電圧の最大値(上限値)を出力する場合の負荷駆動電圧VBPの測定値から、制御用電源2が定格出力電圧の最小値(下限値)を出力する場合の制御電圧VBBの測定値を減じたものに設定されている。電位差検知回路9からスイッチング素子8のゲート端子にHレベルの信号が入力されたとき、同スイッチング素子8がON作動し、これによりスイッチング素子4のゲート端子の電位がGNDに近いレベルに固定される。

(もっと読む)

ドライバ回路およびDC−DCコンバータ

【課題】デッドタイムを設けることなく貫通電流を抑制することができるとともに、貫通電流を抑制しつつ高周波化を図ることができるドライバ回路およびDC/DCコンバータを提供する。

【解決手段】電源端子と接地端子との間に直列形態に接続され、デッドタイムのない相補的な一対の制御信号によってオン、オフ駆動される第1のスイッチング素子(SW1)と第2のスイッチング素子(SW2)を備えるドライバ回路において、少なくとも前記第1のスイッチング素子の制御端子に、オン状態での制御電圧を制限するリミッタ回路(LMT1)を接続するようにした。

(もっと読む)

インダクタ駆動回路

【課題】 インダクタに流れる電流の変化を小さくして逆起電圧を抑制しかつ貫通電流を防止することができるインダクタ駆動回路を提供する。

【解決手段】 第1の電源電圧端子と第2の電源電圧端子との間に直列形態に接続された2以上のトランジスタを有するプッシュプル出力段を備え、該出力段のいずれかのトランジスタの制御端子と前段の論理ゲート回路との間に抵抗手段が接続され、出力端子には負荷としてのインダクタの一方の端子が接続されるインダクタ駆動回路において、前記抵抗手段が接続されている前記出力段のトランジスタの制御端子には、該トランジスタと直列形態に接続されている他のトランジスタがオン状態にされた際に当該トランジスタをオフ状態へ移行させるようにその制御端子を低インピーダンス駆動可能にするインピーダンス切替え手段を設けるようにした。

(もっと読む)

スイッチング電源装置及びスイッチング制御システム

【課題】本発明は、複数の出力系統を設けた構成において、ある出力系統が短絡しても、それ以外の出力系統は正常な給電を行うことができる、スイッチング電源装置及びスイッチング制御システムの提供を目的とする。

【解決手段】レギュレータRGの出力電圧をトランスT1(T2)の一次側に接続されたスイッチング素子16(26)のオンオフ駆動により電圧変換して、インバータを構成するスイッチング素子を駆動する駆動回路の電源電圧として該駆動回路毎にそれぞれ供給される複数の直流電圧をトランスT1(T2)の二次側に出力するフォワード型コンバータFC1(FC2)と、トランスT1(T2)の一次側に流れる過電流を遮断する過電流保護素子E1(E2)とを備える、スイッチング電源装置。

(もっと読む)

スイッチング電源装置

【課題】待機時にノイズフィルタ回路で消費される電力を低減することができるスイッチング電源装置を提供する。

【解決手段】スイッチング電源装置1は、交流電源2と、整流平滑回路5と、スイッチング回路6’と、交流電源2と整流平滑回路5の間に選択的に配置される第1のノイズフィルタ回路3’および第1のノイズフィルタ回路3’よりもインピーダンスが大きな第2のノイズフィルタ回路4と、リレー(切り替え手段)11とを備える。第2のノイズフィルタ回路4は第1のノイズフィルタ回路3’よりも抵抗値が大きな放電抵抗を有する。リレー11は、外部信号に基づいて、通常動作時に第1のノイズフィルタ回路3’を介して交流電源2と整流平滑回路5とが接続される第1の接続モードに切り替え、待機時に第2のノイズフィルタ回路4を介して交流電源2と整流平滑回路5とが接続される第2の接続モードに切り替える。

(もっと読む)

地絡保護を備えるハイサイドドライバ

【課題】ハイサイドドライバ用の費用効率の良い保護回路であって、必要コンポーネント数を最小限化し、ソフトウェア介入を必要としない保護回路の提供。

【解決手段】ハイサイドドライバ用保護回路は、第1の入力および第2の入力を受信し、該入力の各々を分析し、該入力の分析に応じて出力を伝送するように構成される排他的ORゲートであって、第1の入力はハイサイドドライバの電力出力を表し、第2の入力は前記ハイサイドドライバの作動のための制御信号を表す、排他的ORゲートと、排他的ORゲートの出力に応答してハイサイドドライバの電気出力を制御するよう構成されるスイッチングデバイスとを含む。

(もっと読む)

ゲート駆動回路およびそれを用いたインバータ回路

【課題】双方向スイッチは、オン抵抗を下げるためにゲートの閾値電圧が低くする必要がある。閾値電圧を下げた場合、外来ノイズやスイッチング時のノイズ等によりゲート電位が振られ、誤動作が発生し、短絡故障などを起こす可能性があるため、そのような場合でも、冗長な動作が得られるよう基準電位を負電圧として電圧偏差を確保するような回路構成とし、誤動作などによる短絡故障を未然に防止することを目的とする。

【解決手段】第一ゲート端子2、第二ゲート端子3を各オンオフすることで4つの動作モードを有する双方向スイッチ1を直列接続したハーフブリッジ回路に適用するゲート駆動回路であり、第一ゲート端子2あるいは第二ゲート端子3のオン電圧とオフ電圧との偏差を確保する最適電圧生成部を備え、ゲート閾値電圧を下げてオン抵抗を下げ、ノイズが重畳した際であっても、不要なターンオンあるいはターンオフを回避することができる。

(もっと読む)

パワースイッチング素子の駆動回路

【課題】電圧制御形のパワースイッチング素子Swの電力損失の抑制とサージの抑制との両立を図ることが困難なこと。

【解決手段】パワースイッチング素子Swのゲートは、充電用抵抗体34、並びに充電用バイポーラトランジスタ32及び充電用MOSトランジスタ40を介して、電源30の正極に接続されている。パワースイッチング素子Swをオン状態へと切り替える際には、まず充電用バイポーラトランジスタ32をオン操作することで、パワースイッチング素子Swのゲートに正の電荷を充電する。そして、パワースイッチング素子Swがオン状態となった後に、充電用MOSトランジスタ40をオン操作する。

(もっと読む)

DC−DCコンバータ

【課題】急激な入力電圧上昇がある場合や高入力電圧が長時間続く場合においても、素子破壊することなく、安定した直流電力供給が可能なDC−DCコンバータを提供する。

【解決手段】主スイッチ素子Q1と整流スイッチ素子Q2を有してなる同期整流型のDC−DCコンバータであって、整流スイッチ素子Q2が、整流トランジスタ素子Tr2と整流ダイオード素子Di2とで構成されてなり、入力電圧Viまたは入力電圧の上昇率dVi/dtを判定して、該判定値が所定の基準値を越えた時、主スイッチ素子Q1と整流トランジスタ素子Tr2の相補的なオン・オフ動作を解除し、デッドタイムTDより長い時間、主スイッチ素子Q1と整流トランジスタ素子Tr2が共にオフとなる状態が設定されてなるDC−DCコンバータとする。

(もっと読む)

DC−DCコンバータ及び電源供給システム

【課題】効率の低下を抑えつつ、輻射ノイズの低下をすることができるDC−DCコンバータ及びシステム電源を提供すること。

【解決手段】第1DC−DCコンバータ20aは、ワンセグ受信機、無線通信機に第4、第5電源電圧を供給する第4、第5DC−DCコンバータが動作する場合、第1DC−DCコンバータ20aは、スイッチング回路38を駆動するドライバ部37の駆動能力を小さくている。また、第1DC−DCコンバータ20aは、この駆動能力を3段階で大きくしている。これにより、第1DC−DCコンバータ20aのスイッチングの立ち上げ時間及び立ち下げ時間を長くする。

(もっと読む)

電力変換装置

【課題】 この発明になる電力変換装置は、電力変換装置を構成する単相インバータやDC−DCコンバータ等のゲート電源を共通化し、ユニット構成を簡略化して安価で性能の良い電力変換装置を提供するものである。

【解決手段】系統に並列もしくは直列に接続された少なくとも2つ以上の単相インバータを備え、各インバータ間を接続する端子と同電位のソース端子を有するスイッチ群を駆動するゲート用の電源を共通化したことを特徴とするものである。

(もっと読む)

スナバ回路

【課題】半導体スイッチの寄生キャパシタンス充電による過電圧等を抑制する。

【解決手段】ダイオードブリッジ5〜8の交流入力の一端と他端との間に、半導体スイッチ素子3,4を逆方向に直列に接続するとともに、素子3,4の両端にスナバダイオード201,202とスナバコンデンサ204との直列回路をそれぞれ接続し、スナバダイオードとスナバコンデンサとの接続点と前記ダイオードブリッジの直流出力の一端との間には抵抗205を接続し、素子どうしの接続点と前記ダイオードブリッジの直流出力の他端との間にはダイオード203を接続することで、素子3,4の電圧がスナバ電圧を超えて上昇することがないようにする。

(もっと読む)

接合型電界効果トランジスタの駆動装置および駆動方法

【課題】簡単な構成によって、一時的な過電流による接合型電界効果トランジスタの発熱を抑制するとともに、接合型電界効果トランジスタの過熱状態を検知することができる接合型電界効果トランジスタの駆動装置および駆動方法を提供する。

【解決手段】電流検知部90でモニタする電流が閾値電流を超えた場合、接合型電界効果トランジスタ(JFET)32をターンオンするときのゲート電圧をPN接合のビルトイン電圧より大きくする。これにより、JFET32のオン抵抗を低減させてJFET32の発熱を抑制する。さらに、オン状態のJFET32に流れるゲート電流IGの温度依存性を利用することによって、JFET32の温度の値を簡単に求めることができる。

(もっと読む)

多相モータ駆動装置

【課題】インバータ回路における下側のスイッチング素子のオン故障を検出することが可能な多相モータ駆動装置を提供する。

【解決手段】U相のシャント抵抗に流れる電流の検出タイミングを、U相における上側のスイッチング素子Q1のオフ期間からオン期間へシフトさせて、このオン期間にU相のシャント抵抗に流れる電流に基づき、下側のスイッチング素子Q2がオン故障か否かを判定する。また、単に検出タイミングをシフトさせただけでは、下側のスイッチング素子Q2のオン期間において本来必要なU相電流を検出できなくなるため、他の2相のシャント抵抗に流れる電流に基づいて、U相電流の電流値を推定する。

(もっと読む)

281 - 300 / 722

[ Back to top ]