Fターム[5H740BA12]の内容

電力変換一般 (12,896) | 主回路スイッチング素子 (1,744) | トランジスタ (1,563) | 電界効果トランジスタ(FET) (722)

Fターム[5H740BA12]に分類される特許

401 - 420 / 722

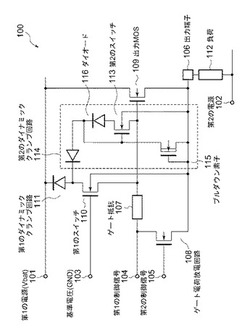

電力供給制御回路

【課題】出力トランジスタを負荷逆起電圧から保護すると共に、ダンプサージ電圧に対しても保護し、さらには、エネルギーは小さいがダンプサージ電圧よりも高い正電源サージに対しても出力トランジスタを保護する保護機能を備えた電力供給制御回路を提供する。

【解決手段】電源ライン101と出力端子106との間に接続される電力用半導体(出力MOSトランジスタ)109と、出力端子106に接続される負荷112と、第1の電源101と出力端子106との間の電圧差を制限する第1のダイナミッククランプ回路111と、このクランプ回路111と出力トランジスタ109との間に接続され基準電圧103と出力端子106の電圧との比較結果に基づいて導通状態が決定される第1のスイッチ110とを有する。さらに、電源ライン101と出力端子106との間の電圧差を制限して出力トランジスタ109を保護する第2のダイナミッククランプ回路114を設る。

(もっと読む)

インダクタ負荷ドライブ回路の逆起電力吸収回路

【課題】実装面積が小さいサージ吸収保護回路の提供。

【解決手段】インダクタ負荷RLは導線101に接続され、他端は導線102により電界効果トランジスタFETのドレインDに接続され、電界効果トランジスタに対して双方向ツェナーダイオードZDと第一抵抗RGSを導線104により並列に設け、電界効果トランジスタのソースSより導線103をアースし、第一抵抗RGSの他端側は導線105により前記導線103に接続し、双方向ツェナーダイオードと第一抵抗RGS間の導線104に電界効果トランジスタのゲートGに接続する導線106を分岐させ、この導線106の他端に第二抵抗R2を設けたインダクタ負荷ドライブ回路の逆起電力吸収回路100。

(もっと読む)

ドライブ回路

【課題】回路サイズを極力小さく抑えつつスルーレートを容易に制御可能なドライブ回路を提供する。

【解決手段】電流値制御回路31は、電源電圧VBを検出してβ(一定値)×VBなる電流IHを出力するように電流出力回路21に指令する。駆動指令信号Sd1がHレベル、駆動指令信号Sd2がLレベルに変化すると、MOSFET20がオンとなりMOSFET14、16をオフさせるとともに、MOSFET13にミラー比m×IHなる電流が流れる。このとき、電源線4からMOSFET13、MOSFET13のゲート・ドレイン間容量CgdおよびMOSFET24を介して電源線5に至る経路で電荷引き抜き電流IHが流れ、電源電圧VBによらず一定時間でMOSFET13のゲート・ドレイン間容量Cgdの放電が行われる。

(もっと読む)

レベルシフト回路およびこれを用いたDC−DCコンバータ

【課題】低電位系のMOSFETのドレイン−基板間に存在する寄生容量の影響により高電位系のラッチ回路が誤動作してしまうことを防止するレベルシフト回路を提供する。

【解決手段】本実施形態では、容量(C)51,52を配することにより、ノイズを吸収してラッチ回路100の誤動作を防止している。即ち、ラッチ回路100のインバータ(U1)41,インバータ(U2)42の入力端子と、高電位系であるラッチ回路100の基準電圧となる端子(V2L)6との間に、容量(C) 51,52を接続しているので、ノイズを容量(C)51,52に吸収させることが可能となり、ラッチ回路100の誤動作を防止することができる。

(もっと読む)

コンデンサモジュール,電力変換装置及び車載用電機システム

【課題】振動に強く、インダクタンスが低い接続部構造を備えたコンデンサモジュールの提供を課題とする。

【解決手段】上記課題は、複数のコンデンサを有するコンデンサモジュールにおいて、第1の幅広導体と第2の幅広導体を絶縁シートを介して積層した積層体を備え、この積層体を、前記複数のコンデンサを載置するとともに、電気的に接続される第1の平面部と、この第1の平面部に対して折り曲げられた第2の平面部と、前記第1の平面部及び第2の平面部の端部にそれぞれ設けられ、外部と接続される接続部とをもって構成することにより、解決できる。

(もっと読む)

バックゲート切替回路、充電制御装置、電子機器

【課題】本発明は、電界効果トランジスタのソース・ドレインいずれが高電位となるか不定であるシステムにも好適に用いることが可能なバックゲート切替回路、並びに、これを用いた充電制御装置及び電子機器を提供することを目的とする。

【解決手段】本発明に係るバックゲート切替回路20は、端子T2から電力供給を受けて電圧Va、Vbの比較信号を生成する比較部(CMP、R1〜R5、N1)と;端子T3から電力供給を受けて反転比較信号を生成するインバータINVと;トランジスタ14のバックゲートと端子T2との間に接続され、反転比較信号に応じてオン/オフ制御されるトランジスタP1と;トランジスタ14のバックゲートと端子T3との間に接続され、比較信号に応じてオン/オフ制御されるトランジスタP2と;インバータINVの入力端及びトランジスタP2のゲートをプルダウンする抵抗(R6、R7)と;を有して成る。

(もっと読む)

半導体素子駆動装置、電力変換装置、及びモータ駆動装置、並びに半導体素子駆動方法、電力変換方法、及びモータ駆動方法

【課題】直列接続IGBT3,4の接続点7のdV/dtによる誤動作発生時に、上下アーム短絡などの事故を回避できる高信頼性IGBT駆動装置を提供する。

【解決手段】高低圧側IGBT3,4は、デッドタイムを挟み相補的にオン/オフ制御される。これらデッドタイム期間中に、高圧側IGBT3をオフさせるリセットパルスRSを、例えば、次のような要領で発生させる。(1)低圧側IGBT4のオン指令LDの直前に、(2)低圧側IGBT4のオン指令LDの直前から、このオン指令LDと重なる期間tdをもつように、(3)デッドタイムDT期間中、継続して、(4)低圧側IGBT4がオンとなる直前のデッドタイム期間中、継続して、(5)高圧側IGBT3のオン状態を観測したとき、低圧側IGBTのオン指令を無効とするように、リセットパルスを生成する。

(もっと読む)

電力変換装置のゲート抵抗配置構造

【課題】スイッチングパワーデバイスのオンオフ時におけるサージ電圧からのスイッチングパワーデバイスの保護と、スイッチング損失の低減との両立を図ることができる電力変換装置のゲート抵抗配置構造を提供する。

【解決手段】電力変換装置の使用開始からの経過時間に応じて大きな温度上昇が生じるスイッチングパワーモジュール1と同じ基板15の実装面にこれと隣接して、あるいは、スイッチングパワーモジュール1と反対側の基板15の面にこれと対向して、ゲート抵抗3を実装、配置する。ゲート抵抗3には、スイッチングパワーモジュール1がいかなる温度であってもサージ電圧がスイッチングパワーモジュール1の耐電圧値以内に収まるような、温度変化に対する抵抗値変化の特性を有するものを使用する。望ましくは、サージ電圧に対してスイッチングパワーモジュール1の耐電圧値が過剰なマージンを持つことにならないような特性のゲート抵抗3を用いる。

(もっと読む)

パワートランジスタドライブ回路

【課題】保護機能を有し、小型化が容易なパワートランジスタドライブ回路を提供する。

【解決手段】パワートランジスタの制御信号を出力する出力端子と、前記パワートランジスタの異常信号が入力される異常検出端子と、外部抵抗に流れる電流を電圧に変換するIV変換回路と、AD変換回路と、ディジタル信号が保持される記憶回路と、前記記憶回路を用いて選択されるシャットダウン抵抗を少なくとも2つ含むソフトシャットダウン回路と、を備え、前記パワートランジスタのオフ状態において第1のシャットダウン抵抗が選択され、入力された前記異常信号により前記異常検出端子が低レベルに転じ、前記パワートランジスタをオフに切り替える前記制御信号が出力されると共に前記パワートランジスタのソフトシャットダウンが実行されることを特徴とするパワートランジスタドライブ回路が提供される。

(もっと読む)

スイッチング回路、回路、並びにスイッチング回路及び駆動パルス生成回路を含む回路

【課題】大電力用主電源スイッチングについて、ワイドバンドギャップ半導体スイッチング素子の誤作動を防ぐ技術を提供する。

【解決手段】スイッチング回路100は、ゲート電極、接地に接続されるソース電極、及び電源電位Vddに接続されるドレイン電極を有するノーマリーオフ型のスイッチング素子130と、スイッチング素子130のゲート電極及びソース電極に、それぞれ接続される、ドレイン電極及びソース電極、並びに、ゲート電極を有するノーマリーオン型FET132とを含む。本回路100を駆動するための電源供給が無い場合、ノーマリーオン型FET132はオン状態となる。その結果、スイッチング素子130のゲート/ソース間電位は0Vとなり、スイッチング素子130はオフ状態を保つ。本回路100は、雑音電圧によるスイッチング素子130の誤作動を防ぐ。

(もっと読む)

スイッチング回路装置及び方法

【課題】電力供給装置に接続可能である負荷を実用するための回路を提供する。

【解決手段】本回路(200)は複数の三端子スイッチ(215)と1つの制御供給装置(252)とを含む。複数の三端子スイッチ(215)は電力供給装置(210)と負荷(205)との間に接続可能な直列の導電路(250)を規定する。複数の三端子スイッチ(215)の各々はソース端子(235)、ドレイン端子(240)及びゲート端子(245)を含む。制御供給装置(252)は制御電圧を生成するものであり且つ複数の三端子スイッチの各々のゲート端子とソース端子との間に電力接続関係にある。複数の三端子スイッチ(215)の各々はそのそれぞれのゲート端子(245)における制御電圧に応答して、複数の三端子スイッチの各々のそれぞれのソース端子(235)とそれぞれのドレイン端子(240)との間の接続部(255)を閉成する。

(もっと読む)

スイッチング回路

【課題】 IC化を容易にでき、特性を安定化させることができるスイッチング回路を提供すること。

【解決手段】 制御信号生成する構成は、スイッチング素子M1の制御信号のターンオン時の作動閾値電圧近傍までの昇圧を、電源V2からの注入で早めるパルス発振器P2、トランジスタQ1、電源V2と、スイッチング素子M1の制御信号のターンオフ時の作動閾値電圧近傍までの降圧を、電流経路101と別の電流経路102,103で電流を流すことで早めるダイオードD2、トランジスタQ2、電源V3を備えた。

(もっと読む)

スナバ回路及びこれを備える電力変換回路

【課題】回路の大型化を回避しつつ、供給電圧へ重畳されるノイズ又はサージ等を極力排除し、併せて、製造コストの高騰を抑え得るスナバ回路を提供する。

【解決手段】陽極側に配置される電圧制御回路Cvと陰極側に配置される保護抵抗Rhとが直列に接続された直列回路Cdと、直列回路Cdの両接続端と電圧制御回路Cv及び保護抵抗Rhの間とにそれぞれ接続されたスイッチング素子Ssとを少なくとも備え、かかるスイッチング素子Ssは、陽極側から陰極側へ向けて透過電流Isが流れる配置とされているスナバ回路。

(もっと読む)

炭化ケイ素静電誘導トランジスタの制御装置及び制御方法

【課題】電力用変換器の過電流においてオン抵抗損失の著しい増大を抑制して、電力用変換器の小型・軽量化および低価格化をはかる。

【解決手段】定格電流容量の5倍ないし20倍のサージ電流が流れる電力用変換器に炭化ケイ素を素材とした静電誘導トランジスタを適用するにあたり、該静電誘導トランジスタのオン時のゲート電圧を定格電流以下の正常動作時にはゲート接合のビルトイン電圧以下として高速、低損失、高効率の電力変換を行い、定格を超える過電流が流れた場合にかぎりゲート電圧をビルトイン電圧以上に昇圧することにより過電流による素子破壊を防止する制御方法によって変換器に使用される炭化ケイ素静電誘導トランジスタの電流容量を変換のそれを大幅に超えない小容量とする。

(もっと読む)

マルチチップ型半導体装置およびその製造方法

【目的】低コストで過熱検出温度のバラツキ範囲や過電流検出値のバラツキ範囲を低減できるマルチチップ型半導体装置およびその製造方法を提供する。

【解決手段】第1ウェハ41内に形成された第1の半導体チップの特性(検知電圧線や検知電流線)と第2ウェハ42内に形成された第2の半導体チップの特性(検出電圧レベルや検出電流レベル)をクラス別にグループ分けする。このグループ分けを第1の半導体チップが形成されている第1ウェハ41内の領域(A,B,C)と第2の半導体チップが形成されている第2ウェハ42内の領域(a、b、c)で行う。領域でクラス別にグループ分けされた第1の半導体チップと第2の半導体チップを、特性バラツキが相殺される領域にあるもの同士で組み合わせる。

(もっと読む)

ドライブ回路

【課題】ブリッジ方式回路において互いに直列接続される2つのスイッチング素子が同時にオンしないようにそれらスイッチング素子を駆動することが可能なドライブ回路を提供することを目的とする。

【解決手段】互いに直列接続されるMOSFET32、33及びMOSFET34、35がそれぞれ直流電源36に並列接続されるブリッジ方式回路31のMOSFET32〜35をオン、オフさせるためのドライブ回路1において、出力端子24の電位を上昇させてMOSFET32をオンさせるnpnバイポーラトランジスタ22をオンさせるための電荷を蓄積するコンデンサ12と、MOSFET32がオンしたときMOSFET33のドレイン−ゲート間の寄生容量に蓄積される電荷を引き抜くpnpバイポーラトランジスタ23をオンさせるための電荷を蓄積するコンデンサ13とを備える。

(もっと読む)

負荷駆動回路

【課題】簡易な構成で、直流電源の出力電圧の変動による半導体素子の導通を防止して、意図しない負荷電流による誤動作を防止する負荷駆動回路を提供する。

【解決手段】電源2から負荷1への電力供給経路に直列に接続されオン/オフ動作により負荷1に流れる電流を制御する半導体素子3を有する負荷駆動回路において、半導体素子3のオン/オフを制御する制御部4と、電源2の出力電圧の変動を検出して検出信号を生成する電圧変動検出部5と、電圧変動検出部5により生成された検出信号が入力された場合に、電源2の出力電圧の変動により半導体素子3がオンする前に半導体素子3を強制的にオフさせる遮断部6とを備える。

(もっと読む)

ゲート駆動回路の制御方法

【課題】スイッチング素子の入力容量を高速に充放電させ、スイッチング速度の増加、スイッチング損失の低減を可能にしたゲート駆動回路の制御方法を提供する。

【解決手段】直流電源11,12に接続された複数のスイッチ4〜6を備え、これらのスイッチ4〜6のオン・オフによりN(Nは3以上の整数)個のレベルの電圧を出力して半導体スイッチング素子1のゲートに供給するゲート駆動回路の制御方法において、スイッチング素子1をオンさせる時に、出力電圧のレベルを第1の電圧レベルからそれより高い第2の電圧レベルに変化させ、その後、出力電圧のレベルを第1のレベルと第2の電圧レベルとの間の第3の電圧レベルに変化させるように前記スイッチ4〜6をオン・オフさせる。

(もっと読む)

DC/DCコンバータ及びこれを用いた駆動装置

【課題】本発明は、入力バイパスコンデンサの音鳴りを低減することが可能なDC/DCコンバータを提供することを目的とする。

【解決手段】本発明に係るDC/DCコンバータは、入力電圧の印加端と接地端との間に接続される入力バイパスコンデンサを用いて前記入力電圧を平滑化し、これを所望の出力電圧に変換して負荷に供給するDC/DCコンバータであって、前記入力バイパスコンデンサは、複数個のコンデンサが並列接続されたものである構成とされている。

(もっと読む)

半導体素子制御装置

【課題】電源電圧が低下した場合でも、制御対象とする半導体素子を適切に制御することができる半導体素子制御装置を提供する。

【解決手段】電圧付与回路18は、電源電圧Vccを所定の閾値電圧Vthと比較して、Vcc≦Vthであれば、プリドライブ回路2のグランド側端子にグランドレベル近傍の電圧である仮想グランド電圧Vcpを付与し、Vcc>Vthであれば、前記グランド側端子に電源電圧Vccとクランプ制御用電圧Vgsとの差電圧を付与する。

(もっと読む)

401 - 420 / 722

[ Back to top ]