Fターム[5H740BA12]の内容

電力変換一般 (12,896) | 主回路スイッチング素子 (1,744) | トランジスタ (1,563) | 電界効果トランジスタ(FET) (722)

Fターム[5H740BA12]に分類される特許

61 - 80 / 722

電源回路

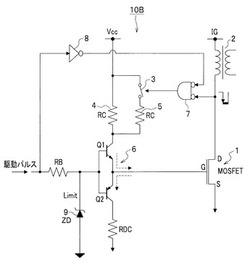

【課題】高速スイッチング素子である電圧駆動型トランジスタ(MOSFET)のターンオン・オフ時の電圧変化(dV/dt)と電流変化(di/dt)を緩和して、ノイズとサージ電圧の発生を抑制する電源回路を提供する。

【解決手段】トランス2に流れる電流をスイッチングさせるためのMOSFET1のゲート抵抗値を、スイッチング期間内で、MOSFET1のドレイン電圧Vdsの変化の検出と共に切り替える、MOSFET1のゲート電圧Vgは、MOSFET1のゲート電圧の最大定格Vgmax以下とする。

(もっと読む)

印刷基板の電力変換装置

【課題】精度の高い電流制御、電圧制御を提供する。

【解決手段】主端子と基準端子と制御端子を有する第一のスイッチと、第二のスイッチまたは整流器、入力側コンデンサと出力側コンデンサを各1以上持ち、インダクタを持つ電力変換回路であって、相互接続点と基準電位または出力または入力間の電流によって生じる電圧を利用して、出力の制御や保護を行う回路であって、印刷基板を用いたものであって、前記電圧の生じている素子のうち相互接続点でない側と接合された印刷基板上の導体と、その導体と回路図上は同電位となるべき基準電位または入力または出力のいずれかと結合された入力コンデンサあるいは出力コンデンサの端子と接合された導体が、最短距離で結合されないように、空隙によって分断された構造を持つもの。

(もっと読む)

インバータ装置

【課題】デッドオフ時間中の還流電流の損失を小さくすると共に、寄生ダイオードの逆回復時間を短くすることが可能なインバータ装置を提供する。

【解決手段】4つの双方向スイッチ素子Q1〜Q4でブリッジ回路を構成し、互いに直列接続されていない2組のスイッチ素子Q1とQ4及びQ2とQ4を、デッドオフ時間ΔTを介して交互にオン及びオフさせる。デッドオフ時間中ΔT、そのデッドオフ時間の直前に非導通であったスイッチ素子の組を一時的に導通させて還流電流を流す。

(もっと読む)

駆動装置

【課題】電圧駆動型素子を駆動状態と非駆動状態の間で遷移させるときの遷移期間において、電圧駆動型素子のゲート電圧を柔軟に制御するための技術を提供する。

【解決手段】駆動装置1は、電圧駆動部3と電流駆動部4を備えている。電圧駆動型素子2を駆動状態と非駆動状態の間で遷移させるときの遷移期間のうちの一部の区間では、電圧駆動部3を利用した電圧駆動型素子2のゲート電圧Vgの制御が停止され、電流駆動部4を利用した電圧駆動型素子2のゲート電圧Vgの制御が実行されるように構成されている。

(もっと読む)

スイッチング電源回路および電動機の制御装置

【課題】スイッチング電源で、電流検出回路を設けずに、負荷変動に伴う電圧上昇の抑制を可能とする。

【解決手段】スイッチング電源回路14は、一次巻線と二次巻線とを有するトランス41と、スイッチング信号を一次巻線に入力してトランス41を駆動する一次側回路40と、二次巻線に接続され、一次側回路40とは電気的に絶縁されているゲートドライブ回路20−nとを具備している。ゲートドライブ回路20−nは、モータECU100からのPWM信号によって駆動されるゲート駆動回路21−nと、ゲートドライブ回路20−nに流れる電流を増大させるブリーダ抵抗R20−nとを有し、モータECU100からのPWM信号を検出した場合に、ブリーダ抵抗R20−nに流れる電流値を減少させる。

(もっと読む)

ゲート駆動回路

【課題】 リカバリー電流を低減させつつ、出力MOSトランジスタのスイッチング応答性を高くすることができるゲート駆動回路を提供する。

【解決手段】 制御信号Scdの信号レベルが所定の第1レベルLから第2レベルHへ遷移する第1遷移を契機として出力MOSトランジスタ2のゲートへ充電を開始する第1チャージ回路6と、制御信号Scdの第1遷移または第1期間Tp1の経過を契機として出力MOSトランジスタ2のゲートへの充電を開始する第2チャージ回路7と、制御信号Scdの第1遷移から第1期間Tp1より長い所定の第2期間Tp2経過後に出力MOSトランジスタ2のゲートへ充電を開始する第3チャージ回路8とを備え、第2チャージ回路7の単位時間あたりの充電量は、第1チャージ回路6および第3チャージ回路8の単位時間あたりの充電量より少ない。

(もっと読む)

電圧制御型スイッチング素子のゲート駆動回路

【課題】電圧制御型スイッチング素子のスイッチング時に、サージ電圧・サージ電流及びスイッチングノイズを抑制しながら、誤動作の発生を抑制することができる電圧制御型スイッチング素子のゲート駆動回路を提供する。

【解決手段】電圧制御型スイッチング素子2のゲートにゲート電圧を供給して当該電圧制御型スイッチング素子2を駆動するゲート駆動回路であって、直列に接続された高電位側スイッチング素子M1及び低電位側スイッチング素子M2と、前記高電位側スイッチング素子M1と高電位電源との間及び前記低電位側スイッチング素子M2と低電位電源との間の少なくとも一方に介挿された第1の可変抵抗VR11,VR12と、前記第1の可変抵抗VR11,VR12の抵抗値を調整する制御回路4とを備えている。

(もっと読む)

半導体装置

【課題】インバータ回路とそれを構成するスイッチ素子を駆動・制御する駆動・制御回路において、追加回路規模が少なく、所望の負電位を動的に印加できる駆動・制御回路、また、インバータ回路における短絡電流を削減し、損失の少ない電力変換回路を提供する。

【解決手段】半導体装置において、第1,第2スイッチ素子(下側アームのスイッチ素子LSW,同様の上側アームのスイッチ素子)を有するインバータ回路と駆動回路(L側ゲート駆動回路LGD,同様のH側ゲート駆動回路)と制御回路とを有し、駆動回路は、スイッチ素子のゲート電極をソース電位に駆動する回路と、スイッチ素子のゲート電極を負電位に駆動する回路とを有し、負電位に駆動する回路の出力ノードとスイッチ素子との間に直列にコンデンサが接続され、制御回路は、スイッチ素子がオフ状態からオン状態になる直前のスイッチ素子のゲート電極の電圧をソース電位と同じであるように制御する。

(もっと読む)

半導体集積回路

【課題】絶縁ゲート型半導体素子を駆動する半導体集積回路内において、貫通電流の発生を抑制することが可能な技術を提供することを目的とする。

【解決手段】半導体集積回路は、制御信号Vinを遅延させて得られる遅延信号を、PMOS1及びNMOS2のゲート端子に出力する遅延回路19を備える。NMOS4が、第2出力信号の変化に応じてオンからオフに切り替えられるタイミング(t2)は、PMOS1が、遅延信号の変化に応じてオフからオンに切り替えられるタイミング(t2)よりも遅くなく、かつ、PMOS3が、第1出力信号の変化に応じてオンからオフに切り替えられるタイミング(t7)は、NMOS2が、遅延信号の変化に応じてオフからオンに切り替えられるタイミング(t7)よりも遅くない。

(もっと読む)

AC/DC入力対応電源装置

【課題】部品点数を削減して小型化を図ることができると共に、効率を良くすることができるAC/DC入力対応電源装置を提供する。

【解決手段】PFC回路の入力段に、AC100〜240V用に巻き数が最適化されたコイル1とDC−48V用に巻き数が最適化されたコイル2を用意し、入力(IN)にDC−48Vが与えられた場合は、スイッチ(SW)4を切り替えてDC−48V用のコイル2を選択し、入力(IN)にAC100〜240Vが与えられた場合は、スイッチ(SW)4を切り替えてAC100〜240V用のコイル1を選択する。

(もっと読む)

スイッチング回路及び半導体モジュール

【課題】スイッチング制御する制御回路の負担を軽減するスイッチング回路を提供する。

【解決手段】第1のスイッチング素子の制御電極と第1のスイッチング素子をスイッチング制御する制御回路との間に接続される抵抗と、第1のスイッチング素子の制御電極と第1のスイッチング素子の低電位側電極との間に接続される第1のコンデンサと、第1のコンデンサと直列に接続される第2のスイッチング素子とを備え、第2のスイッチング素子の高電位側電極は、第1のスイッチング素子の制御電極に電気的に接続され、第2のスイッチング素子の低電位側電極は第1のスイッチング素子の低電位側電力端子に電気的に接続され、第2のスイッチング素子の制御電極は、抵抗と制御回路の間に接続されている。

(もっと読む)

整流器のスナバ回路

【課題】スナバの付加による直流部の電位変動を防止しつつ、半導体スイッチング素子の過電圧保護を図る。

【解決手段】ダイオード5,6,7,8で構成される整流器の交流入力端子間に双方向スイッチを構成するMOSFET3,4を備え、交流電源1の電圧と同期してスイッチングを行うことで端子Pと端子N間の直流電圧を調整している。MOSFET3,4にはスナバ回路201〜205を付とともに、ダイオード206を付加することで、コンデンサ204両端間の電位が変動しないようにしつつ、スナバ回路201〜205のスイッチング素子の過電圧保護が図る。

(もっと読む)

スイッチング回路

【課題】スイッチング素子の動作に起因するノイズの大きさが低減された、小型で製造コストの低いスイッチング回路を提供する。

【解決手段】スイッチング素子と、一定周期でパルス波のドライバ信号を出力するドライバ信号出力回路と、ドライバ信号のパルス波の周期を複数含む一定期間内において駆動力を変化させながら、ドライバ信号の周期に同期してスイッチング素子を駆動する駆動回路とを備える。

(もっと読む)

半導体装置および電子機器

【課題】良好な逆回復特性と良好なEMCとを同時に実現することが出来て、かつ、従来の半導体装置よりも安価である半導体装置及び電子機器を提供する。

【解決手段】半導体装置1は、FET3のソースとMOSFET4のドレインとが接続されるとともに、一端が、FET3のゲートに接続され、他端が、MOSFET4のソースに接続される抵抗Rgsと、アノードが、FET3のゲートに接続され、カソードが、MOSFET4ソースに接続されるダイオードD1とを備える。

(もっと読む)

過電流保護電源装置

【課題】直流電源17からスイッチ用のFET18を経て負荷16へ電力を供給する電源装置においては、2種類の保護回路が設けられていた。第1は、該FETの温度を検出し、所定温度に達したら該FETをオフする回路である。第2は、デッドショート時のような大過電流が流れた場合には、電流を所定電流に制限する電流制限回路である。保護回路を2種類設けると、部品コストが大になっていた。

【解決手段】比較基準電圧生成回路40を電流供給部41と比較基準電圧発生抵抗部46とで構成し、比較基準電圧VX を生成する。過電流検出電圧生成回路50を電流供給部51と過電流検出抵抗部54とで構成し、FET18の電圧VDSが増大すると減少する電流検出電圧VY を生成する。電圧VDSの増大を検出してFET18をオフすれば、過電流保護も過熱保護も可能となる。

(もっと読む)

レベルシフト回路、制御回路及びDC−DCコンバータ

【課題】信号遅延が小さく高速化可能なレベルシフト回路、制御回路及びDC−DCコンバータを提供する。

【解決手段】実施形態によれば、差動電流生成回路と電流減算回路とを備えたレベルシフト回路が提供される。前記差動電流生成回路は、第1の高電位端子と第1の低電位端子との間に接続され、入力される制御信号に応じて、規定値または前記規定値よりも大きい電流値に変化する電流と前記規定値よりも大きい電流値または前記規定値に変化する電流とを一対の差動電流として生成する。前記電流減算回路は、第2の高電位端子と第2の低電位端子との間に接続され、前記一対の差動電流を受けて、前記一対の差動電流の差に等しい電流を生成する。

(もっと読む)

電動機駆動システム

【課題】電源側に回り込むノイズを低減することができる電動機駆動システムを提供すること。

【解決手段】電動機駆動システムは、電源ラインに接続された複数のスイッチング素子を有するインバータ装置100と、インバータ装置100から出力される交流電圧によって駆動される電動機200と、インバータ装置100と電動機200との間に挿入されるLCフィルタ回路300と、電導部材によって形成されて複数のスイッチング素子が固定される冷却体400と、複数のスイッチング素子の電源ライン側端子と冷却体400との間に挿入されるコンデンサと抵抗からなる直列回路とを備える。LCフィルタ回路300は、インバータ装置100から電動機200に動作電力を供給する電力供給線202等に挿入されるインダクタ310等と、一方端がインダクタ310等の一方端に接続されるとともに他方端が冷却体400に接続されるコンデンサ320等とを有する。

(もっと読む)

レベルシフト回路、制御回路及びDC−DCコンバータ

【課題】低消費電力で高速動作可能なレベルシフト回路、制御回路及びDC−DCコンバータを提供する。

【解決手段】実施形態によれば、電流生成回路と、電流スイッチ回路と、保護回路と、を備えたレベルシフト回路が提供される。前記電流生成回路は、第1の高電位端子と第1の低電位端子との間に接続され、第1の電流を生成して第1の出力線に出力する。前記電流スイッチ回路は、第2の高電位端子と第2の低電位端子との間に接続され、前記電流生成回路よりも大きい電流供給能力で前記第1の電流を受け、入力信号に応じて前記第1の電流を流しまたは前記第1の電流を遮断する。前記保護回路は、前記電流生成回路と前記電流スイッチ回路との間において前記第1の出力線に接続され、前記第1の出力線の電位を前記第1の低電位端子の電位以上で前記第1の高電位端子の電位以下に制限して前記電流生成回路を過電圧から保護する。

(もっと読む)

駆動回路

【課題】複数のスイッチ素子を備える装置を小型化すること。

【解決手段】駆動回路1は、キャパシタC21と、充電部を構成する抵抗R21およびダイオードD21と、を備える。キャパシタC21は、スイッチ素子Q11のゲートと、スイッチ素子Q21のゲートと、の間に設けられ、制御部22の端子Y3には、スイッチ素子Q11のゲートが接続されるとともに、キャパシタC21を介してスイッチ素子Q21のゲートが接続される。抵抗R21およびダイオードD21で構成される充電部は、スイッチ素子Q21のゲートとソースとの間に設けられる。

(もっと読む)

直流電源装置

【課題】ワイドバンドギャップ半導体を用いたFETを使用した、非常に大きな電力を直流に変換する直流電源装置において、1つの駆動電源にて各FETに正と負の駆動電圧を与えることで、低価格で小型かつ高効率の直流電源装置を得る。

【解決手段】入力段に突入電流保護回路1を有し、各FET3〜6に対し独立した駆動回路D3〜D6を有する。高電圧側のFET3、5をドライブトランス14により駆動し、低電圧側のFET4、6においては、駆動電源17およびFET4、6に流れる電流で充電される負バイアス用コンデンサ24によりゲート電圧を供給可能に構成する。

(もっと読む)

61 - 80 / 722

[ Back to top ]