Fターム[5H740BA12]の内容

電力変換一般 (12,896) | 主回路スイッチング素子 (1,744) | トランジスタ (1,563) | 電界効果トランジスタ(FET) (722)

Fターム[5H740BA12]に分類される特許

141 - 160 / 722

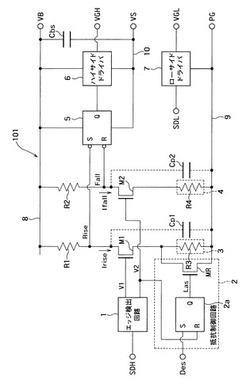

ドライブ制御回路、制御装置、スイッチング電源装置、および、制御方法

【課題】入力電圧の急変や負荷短絡時等における共振外れにより、中間電位VSが急変した場合にも、ハイサイドドライブ信号SDHとローサイドドライブ信号SDLに応じて、所定の動作をすることが可能なドライブ制御回路を提供する。

【解決手段】ドライブ制御回路101は、ハイサイドスイッチ素子Q1とローサイドスイッチ素子Q2との間の中間端子Xに接続された共振回路の状態を検出することにより得られた状態検出信号Desに応じて、第1のMOSトランジスタM1の他端と第2の電位線9との間の抵抗値を下げる抵抗制御回路2を備える。

(もっと読む)

ドライブ信号生成回路、制御装置、スイッチング電源装置、および、制御方法

【課題】発振信号にノイズが発生してデッドタイムパルスが短くなる場合でも、ハイサイドドライブ信号およびローサイドドライブ信号を切り替えて出力することが可能なドライブ信号生成回路を提供する。

【解決手段】ドライブ信号生成回路1は、第1のパルス信号を出力するデッドタイムパルス生成回路1aと、第2のパルス信号Aを出力するデッドタイム調整回路1bと、第3のパルス信号Bを出力する補償パルス生成回路1cと、第2のパルス信号Aと第3のパルス信号Bとの論理和を演算し、この演算結果に応じた第4のパルス信号Zを出力するOR回路1dと、第4のパルス信号Zに応じて、ハイサイドドライブ信号SHおよびローサイドドライブ信号SLを出力する論理回路1eと、を備える。

(もっと読む)

スイッチング素子の駆動回路

【課題】パワースイッチング素子S#*がオン状態であるときとオフ状態であるときとの双方においてそのゲートの電圧を適切に検出することが困難なこと。

【解決手段】パワースイッチング素子S#*のゲートおよびエミッタ間は、ゲート電圧が低下することをトリガとして、オフ保持用スイッチング素子40によって短絡される。オフ保持用スイッチング素子40は、集積回路(ドライブIC20)によってオン操作される。パワースイッチング素子S#*のゲートに電圧を印加する電源28,30はそれぞれ端子電圧が相違し、ゲート電圧が上昇することで端子電圧の低い電源30から端子電圧の高い電源28へと切り替える。パワースイッチング素子S#*がオフ状態であるときには端子T1の電圧を、また、オン状態であるときには端子T2の電圧を、それぞれゲート電圧として検出する。

(もっと読む)

半導体スイッチ、制御装置、電力変換装置及び半導体装置

【課題】異常停止時においても主素子の逆並列ダイオードを通流させることで、還流ダイオードにおける発熱を抑え、還流ダイオードの冷却が容易にした電力変換装置を提供する。

【解決手段】実施形態の半導体スイッチ制御装置は、各相のアーム毎に、主素子3の負極と補助素子5の負極とを接続して主素子の正極を正極端子7とし、補助素子の正極を負極端子8とし、正極端子と負極端子との間に負極端子から正極端子に向かう方向が順方向となるように還流ダイオード4を並列接続した半導体スイッチに対して、主素子と補助素子とをそれぞれ個別にON/OFF制御する。

(もっと読む)

電源装置

【課題】回路が複雑でなく、スイッチング素子の保護機能を向上することができる電源装置を提供する。

【解決手段】電源装置10は、一端が電源端子に接続され、他端が出力端子に接続された主スイッチング素子15と、カソード端子が主スイッチング素子の他端に接続され、アノード端子が接地された整流素子と、主スイッチング素子を制御する制御信号を電圧レベル変換して出力するレベルシフト回路と、ドライバ回路と、レベルシフト回路とドライバ回路に電源供給するブートストラップ回路と、電源からの電圧を所定の電圧に変換してブートストラップ回路に電源供給するレギュレータとを備えた電源装置であって、主スイッチング素子をオンする制御信号が入力されている期間中は、レギュレータからブートストラップ回路への電源供給を遮断するレギュレータ電源供給遮断手段23を設けた。

(もっと読む)

保護回路

【課題】

本発明は、FET1の劣化ないし破壊を防止するための保護回路を提供することを目的とする。

【解決手段】

主スイッチ2をONすると+電源3および−電源4に電圧が供給されコンデンサC3およびC4により+電源と−電源は徐々に立ち上がる。この時電子スイッチ21はOFFに設定されている。−電源4が規定値まで立ち上がると電子スイッチ21はONとなりFET1のドレインに+電源3が印加される。主スイッチ2をOFFとすると+電源3と−電源4はコンデンサC3およびC4により徐々に電圧は下がり始める。−電源が下がり始めると電子スイッチ21はOFFとなりFET1のドレイン電圧7はOFFとなる。

(もっと読む)

モータ駆動回路

【課題】スイッチング損失が小さく、かつ、安定してモータを動作させることが可能なモータ駆動回路を提供する。

【解決手段】モータ駆動回路1は、インバータ回路2と、制御回路部3と、バッファ回路4a〜4cと、抵抗R2と、キャパシタ素子C1〜C3とを備えている。バッファ回路4aは、PMOSトランジスタQ1aと、NMOSトランジスタQ1bと、抵抗R1aと、抵抗R2aとを有する。バッファ回路4a〜4cにMOSトランジスタを用いるため、ターンオン時間Tonおよびターンオフ時間Toffを短くでき、スイッチング損失を小さくできる。また、MOSトランジスタQ1のゲートをハイに設定する場合は抵抗R2aを介して充電し、ロウに設定する場合は抵抗R2a,R1aを介して放電するため、ターンオフ時間Toffよりターンオン時間Tonが長くなる。そのため、すべての相をオフに設定するデッドタイムを設ける必要がなく、モータを安定して駆動できる。

(もっと読む)

レベルシフト回路及びスイッチング電源装置

【課題】dv/dt印加時に誤動作を防止し且つローサイド側からハイサイド側へ信号を伝達し低電圧でも広い範囲で動作するレベルシフト回路。

【解決手段】トランジスタMN3とトランジスタMN4とをオン/オフさせるパルス発生回路10、第1抵抗R1の両端に第3抵抗R9と非線形特性を有し且つ一定以上のdv/dt過渡信号が印加された場合にオンするダイオードD3〜D6とが接続された直列回路、第2抵抗R2の両端に第3抵抗と同じ抵抗値を有する第4抵抗R10とダイオードとが接続された直列回路、MN3がオンである場合にセット信号、MN4がオンである場合にリセット信号を生成し、MN3のドレインにおける電位とMN4のドレインにおける電位との間において電圧差が生じていない場合にはいずれの信号も生成しない制御部、セット信号とリセット信号とに基づいて入力信号をレベルシフトした出力信号を出力するフリップフロップ12を備える。

(もっと読む)

電源逆接続保護回路

【課題】外部直流電源の逆接続や負サージの印加を認識し、確実に電子制御装置に過電流が発生することを防止できる電源逆接続保護回路を提供する。

【解決手段】外部直流電源の高電位側端子2と低電位側端子3とに接続される整流器12が備えられる。この整流器12の高電位側ノード13及び低電位側ノード14は逆接続保護制御回路11に接続される。外部直流電源の逆接続状態でも、整流器12は高電位側ノード13に高電位を発生し、低電位側ノード14に低電位を発生する。従って、逆接続保護制御回路11の比較器15は、電源端子3とグランド端子5への外部直流電源の逆接続状態を判定し、逆接続保護素子駆動回路16は逆接続保護素子10を確実にオフ動作させる。その結果、グランド端子5から電源端子3への過電流は確実に防止される。

(もっと読む)

ゲート駆動回路の設計支援装置および設計支援方法

【課題】ゲート駆動回路の設計を、短TAT化する設計支援装置を提供する。

【解決手段】半導体素子のスイッチングを制御するゲート駆動回路に含まれる回路素子のパラメーを用いて前記半導体素子のスイッチング電圧を計算する回路解析部と、前記スイッチング電圧によって前記ゲート駆動回路を搭載するシステムに発生する電磁放射ノイズを計算する電磁界解析部と、前記電磁放射ノイズが目標値に収まっているか否か判定する第1の判定部と、前記電磁放射ノイズが目標値に収まっていない場合に、前記電磁放射ノイズを抑制するように前記回路素子のパラメータを改良する第1の回路改良部と、前記改良したパラメータを用いて前記回路解析部が計算したスイッチング電圧に基づいて電磁放射ノイズを推定するノイズ推定部と、を備え、中央処理装置が、前記回路素子のパラメータを最適化する。

(もっと読む)

モータ制御装置及び電動パワーステアリング装置

【課題】より簡素な構成にて、駆動回路を構成する各スイッチング素子の動作遅延を最小限に抑えつつ、そのスイッチング伴う電流変化を穏やかにすることのできるモータ制御装置を提供すること。

【解決手段】各FET30a〜30fのゲート端子に対する電圧印加経路Lgcには、抵抗可変回路34が設けられる。抵抗可変回路34は、第3抵抗R3が設けられた主経路LprとスイッチSWが設けられた迂回経路Lbpとを備えてなるとともに、そのスイッチSWは、制御回路CLにより作動が制御される。そして、制御回路CLは、各FET30a〜30fのゲート駆動電圧Vgに基づいて、当該ゲート駆動電圧Vgの変化が平坦化する領域にある場合に、迂回経路Lbpを遮断すべくスイッチSWを作動させる。

(もっと読む)

駆動回路

【課題】電源部品を減らし、安価な構成の駆動回路。

【解決手段】一次巻線N1と第1の二次巻線N2とを有し、一次巻線に駆動信号が印加されるトランスT1と、トランスの第1の二次巻線の一端と第1スイッチング素子Q1の制御端子との間に接続された第1コンデンサC3と、第1ツェナーダイオードZN1と第2ツェナーダイオードZN2とが直列に接続され、第1コンデンサと第1スイッチング素子との接続点に第1ツェナーダイオードのカソードに接続され、トランスの第1の二次巻線の他端に第2ツェナーダイオードのカソードが接続された第1直列回路とを有する。

(もっと読む)

駆動装置

【課題】駆動回路やトランジスタにおいてばらつきがあっても、PWM駆動信号の駆動デューティ成分が小さい場合にも、上側トランジスタと下側トランジスタのシュート・スルー(貫通状態)を防止する。

【解決手段】入力端子の第2レベルまたは第1レベル信号に応じてスイッチングデバイスの制御端子に駆動電流をシンク出力するシンク回路と、スイッチングデバイスのオフ期間中に制御端子を経て容量性の電流をシンクする電流シンクトランジスタと、入力端子の信号に応じてソース回路の入力駆動信号と、シンク回路あるいは前記シンクトランジスタへの入力駆動信号とを生成するI/F回路と、シンク回路または前記シンクトランジスタへの入力駆動信号をシンク回路かあるいはシンクトランジスタのどちらに入力駆動信号として出力するかを選択するセレクタと、この選択動作を制御するセレクタへの選択信号を受ける入力端子とを備える。

(もっと読む)

駆動回路及びこれを含む電源装置及び電気装置

【課題】駆動回路及びこれを含む電源装置及び電気装置を提供する。

【解決手段】制御端子及び出力端子を有するスイッチング素子、及び制御端子と出力端子との間の電圧が臨界電圧以下に維持されるように、前記スイッチング素子を制御するための駆動電圧が目標レベルに達するのにかかる上昇時間を制御する制御部を含み、制御端子と出力端子との間の電圧が臨界電圧より高ければ、制御端子と出力端子との間に漏れ電流が発生する電源装置である。

(もっと読む)

位相制御装置

【課題】位相制御装置において、トランジスタに与えるゲート駆動電圧を、簡単な構成を用いて全波整流により生成する。

【解決手段】スイッチング手段3は、ソースが交流電源1の一端と、ドレインが負荷2の一端と接続される第1トランジスタ31と、ソースが交流電源1の他端と、ドレインが負荷2の他端と接続される第2トランジスタ32とを含む。定電圧生成手段7のダイオードブリッジ71の一方の入力端子は、交流電源1と第1トランジスタ31の接続点に接続され、ダイオードブリッジ71の他方の入力端子は、交流電源1と第2トランジスタ32の接続点に接続される。定電圧生成手段7の出力端子間には、抵抗72とツェナーダイオード74及びコンデンサ73の並列回路とが直列に接続される。トランジスタ31,32の制御端子の電位は、この並列回路と抵抗72の接点の電位と、ダイオードブリッジ71の負側の出力端子の電位との間で切り換わる。

(もっと読む)

電子制御装置

【課題】複数の開閉素子と第二の多チャンネルAD変換器を内蔵したインテリジェントパワーモジュール(IPM)において、多様な制御信号に対応したデジタル変換値をマイクロプロセッサで正確に読み出す。

【解決手段】電子制御装置100A内のCPU110Aは、直並列変換器114a、114bと第二の多チャンネルAD変換器116bを介してIPM190A内の開閉素子140nの通電電流を読み出し、開閉素子140nは、シリアル制御信号SRn又はパラレル制御信号PWMnによって開閉制御され、読出時期制御回路170nは、制御信号の種別を問わず常に開閉素子140nが閉路駆動されている期間に読出しするよう読出タイミングを調整するように構成され、直並列変換器によってIPMとマイクロプロセッサ間の配線数が削減できると共に、シリアル信号とパラレル信号間のタイミング誤差を調整して、正確にデジタル変換値を読み出す。

(もっと読む)

電力用半導体装置

【課題】ブートストラップコンデンサを十分に充電することができ、かつ回路を簡略化及び小型化することができる電力用半導体装置を得る。

【解決手段】ブートストラップコンデンサCbsの一端が、トーテムポール接続されたハイサイドスイッチング素子M1とローサイドスイッチング素子M2の接続点に接続され、他端がハイサイド駆動回路10aの電源端子に接続されている。ブートストラップダイオードDbsは、ローサイド駆動電源LVからの電流をブートストラップコンデンサCbsの他端に供給する。ハイサイド駆動回路10aがハイサイドスイッチング素子M1をONにし、ローサイド駆動回路10bがローサイドスイッチング素子M2をOFFにする場合に、ブートストラップ補償回路12は、ブートストラップコンデンサCbsの他端に、高圧側電位を基準電位とするフローティング電源FVからの電流を供給する。

(もっと読む)

シリーズレギュレータ

【課題】直列に接続した複数のトランジスタの耐圧を確実に分散できるシリーズレギュレータを提供することを課題とする。

【解決手段】複数の出力制御用トランジスタ5a,5bを直列に接続したシリーズレギュレータ5であって、複数の出力制御用トランジスタ5a,5bの耐圧を分散させるための分圧を設定する複数の分圧素子5e,5gと、複数の出力制御用トランジスタ5a,5bにそれぞれ設けられ、出力制御用トランジスタ5a,5bのゲート電圧を制御する分圧制御用トランジスタ5j,5kを備えることを特徴とする。

(もっと読む)

インバータ装置およびそれをファンモータの駆動装置に用いた電気掃除機

【課題】安価な構成で高効率、信頼性の高いインバータ装置を実現すること。

【解決手段】インバータ装置は、複数の上下アームから構成されるスイッチング回路とスイッチング回路を駆動する制御手段とを備え、上アーム側スイッチング回路を構成するスイッチング素子が電圧駆動型素子であり、下アーム側スイッチング回路を構成するスイッチング素子が電流駆動型素子であり、上アーム側スイッチング回路に素子を駆動する電源電圧を印加するブートストラップ回路を有することにより、低損失、高速のスイッチング素子での回路コストを低減すると共に、スイッチング素子の駆動制御を最適に行うことにより、インバータ回路損失を低減し効率向上を行うことを目的としている。

(もっと読む)

過電流保護回路、スイッチングレギュレータ、スイッチングアンプ

【課題】被保護回路の動作を阻害することなく、被保護回路を保護できる過電流保護回路を提供する。

【解決手段】被保護回路を過電流から保護する過電流保護回路を、一定の値の定電流Irefを生成する電流生成部6、電源電圧の変化に追従する基準電流を生成するNMOSトランジスタ46、被保護回路において生成された電流と、前記基準電流とを比較する比較器41及びPMOSトランジスタ43、比較の結果に基づいて被保護回路の動作を停止する駆動回路と、によって構成する。

(もっと読む)

141 - 160 / 722

[ Back to top ]