Fターム[5H740BA12]の内容

電力変換一般 (12,896) | 主回路スイッチング素子 (1,744) | トランジスタ (1,563) | 電界効果トランジスタ(FET) (722)

Fターム[5H740BA12]に分類される特許

1 - 20 / 722

インバータ装置及びそれを備えた空気調和機

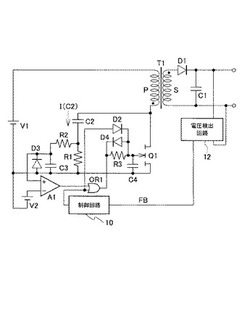

過電圧保護回路

【課題】製造し易い高耐圧素子を使用し、且つ、インピーダンスのバラツキを考慮しなくても良い過電圧保護回路。

【解決手段】制御信号によりスイッチング素子Q1を駆動する駆動部10と、スイッチング素子のドレインとソースとの間に接続され、コンデンサC2と抵抗R1とが直列に接続された微分回路と、抵抗R1の両端に接続され、抵抗R2とコンデンサC3とが直列に接続された積分回路と、コンデンサC3の電圧が基準電圧以上となった場合にドレイン及びソース間の電圧が所定電圧以上になったと判定し、スイッチング素子をオンさせてドレイン及びソース間の電圧をクランプさせる過電圧保護部A1,R3,C4とを備える。

(もっと読む)

半導体スイッチおよび電力変換装置

【課題】主素子の出力静電容量の増大を防止し、接合容量充電電流に起因するターンオン損失を抑制する半導体スイッチを提供する。

【解決手段】逆導通性能を有し、高耐圧な電圧駆動型スイッチング素子である主素子1と、主素子1に比べ耐圧が低い逆流防止素子3と、主素子1の負極と逆流防止素子3の負極とを接続して主素子1の正極を正極端子とし、逆流防止素子3の正極を負極端子とし、正極端子と負極端子間に負極端子から正極端子に向かう方向が順方向となるように接続し、主素子1と同等の耐圧を有する高速還流ダイオード4と、主素子1の正極に正電圧が印加される方向に接続し、少なくとも主素子1の耐圧より低い電圧パルスを発生するとともに主素子1又は逆流防止素子3がオフする時期と略同期して電圧パルスを出力する予備電圧印加回路5と、を備えた半導体スイッチ。

(もっと読む)

過電流検出回路および負荷駆動装置

【課題】回路用電源電圧としてむやみに高い電圧を用いることなく、シャント抵抗の低電位側端子の電圧がグランド電位付近となる異常が原因で生じる過電流を検出する。

【解決手段】検出電流出力部11は、シャント抵抗Rsの各端子電圧を入力し、その入力した電圧から負荷2に流れる電流に応じた検出電流を出力する。過電流判定部12は、検出電流に基づいて負荷2に過電流が流れているか否かを判定する。検出電流出力部11において、通常時に駆動用電源電圧Vdに近い電圧が印加される部分と、回路用電源電圧Vcに近い電圧が印加される部分との間の経路に第1ダイオードD1および第2ダイオードD2を逆方向に介在させることにより、第1トランジスタT1および第2トランジスタT2がブレークダウンして電流が流れることを阻止する。

(もっと読む)

制御回路及び電子機器

【課題】ノーマリーオフ化したGaN−HEMTを電源回路に用いた場合、長期間電源をオフしている間にノーマリーオンに戻るのを防止する制御回路を提供する。

【解決手段】制御回路は、ソース、ゲート及びドレインを有する第1のスイッチング素子と、第2のスイッチング素子を介して前記ゲートに電圧を供給するバッテリーと、第3のスイッチング素子を介して前記ゲートにPWM信号を供給するPWM信号発生回路と、電源がオフの状態で、前記第2のスイッチング素子をオンして前記ゲートに前記バッテリーの電圧を供給すると共に、前記第3のスイッチング素子をオフし、電源がオンの状態で、前記第3のスイッチング素子をオンして前記ゲートに前記PWM信号電圧を供給すると共に、前記第2のスイッチング素子をオフするゲート制御回路とを有する。

(もっと読む)

スイッチング素子の駆動回路

【課題】固定が容易で且つ設置スペースを削減できるようにしたスイッチング素子の駆動回路を提供する。

【解決手段】多層配線板8の下面が主電流経路6上に搭載する搭載面とされているため、その多層配線板8の搭載面を平坦面にすることができる。したがって、主電流配線6は、その上面が平坦な設置面として形成されていれば、単に多層配線板8の搭載面を主電流配線6の上面に配置することで設置できる。これにより、コイルLを容易に固定でき設置スペースを削減できる。

(もっと読む)

半導体装置と、それを用いたインバータ、コンバータおよび電力変換装置

【課題】性能のばらつきが小さな半導体装置を提供する。

【解決手段】この半導体装置は、ノードN1,N2間に直列接続された第1のスイッチング素子(高耐圧のトランジスタQ1)および第2のスイッチング素子(抵抗素子R1および低耐圧のトランジスタQ2)と、第2のスイッチング素子に並列接続された第3のスイッチング素子(低耐圧のトランジスタQ3)とを含む。トランジスタQ2をオンさせるとトランジスタQ1がオンし、さらにトランジスタQ3をオンさせるとノードN1,N2間が導通状態になる。したがって、オン抵抗値の高い第1のスイッチング素子をオンさせて高耐圧のトランジスタQ1をオンさせるので、ターンオン時間のばらつきが小さくなる。

(もっと読む)

スイッチング電源装置

【課題】入力に帰還する同相ノイズが小さく、小型化・高効率化が容易なブリッジレス・ブースト・コンバータ方式のスイッチング電源装置を提供する。

【解決手段】インダクタンスが略等しい第一及び第二昇圧インダクタ12,14と、マイナス端子が制御グランド20に接続された平滑コンデンサ16を備える。制御回路30によってオン・オフされる第一及び第二スイッチング素子22,26、及びそれらと相補的にオン・オフする整流素子24,28を備える。同じ巻数の3巻線を有する入力線インダクタ42を備え、第一巻線48の出力端48bが第一昇圧インダクタ12の入力端12aに接続され、第二巻線50の出力端50bが第二昇圧インダクタ14の入力端14aに接続される。第三巻線52の入力端52aが制御グランド20に接続され、出力端52bが交流遮断コンデンサ44を介して第二昇圧インダクタ14の入力端14aに接続される。

(もっと読む)

トランジスタ保護回路

【課題】スイッチング周波数が高くても、適切にトランジスタの保護を行うことが可能なトランジスタ保護回路を提供する。

【解決手段】本発明の一実施形態に係るトランジスタ保護回路10は、駆動回路30によって電源40の高電位側電圧または低電位側電圧がゲート端子に印加されて、スイッチング制御される電圧駆動型のトランジスタ20の保護を行うためのトランジスタ保護回路である。このトランジスタ保護回路10は、トランジスタ20の保護を実行する保護指令を受けたときに、電源40の高電位側電圧を次第に低下させる電源制御部12を備える。

(もっと読む)

系統連系インバータ

【課題】漏れ電流および高周波ノイズを抑制する小型の系統連系インバータを提供する。

【解決手段】インバータ1と、インバータ1の入力側において直列に接続されたコンデンサによる第1コンデンサ対41と、インバータ1の出力側において直列に接続されたコンデンサによる第2コンデンサ対42と、第1コンデンサ対41の中性点cと第2コンデンサ対42の中性点fとを接続する中性点接続線gと、第1コンデンサ対41と第2コンデンサ対42との間で、且つ、インバータ1の入力側もしくは出力側に配置されインバータ1で発生したコモンモード電流を抑制するコイル3と、インバータ1から出力されるパルス幅変調された電圧を正弦波状の交流に変換するローパスフィルタ構造を構成した出力フィルタ2と、を備え、コイル3は、各相の第1巻線32aおよび第2巻線32bと、第1巻線32aと第2巻線32bとが近接した状態で巻きつけられたコア31と、を備える。

(もっと読む)

駆動回路

【課題】駆動電圧を調整可能な駆動回路を提供すること。

【解決手段】駆動回路10は、チャージポンプ回路部14を備えている。チャージポンプ回路部14は、メインスイッチング素子SW10がターンオンする遷移期間の初期段階において、キャパシタC1に充電された充電電圧に基づいて駆動電源18の電圧Vsを昇圧して駆動電圧Vgprを生成する。チャージポンプ回路部14では、指示信号S1に基づいてキャパシタC1に充電される充電電圧が調整可能に構成されている。

(もっと読む)

ゲート駆動回路

【課題】双方向に導通可能なスイッチング素子に逆電流が流れた場合であってもスイッチング素子の損失を低減できるゲート駆動回路を提供する。

【解決手段】双方向に導通可能なスイッチング素子Q1のゲートに正電圧を印加してオンさせ、ゲートに負電圧を印加してオフさせる駆動部2と、スイッチング素子Q1に逆方向電流が流れる前にゲートへの負電圧の印加を解除する負電圧解除部3とを備える。

(もっと読む)

ゲート駆動回路

【課題】印加可能なゲート電圧の制約条件を満たしながら、高速スイッチングによる低損失特性を満足させるとともに、誤オン動作等のインバータとしての不正動作を阻止することのできるゲート駆動回路を提供する。

【解決手段】SiCで形成された接合型電界効果トランジスタ(JFET)1のゲート側にゲート抵抗(Rg1)3を設け、スイッチ5を介してゲート電源(Vsg)7と接続し、JFET1のゲート・ソース間に、JFET1のドレイン・ゲート間に生じる浮遊容量(Cf1)9よりも大きな容量を有するコンデンサ(Cg)11を設ける。

(もっと読む)

スイッチングシステムおよびスイッチングシステムの制御方法

【課題】EMIを低減できるスイッチングシステムを提供する。

【解決手段】本発明は、スイッチングシステムを提供する。スイッチングシステムは、Hブリッジ、電流ルーターおよび制御回路を含む。Hブリッジは、第一出力ノードに結合される第一スイッチと第二スイッチおよび第二出力ノードに結合される第三スイッチと第四スイッチを含み、ロードは、第一出力ノードと第二出力ノード間に結合される。電流ルーターは、第一出力ノードと第二出力ノード間に結合される第一シャントスイッチと第二シャントスイッチを含む。制御回路は、第一制御信号を生成して、第一スイッチと第四スイッチを制御し、第二制御信号を生成して、第二スイッチと第三スイッチを制御し、第三制御信号を生成して、第一シャントスイッチを制御し、第四制御信号を生成して、第二シャントスイッチを制御する。

(もっと読む)

誘導性負荷駆動装置

【課題】電流回生ルートから電流還流ルートへの切替時におけるホールドコンデンサの電荷抜けを抑制して電流検出精度の向上を実現可能な誘導性負荷駆動装置を提供する。

【解決手段】第1のスイッチング素子と、第2のスイッチング素子と、還流回路と、逆起電流回生回路と、第2のスイッチング素子とアースとの間に介挿されたシャント抵抗とを備えた誘導性負荷駆動回路から誘導性負荷に供給される駆動電流を検出する誘導性負荷駆動装置であって、シャント抵抗の両端に接続された差動増幅器と、第1及び第2のスイッチング素子を制御するプロセッサと差動増幅器の出力端子とを結ぶ配線に介挿されたサンプルスイッチと、プロセッサから第2のスイッチング素子に出力される制御信号がオンレベルに遷移してから所定の遅延時間の経過後にサンプルスイッチをオンにさせる遅延回路とを備える。

(もっと読む)

電力変換器の制御装置および制御方法

【課題】複数のスイッチング素子を含む電力変換器において、動作モードに応じてスイッチング速度を制御することによって、サージ電圧抑制およびスイッチング損失低減の両立を図る。

【解決手段】電力変換器50は、スイッチング素子S1〜S4を独立にオンオフ制御して、直流電源10,20および負荷30の間で電力変換を実行する第1の動作モードと、スイッチング素子S1〜S4のうちの2個ずつを共通にオンオフ制御して、直流電源10または20と負荷30の間で電力変換を実行する第2の動作モードとを有する。スイッチング素子S1〜S4の各々のターンオンおよびターンオフ時におけるスイッチング速度は、動作モードに応じて制御される。具体的には、第2の動作モードにおけるスイッチング速度は、第1の動作モードにおけるスイッチング速度よりも高い。

(もっと読む)

電界効果トランジスタのゲート電位制御回路

【課題】FETのゲートドライブ回路に正負の電源を必要とせず、簡単な受動素子のみの回路で、ゲート電位に正極/負極電位を印加しFETの高速スイッチングドライブを可能とする。

【解決手段】電流路が導通する電位を超える電位1を、電流路の一端を基準電位として、制御端に容量素子を介して断続的に印加されるべく構成され、電位1が印加されたとき、電位1が前記定電圧素子1に対して、電流路が導通に要す定電圧素子1の有する降伏電圧1を発生すべく、かつ電位1が定電圧素子2に対して順方向に、電位1が印加された後、電位1が低下されたとき、電位1により容量素子に充電された電位2が電流路の一端を基準電位とし定電圧素子2に対して、電位1と逆極性の、定電圧素子2の有する降伏電圧2を発生すべく、かつ電位2が定電圧素子1に対して順方向に、定電圧素子1と定電圧素子2の直列接続回路を、制御端と電流路の一端との間に介在させた。

(もっと読む)

誘導性負荷駆動装置

【課題】高速スイッチングに起因するラジオノイズの低減を図ることの可能な誘導性負荷駆動装置を提供する。

【解決手段】電源と誘導性負荷の一端との間に介挿された第1のスイッチング素子と、前記誘導性負荷の他端とアースとの間に介挿された第2のスイッチング素子と、前記第1及び第2のスイッチング素子の両方がオフの時に前記誘導性負荷の他端から出力される逆起電流を前記電源に回生させる逆起電流回生回路と、を備えた誘導性負荷駆動装置において、前記誘導性負荷の両端或いは片端に接続されたノイズ吸収回路を備える。

(もっと読む)

半導体スイッチング回路、及びそれを用いた半導体モジュール並びに電力変換モジュール

【課題】低ゲート消費電力で、高速かつ確実にスイッチング素子をオンオフさせる半導体スイッチング回路、及びそれを用いた半導体モジュール、電力変換モジュールを提供する。

【解決手段】スイッチング素子1,11を有するスイッチング回路20,21において、容量4,14と抵抗5,15との容量抵抗並列接続回路3,13と、ダイオード直列接続回路7,17とこのダイオードと逆方向に並列に接続されたダイオード8,18とを有するダイオード直列並列接続回路6,16とを有し、スイッチング素子1,11のゲート端子には容量抵抗並列接続回路3,13の一端が接続され、この他端とゲート駆動用回路9の出力端子との間には、ダイオード直列接続回路7,17のダイオードのアノード端子をゲート駆動用回路9側、このカソード端子をスイッチング素子1,11のゲート端子側にして、ダイオード直列並列接続回路6,16が接続されている。

(もっと読む)

電力変換装置

【課題】単発的な異常が原因でブートストラップ電圧の低下を一時的に検出した場合に、上アームスイッチング素子の動作停止期間を最短に制御することが可能な電力変換装置を提供する。

【解決手段】電圧監視回路24は、ブートストラップコンデンサ22に充電されているブートストラップ電圧(c)を監視する。電圧監視回路24は、上アームスイッチング素子駆動信号(b)の上アームスイッチング素子11への出力を、ブートストラップ電圧(c)が閾値電圧以上であれば実行し、ブートストラップ電圧(c)が閾値電圧よりも低下すれば停止する。停止期間制御回路25は、電圧監視回路24が上アームスイッチング素子11への上アームスイッチング素子駆動信号(b)の出力を停止する期間を制御する。

(もっと読む)

1 - 20 / 722

[ Back to top ]