Fターム[5H740BA13]の内容

電力変換一般 (12,896) | 主回路スイッチング素子 (1,744) | トランジスタ (1,563) | マルチエミッタトランジスタ (26)

Fターム[5H740BA13]に分類される特許

21 - 26 / 26

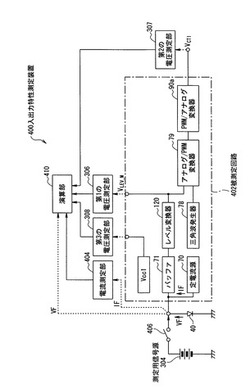

演算増幅器を含むアナログ回路の入出力特性調整方法

【課題】演算増幅器を含むアナログ回路の入出力特性を調整する工数を削減すること。

【解決手段】演算増幅器を含むアナログ回路である被測定回路402の入出力特性を測定し、この結果に応じてゲイン調整値を計算し、次に、この時点ではゲイン調整を行わずゲイン調整後の当該アナログ回路の入出力特性を推定し、この結果に応じてオフセット調整値を計算し、次に、先に計算したゲイン調整値とそのオフセット調整値に応じてゲイン調整とオフセット調整を同時に行う。

(もっと読む)

パワーデバイス短絡検出回路

【課題】パワーデバイスを駆動するドライブ基板内に設け、ドライブ基板につながるパワーデバイスのゲート・エミッタ間電圧の変化を利用して短絡故障を検出することができるパワーデバイス短絡検出回路を得る。

【解決手段】パワーデバイス1と、パワーデバイスを駆動するドライブ基板2に設けられたゲート抵抗4と、パワーデバイスのゲート・エミッタ間に設けられ、必要なゲート電圧の変動を利用してパワーデバイスが短絡故障を起こしたことを検出する短絡検出回路5とを備える。

(もっと読む)

過電流保護回路

【課題】スイッチング素子SWを流れる電流をセンス電圧によって検出することで過電流を検出するに際し、スイッチング素子SWのオン操作直後には過電流を適切に検出することが困難なこと。

【解決手段】センス電圧は、RCフィルタ回路42を介して、過電流用比較器43及び貫通電流用比較器44のそれぞれの非反転入力端子に印加される。これら過電流用比較器43及び貫通電流用比較器44の反転入力端子には、閾値電圧Vref1,Vref2が印加されている。センス電圧が閾値電圧Vref1以上となる継続時間が規定時間Delay1以上となるときや、閾値電圧Vref2以上となる継続時間が規定時間Delay2以上となるときには、スイッチング素子SWを遮断する。規定時間Delay2及び閾値電圧Vref2は、貫通電流用に設定される。

(もっと読む)

電力用半導体装置

【課題】 スイッチング素子のスイッチング動作によって流れる過渡電流により生じうる保護回路の誤動作を防止することができる電力用半導体装置を提供する。

【解決手段】 電力用半導体装置は、直列に接続された2個の半導体スイッチング素子からなる複数の直列回路が並列に接続されてなるブリッジ回路と、ブリッジ回路における下アーム側の対応する半導体スイッチング素子を駆動する各駆動回路部とを備える。各駆動回路部の負側電源入力端と該各駆動回路部に対応する各半導体スイッチング素子の所定の電流出力端とは、それぞれ対応して接続される。各駆動回路部の負側電源入力端は、それぞれ個別の配線パターンを介して、所定の直流電源の負側電極に接続される。

(もっと読む)

電圧駆動素子の駆動方法

【課題】電動機の性能向上のため、所定の短時間のみ電動機側への電流すなわちインバータからの出力電流を大電流化するようなインバータ装置においても、短絡過電流に対してスイッチング素子を保護することができる電圧駆動素子の駆動方法を提供する。

【解決手段】少なくとも2つ以上の電圧駆動型スイッチング素子(Q1、Q2)を直列に接続したアームにおける電圧駆動素子の駆動方法において、インバータの出力電流要求値が所定の電流値以上となった場合に、通電に寄与しない電圧駆動型スイッチング素子のゲート電圧を、通電に寄与する電圧駆動型スイッチング素子のゲート電圧よりも低下させるとともに、通電に寄与しない電圧駆動型スイッチング素子の過電流検知レベルを、通電に寄与する電圧駆動型スイッチング素子の過電流検知レベルよりも低下させる(第1発明)。

(もっと読む)

保護装置

【課題】高速動作により確実にパワー半導体素子を保護するとともに、パワー半導体素子の駆動信号波形への影響が小さい保護装置を提供する

【解決手段】保護装置は、抵抗12およびフォトカプラ13によって実現される。ソース電流ISの電路101に挿入された抵抗は、ソース電流ISに応じた検出電圧ΔVを発生する電流検出手段の一例となっている。検出電圧ΔVは、抵抗12に並列接続されたフォトカプラ13の入力端子対13a−13bに与えられる。フォトカプラ13の出力端子対13c−13dは、FET11の駆動端子対と並列接続される。

(もっと読む)

21 - 26 / 26

[ Back to top ]