Fターム[5H740LL00]の内容

電力変換一般 (12,896) | G−K間回路 (124)

Fターム[5H740LL00]の下位に属するFターム

抵抗(dV/dt用) (37)

コンデンサ(ノイズ除去用) (24)

ダイオード(定電圧素子等) (27)

G−K間を短絡する手段 (28)

Fターム[5H740LL00]に分類される特許

1 - 8 / 8

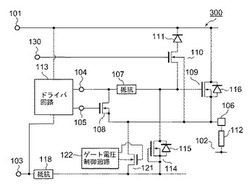

電力供給制御回路

【課題】ターンオフ時に出力端子に発生する逆起電圧に対して、電源の逆接続回路の影響を受けずに過電圧保護回路が正常に動作する電力供給制御回路を提供することである。

【解決手段】第1電源ライン101と出力端子106との間に接続される出力トランジスタ109と、出力端子と第2電源ライン102との間に接続される負荷112と、出力トランジスタ109の制御端子と第1電源ライン101との間に接続され負荷からの逆起電圧に対して導通状態となるスイッチトランジスタ110を含んで構成される過電圧保護回路と、電源が電源ラインに逆方向に接続された場合は出力トランジスタの制御端子に対して電気通路を形成し、一方、正常に接続された場合はその電気通路を負荷からの逆起電圧に対しても遮断状態とする電源逆接続保護回路(114、115、121、122)を備えて構成される。

(もっと読む)

半導体素子の駆動回路

【課題】駆動回路の電源電圧が所定値以上に上昇するまで駆動回路がオン動作しないことと、駆動回路の出力段のトランジスタに貫通電流が流れないようにする。

【解決手段】MOSトランジスタQ1とQ2は縦続接続されている。IC12の出力は、MOSトランジスタQ1のゲートと、ツェナーダイオードZD2を介してMOSトランジスタQ2のゲートに印加されている。IC12の出力電圧がツェナー電圧未満のときは、MOSトランジスタQ2はオフ状態となり、MOSトランジスタQ4のゲートには、抵抗R6を介して電源電圧が印加されるので、駆動回路11の出力段のMOSトランジスタQ4はオン状態となる。

(もっと読む)

ゲート駆動回路

【課題】複数個直列に接続された素子の過電流保護を確実、かつ安全に行ない得るようにする。

【解決手段】複数個直列接続される半導体素子1a〜1cと対応して設けられるゲート駆動回路3a,3b,3cを、絶縁トランス14a〜14cおよび信号線13を介して互いに接続し、いずれかの過電流判定回路8において過電流と判断されたら、当該過電流判定回路8から他のゲート駆動回路へその旨の信号を伝送することにより、他のゲート駆動回路でも過電流保護動作が行なわれるようにする。

(もっと読む)

ソリッドステート・スイッチ用の高効率ドライバ回路

【課題】3端子電圧調整器無しにSCRをターンオンする高効率なソリッドステート・スイッチ用ドライバ回路を提供する。

【解決手段】トリガ回路100は、電源電圧の変動によらず一定の出力DC電流を供給するDC/DC電流モードバック・コンバータを含み、このバック・コンバータはシリコン制御整流器SCR108の制御端子102へ固有の制御要求における変動にかかわらずシリコン制御整流器SCR108がターンオンするための最小電流ILを供給する。

(もっと読む)

半導体素子制御装置

【課題】電源電圧が低下した場合でも、制御対象とする半導体素子を適切に制御することができる半導体素子制御装置を提供する。

【解決手段】電圧付与回路18は、電源電圧Vccを所定の閾値電圧Vthと比較して、Vcc≦Vthであれば、プリドライブ回路2のグランド側端子にグランドレベル近傍の電圧である仮想グランド電圧Vcpを付与し、Vcc>Vthであれば、前記グランド側端子に電源電圧Vccとクランプ制御用電圧Vgsとの差電圧を付与する。

(もっと読む)

電圧駆動型半導体素子のドライブ回路及びインバータ装置

【課題】正電圧の電源のみで、導通損失を増加させることなく、誤点弧を防止する電圧駆動型半導体素子のドライブ回路及びインバータ装置を提供する。

【解決手段】半導体素子を駆動するドライブ回路において、直流電源の正側に接続された第1のスイッチと、第1のスイッチの他端子に接続され、かつ直流電源の負側に接続された第2のスイッチと、直流電源の正側に接続された第3のスイッチと、第3のスイッチの他端子に接続された第4のスイッチと、第4のスイッチの他端子に接続され、かつ直流電源の負側に接続された第5のスイッチと、第1のスイッチの他端子と第4のスイッチの他端子に接続されたコンデンサを備え、半導体素子のゲートは第3のスイッチの他端子に接続され、半導体素子のソースは直流電源の負側に接続する。

【効果】正電圧の電源のみで、半導体素子のゲートに負電圧を印加することが可能となる。

(もっと読む)

電流増幅半導体素子の駆動回路

【課題】 電流増幅半導体のベース電流をコレクタ電流に応じた必要最小限の値に制御するようにし、高速で低消費電力の電流増幅半導体素子の駆動回路を提供する。

【解決手段】 2個の直流電源の正側電源2の正極と負極の間に、チョッピング用スイッチング素子4とインダクタ6と被制御電流増幅半導体1のベース及びエミッタとの直列回路を接続するとともに、チョッピング用スイッチング素子とインダクタの接続点に該接続点側にカソード及び負側電源3の負極にアノードとなるようダイオード8を接続し、被制御電流増幅半導体のベースと負側電源の負極間に制御用スイッチング素子7を接続した回路構成をなし、被制御電流増幅半導体のコレクタ及びエミッタ間の電圧を検出し、被制御電流増幅半導体がオン状態時に、該電圧が準飽和電圧近辺の2値間になるようにチョッピング用スイッチング素子のオンオフ期間を制御する制御回路5を有する電流増幅半導体の駆動回路。

(もっと読む)

電力変換装置

【課題】電力変換装置の各半導体素子の破損を防止する。

【解決手段】制御装置5のゲート接続端子G01と接続点G00間の配線14及びエミッタ接続端子E01と接続点E00間の配線16にコモンモード電流対策部品18を接続するとともに、制御装置5のゲート接続端子G02と接続点G00間の配線15及びエミッタ接続端子E02と接続点E00間の配線17にコモンモード電流対策部品19を接続する。

(もっと読む)

1 - 8 / 8

[ Back to top ]