Fターム[5H740LL03]の内容

Fターム[5H740LL03]に分類される特許

21 - 27 / 27

電子式壁取り付けスイッチ用の電源回路

電子式壁取り付けスイッチ用の電源回路が開示される。開示された本発明は、電子式壁取り付けスイッチ内部の電子回路駆動用の電源回路に係り、スイッチに必要となる十分な電流を供給可能な電子式壁取り付けスイッチ用の電源回路に関する。近年、電子式壁取り付けスイッチの機能が、電灯スイッチ機能に加えて、防犯機能、時計機能、リモコン機能、室内温度調節機能など多様化されており、スイッチ内部の電流需要が数十mA以上に増大されていて、大電流が供給可能な競争力ある電源供給回路が望まれている。また、壁取り付けスイッチ内部の空間が狭くて省スペース特性も求められる。本発明による電子式スイッチ用の電源回路を使用すると、省スペースが可能であり、大電流が供給可能であるだけではなく、コストと品質競争力を兼ね備えていて、結果的に電子式壁取り付けスイッチの競争力を大幅に向上させる効果がある。  (もっと読む)

(もっと読む)

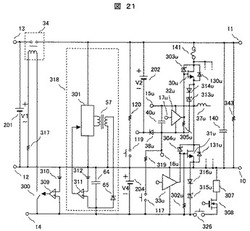

半導体回路

【課題】

ノーマリオン特性を有する半導体素子または、しきい電圧が低いスイッチング素子に好適な半導体回路を提供する。

【解決手段】

本発明の半導体回路は、高圧電源から負電源を充電する手段を設け、高圧端子に電圧を印加するかどうかを制御する高圧スイッチを設け、電力用スイッチング素子用の電源供給が低下したときに高圧スイッチを遮断したり、電力用スイッチング素子の制御回路用が低下しても、高圧端子から制御回路用の電源キャパシタを充電し、制御回路が動作するようにした。さらに、出力端子側からキャパシタに充電されるエネルギーを利用した負電源電圧発生回路を設け、高圧端子と基準電圧端子との間に電圧端子を設け、この電圧端子と複数の出力側端子との間に負電源電圧発生回路を設けた。

(もっと読む)

絶縁ゲート型半導体素子のゲート回路

【課題】 負側電源の故障が発生しても、絶縁ゲート型半導体素子が誤オン動作しないような安全な絶縁ゲート型半導体素子のゲート回路を得る。

【解決手段】 正側電源2Aと負側電源2Bで動作し、絶縁ゲート型半導体素子3のゲート駆動を行うFET12A及びFET12Bから成るトーテムポール回路と、ゲート制御IC11と、ゲート制御ICの出力とFET12Aのゲート間に設けたツェナーダイオード15A及び抵抗14Aから成る直列回路と、ゲート制御ICの出力とFET12Bのゲート間に設けたツェナーダイオード15B及び抵抗14Bから成る直列回路とで構成し、ツェナーダイオード15Aの降伏電圧は、正側電源の電圧からFET12Aのゲートしきい値電圧を減算した値より大きく、ツェナーダイオード15Bの降伏電圧は、負側電源の電圧からFET12Bのゲートしきい値電圧を減算した値より小さく選定する。

(もっと読む)

半導体素子のゲート駆動回路

【課題】 小電流ターンオフ時の過大な短絡電流を確実に防止できる。

【解決手段】 ゲート駆動回路20は、制御信号Saが絶縁器10を介して供給され、ゲート抵抗13,15の接続点がIGBT5aのゲートに接続されている。ゲート制御回路30は、第1の基準値Vref1を設定するための基準電源31と、この第1の基準値Vref1とIGBT5aのゲート電位を比較するコンパレータ回路32と、このコンパレータ回路32の出力とスイッチ素子14をオンオフ制御するスイッチング信号S2との論理積(アンド)演算を行う論理積回路33と、セット端子(S)とリセット端子(R)を持つフリップフロップ34とから構成され、ゲート駆動回路20に対する制御信号Saがオフ指令に切換わった後に、スイッチ素子22をオン状態に切換えて保持するように動作する。

(もっと読む)

過電圧保護回路

【課題】

従来の過電圧保護回路は、ダイナミッククランプ電圧の設定値によっては回路が誤動作を生じる場合があった。

【解決手段】

本発明にかかる過電圧保護回路は、第1の電源101と出力端子106との間に接続される出力トランジスタ109と、出力端子106に接続される負荷112と、前記第1の電源101と出力端子106との間の電圧差を制限するダイナミッククランプ回路111と、ダイナミッククランプ回路111と出力端子106との間に電気的に接続され、基準電圧103と出力端子106の電圧との比較結果に基づいて導通状態が決定されるクランプ切換スイッチ110とを有するものである。

(もっと読む)

スイッチング素子保護回路

【課題】 スイッチング素子を大型化せずに高温動作時におけるスイッチング素子の特性劣化や破壊を防止できるスイッチング素子保護回路を提供する。

【解決手段】 本発明によるスイッチング素子保護回路は、MOS-FET(4)の動作温度を検出する温度検出用サーミスタ(11)と、温度検出用サーミスタ(11)により検出した動作温度が所定のレベルを越えるときに保全信号を発生する比較回路(12)と、過電圧保護回路(10)の検出電圧を設定する2つのアバランシェダイオード(5,6)とMOS-FET(4)の制御端子(G)との間に接続された切換手段(13)を構成するトランジスタ(14)とを備え、比較回路(12)の保全信号が発生したときにトランジスタ(14)をオン状態にして過電圧保護回路(10)の検出電圧を低下させる。これにより、高温動作時のMOS-FET(4)が低下した安全動作領域内での動作に切り換わるので、高温動作時におけるMOS-FET(4)の特性劣化や破壊を防止できる。

(もっと読む)

電力用半導体装置

【課題】 サージを抑制した電力用半導体装置を提供する。

【解決手段】 電力用半導体装置において、直列に接続される1対の高圧側および低圧側の電力用スイッチング半導体素子と、各電力用スイッチング半導体素子に逆接続されたフライホイールダイオードと、電力用スイッチング半導体素子ごとに配置され、入力信号に基づいて当該電力用スイッチング半導体素子のゲートに駆動信号を供給するゲート駆動回路とを備え、さらに、サージの影響を抑制するため、たとえば、低圧側のゲート駆動回路とそのゲート駆動回路に電源電圧を供給する制御電源回路との間にダイオードを挿入する。または、ゲート駆動回路と、入力信号を供給するための入力端子との間にダイオードを挿入する。

(もっと読む)

21 - 27 / 27

[ Back to top ]