Fターム[5H740LL05]の内容

Fターム[5H740LL05]に分類される特許

1 - 20 / 28

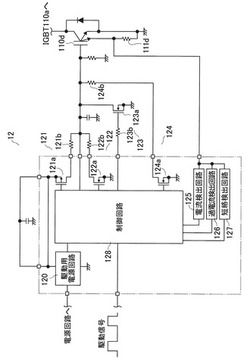

電子装置

【課題】スイッチング素子をオフするように制御しているにもかかわらず、オフできない異常状態を検出し、スイッチング素子の熱破壊を防止することができる電子装置を提供する。

【解決手段】IGBT110dに流れる電流が電流閾値より大きくなると、電流検出回路125は、IGBT110dに電流が流れていると判断する。制御回路128は、駆動信号がIGBT110dのオフを指示しているにもかかわらず、電流検出回路125がIGBT110dに電流が流れていると判断すると、IGBT110dをオフできない異常状態にあると判断する。そして、オフ保持用FET123aをオンする。その結果、IGBT110dのゲートから電荷が放電され、IGBT110dがオフする。そのため、駆動信号がIGBT110dのオフを指示しているにもかかわらず、IGBT110dをオフできない異常状態を検出し、IGBT110dの熱破壊を防止できる。

(もっと読む)

スイッチングデバイスの制御装置

【課題】スイッチングデバイスが過電流の状態ではないが、過電流からの保護に先立ち、スイッチングデバイスの遮断時のサージ電圧を抑制するようにする。

【解決手段】本発明は、電流センサ10と、コンパレータ501と、タイマラッチ502と、制御回路80と、トランジスタ95とを備える。電流センサ10は、スイッチングデバイスQ1の電流を検出し、これに応じた検出電圧ESを出力する。コンパレータ501は、検出電圧ESが基準電圧ER1以上のときに信号を出力する。タイマラッチ502は、その出力信号の継続時間が設定時間以上の場合に、サージ抑制検出信号S3を出力する。制御回路80は、そのサージ抑制検出信号S3を基に、スイッチングデバイスQ1をターンオフさせる駆動信号S12を、トランジスタ95に出力する。基準電圧ER1は、スイッチングデバイスQ1に流れる過電流検出時の基準電圧ER2よりも小さい。

(もっと読む)

モータ駆動装置

【課題】モータ性能を向上するモータ駆動装置を提供することにある。

【解決手段】モータ駆動装置100は、モータを駆動するモータ駆動信号を生成する駆動信号生成部120と、この駆動信号生成部120の前段に設けられ、プルアップ動作時、駆動信号生成部120のスイッチがオン/オフする時発生される電磁波妨害によって引き起こされるモータの振動またはノイズを防止するように、駆動信号生成部120の電流を調節する電流制御部110と、駆動信号生成部120から出力されるモータ駆動信号に基づいてモータを駆動する駆動部130とを含む。

(もっと読む)

トランジスタ駆動回路

【課題】より簡単な構成で、出力トランジスタを確実にオフ状態に維持できるトランジスタ駆動回路を提供する。

【解決手段】NチャネルMOSFET5とコイル2との共通接続点;出力端子OUTとグランドとの間にフライホイールダイオード3を接続する。FET5のゲートには、NPNトランジスタ6及びPNPトランジスタ7のプッシュプル回路により制御信号を出力し、トランジスタ7のベースとグランドとの間にNPNトランジスタ11を接続し、トランジスタ11のベースとグランドとの間にNチャネルMOSFET14を接続して、FET14にPWM信号を入力する。ダイオード13は、FET14がオフ状態になるとトランジスタ11のベースにベース電流を供給し、ダイオード15をダイオード13のアノードとトランジスタ6及び7のベースとの間に接続する。NPNトランジスタ22をFET5のゲートと出力端子との間に接続し、トランジスタ22をPWM信号に応じてFET5がオフする際にオンさせる。

(もっと読む)

ゲートドライブ回路

【課題】ターンオン時のスイッチング特性が変動せず、電力損失を発生せずにスイッチング素子を安定してターンオンさせることができるゲートドライブ回路。

【解決手段】ドレインとソースとゲートとを有し且つワイドバンドギャップ半導体かなるスイッチグ素子Q1のゲートに制御回路からの制御信号を印加することによりスイッチング素子をオンオフ駆動させるゲートドライブ回路であって、制御回路とスイッチング素子のゲートとの間に接続され、第1のコンデンサC1と第1の抵抗R1とからなる並列回路と、スイッチング素子のゲートとソースとの間に接続され、制御信号のオフ信号に対して遅延させてゲートとソースとの間を短絡する短絡手段S4とを備える。

(もっと読む)

ゲートドライブ回路

【課題】簡単な構成で、ワイドバンドギャップ半導体からなるスイッチ素子を駆動するゲートドライブ回路。

【解決手段】ワイドバンドギャップ半導体からなるスイッチ素子Q1であって、ドレインとソースとゲートとを有し、ゲートをドライブする信号とゲートとの間にコンデンサと抵抗の並列接続回路を介して接続され、オフ信号期間は、スイッチ素子Q1のゲート・ソース間を短絡するスイッチSW1とを備えることを特徴とするゲートドライブ回路。

(もっと読む)

スイッチング素子の駆動回路

【課題】定電流用スイッチング素子26や放電用スイッチング素子30に異常が生じると、駆動対象とするスイッチング素子S*#を駆動できないこと。

【解決手段】定電流用スイッチング素子26および放電用スイッチング素子30は、ゲート抵抗体28を介してスイッチング素子S*#のゲートに接続されている。ゲート抵抗体28の両端の電圧は、差動増幅回路70によって出力電圧Vgiに変換され異常判断部72に取り込まれる。異常判断部72では、ゲート抵抗体28に流れる電流に基づき、定電流用スイッチング素子26や放電用スイッチング素子30に異常が生じたか否かを判断する。

(もっと読む)

電子装置

【課題】電流制御用トランジスタ、電流検出用抵抗及びオフ駆動用スイッチング素子の少なくともいずれかの異常を検出できる電子装置を提供する。

【解決手段】制御回路は、正常時のミラー期間Tmの終了時t4におけるIGBT110dのゲート電圧がミラー電圧Vmより高い場合、電流制御用FET121aのショート故障、又は、電流検出用抵抗121bのショート故障が発生していると判断する。具体的には、IGBT110dのゲート電圧の立ち上がり時t2を基準として、所定時間T1経過後のt4におけるIGBT110dのゲート電圧に基づいて異常を検出する。これにより、電流制御用FET121a又は電流検出用抵抗121bの異常を検出するころができる。

(もっと読む)

電力用半導体装置及びその動作方法

【課題】電力用半導体装置がOFF状態の時に電源電圧の急峻な増加が発生した場合であっても、出力トランジスタがONすることを防止する。

【解決手段】本発明の電力用半導体装置は、電源端子と出力端子との間に接続された出力トランジスタと、出力トランジスタのゲートに接続された第1ノードを充放電し、出力トランジスタをON/OFF制御するゲート充放電回路と、第1ノードと出力端子との間に接続されたショートスイッチ回路と、ショートスイッチ回路を制御するショート制御回路と、を備える。ターンオン期間、ON期間及びターンオフ期間において、ショート制御回路は、ショートスイッチ回路を介した第1ノードと出力端子との間の電気的接続を切断する。OFF期間において、ショート制御回路は、ショートスイッチ回路を介して第1ノードと出力端子との間を電気的に接続する。

(もっと読む)

スイッチング素子の駆動装置

【課題】電圧制御形のスイッチング素子S*#の導通制御端子の電圧が正常時におけるシリーズレギュレータ22の出力電圧(ゲート印加電圧VgH)よりも低くなる中間電圧異常に対処できないこと。

【解決手段】ウィンドウコンパレータ70は、ゲート電圧Vgeが、スイッチング素子S*#がオン状態に切り替わる電圧とゲート印加電圧VgHとの間の中間電圧であると判断されることで、論理「H」の信号を出力する。この信号は、ローパスフィルタ72を介して中間電圧異常検出部74に取り込まれる。中間電圧異常検出部74では、ローパスフィルタ72の出力が論理「H」となることで、放電用スイッチング素子30、ソフト遮断用スイッチング素子42およびオフ保持用スイッチング素子60をオン操作して且つ、充電用スイッチング素子24およびシリーズレギュレータ22をオフ状態に切り替える。

(もっと読む)

スイッチング素子の駆動回路

【課題】パワースイッチング素子S#*がオン状態であるときとオフ状態であるときとの双方においてそのゲートの電圧を適切に検出することが困難なこと。

【解決手段】パワースイッチング素子S#*のゲートおよびエミッタ間は、ゲート電圧が低下することをトリガとして、オフ保持用スイッチング素子40によって短絡される。オフ保持用スイッチング素子40は、集積回路(ドライブIC20)によってオン操作される。パワースイッチング素子S#*のゲートに電圧を印加する電源28,30はそれぞれ端子電圧が相違し、ゲート電圧が上昇することで端子電圧の低い電源30から端子電圧の高い電源28へと切り替える。パワースイッチング素子S#*がオフ状態であるときには端子T1の電圧を、また、オン状態であるときには端子T2の電圧を、それぞれゲート電圧として検出する。

(もっと読む)

負荷駆動装置

【課題】従来の負荷駆動装置は、電源が正常に接続された場合の待機時において消費電流が増大するという問題があった。

【解決手段】本発明にかかる負荷駆動装置は、電源端子PWRと出力端子OUTとの間に接続された出力トランジスタT1と、出力端子OUTと接地端子GND1との間に接続される負荷11と、出力トランジスタT1のゲートと接地端子GND2との間に接続され、出力トランジスタT1を非導通にする場合に出力トランジスタT1のゲートと接地端子GND2との間を導通する放電トランジスタMN1と、出力端子OUTと接地端子GND2との間に接続され、接地端子GND2の電位が所定値以上となった場合に導通し、出力トランジスタT1の非導通状態を維持する補償トランジスタMN7と、接地端子GND2と補償トランジスタMN7のバックゲートとの間に接続された第1の抵抗R3と、を備える。

(もっと読む)

負荷駆動装置

【課題】従来の負荷駆動装置は、電源が正常に接続された場合の待機時において消費電流が増大するという問題があった。

【解決手段】本発明にかかる負荷駆動装置は、電源端子PWRと出力端子OUTとの間に接続された出力トランジスタT1と、出力端子OUTと接地端子GNDとの間に接続された負荷11と、出力トランジスタT1のゲートと接地端子GNDとの間に設けられ、電源11の極性が逆になった場合に出力トランジスタT1を導通状態にする保護トランジスタMN3と、電源10の極性が正常の場合に接地端子GNDと保護トランジスタMN3のバックゲートとを導通状態に制御するバックゲート制御回路17と、を備える。

(もっと読む)

電力供給制御回路

【課題】従来の電力供給制御回路は、電源が正常に接続された場合の待機時において消費電流が増大するという問題があった。

【解決手段】本発明にかかる電力供給制御回路は、電源端子PWRと接地端子GNDとの間に設けられた出力トランジスタT1及び負荷11と、出力トランジスタT1のゲートと接地端子GNDとの間に設けられ、電源10の極性が逆になった場合に出力トランジスタT1を導通状態にする保護トランジスタMN8と、出力端子に逆起電圧が印加された場合に出力トランジスタT1を導通状態にする負電圧制御部と、出力端子に逆起電圧が印加された場合に、接地端子GNDと出力端子とを導通状態にする補償トランジスタMN7と、電源10の極性が正常の場合に、接地端子GNDと補償トランジスタMN7及び保護トランジスタMN9のバックゲートとを導通状態に制御するバックゲート制御回路18と、を備える。

(もっと読む)

スイッチング素子駆動装置

【課題】ソフトシャットダウンのための抵抗を別途設ける必要がなく、部品点数を削減でき、コストを抑えることができるスイッチング素子駆動装置を提供する。

【解決手段】IGBT110dのコレクタ電流が過電流状態になると、過電流判定回路122dは、過電流信号を出力する。過電流信号が入力されると、トランジスタ駆動回路122eは、MOSFET122aをオフするとともに、所定時間経過後、MOSFET112cをオンする。MOSFET112cのオン抵抗は、MOSFET122bのオン抵抗とゲート抵抗121との合成抵抗の2倍以上となるように設定されている。そのため、IGBT110dのゲート電圧は、MOSFET122bによってゲート抵抗121を介して放電する場合に比べ緩やかに放電され、ソフトシャットダウンする。従って、ソフトシャットダウンのための抵抗を別途設ける必要がなく、部品点数を削減でき、コストを抑えることができる。

(もっと読む)

半導体素子駆動回路

【課題】半導体素子の種類によらず半導体素子を確実に保護することが可能な半導体素子駆動回路を提供する。

【解決手段】このIGBT駆動回路では、IGBT1のゲート−補助エミッタ間にトランジスタ6を接続し、IGBT1の主電流Iが所定値I1を超えたことに応じてトランジスタ6を導通させ、その所定時間Td1経過後に制御信号VCを「L」レベルにし、トランジスタ6を非導通にするとともにIGBT1のゲートの電荷を抵抗素子20およびトランジスタ17を介して放電させる。したがって、IGBT1のコレクタに発生するサージ電圧VSを小さく抑制できる。

(もっと読む)

スイッチング回路、及びトランジスタの駆動回路

【課題】トランジスタのゲート電位をスレショルド電位未満に維持するための構成を備えるスイッチング回路において、ゲート電位の立ち上がりの遅延を抑制すること等。

【解決手段】電圧制御される主トランジスタと、グランド端子に接続され、前記主トランジスタのゲートスレショルド電圧よりもオン時ドレインーソース間電圧が低い副トランジスタと、第1の抵抗が設けられ、電源装置に接続される端子と前記主トランジスタのゲートとを接続する第1の電力ラインと、前記主トランジスタのゲートから前記副トランジスタへ流れる電流を選択的に許容する第2の電力ラインと、第2の抵抗が設けられ、前記端子と前記副トランジスタとを接続する第3の電力ラインと、を有し、前記第2の抵抗の抵抗値は、前記主トランジスタの容量と前記第1の抵抗の抵抗値の積を前記副トランジスタの容量で除した値よりも小さい値である、スイッチング回路。

(もっと読む)

電力供給制御回路

【課題】ターンオフ時に出力端子に発生する逆起電圧に対して、電源の逆接続回路の影響を受けずに過電圧保護回路が正常に動作する電力供給制御回路を提供することである。

【解決手段】第1電源ライン101と出力端子106との間に接続される出力トランジスタ109と、出力端子と第2電源ライン102との間に接続される負荷112と、出力トランジスタ109の制御端子と第1電源ライン101との間に接続され負荷からの逆起電圧に対して導通状態となるスイッチトランジスタ110を含んで構成される過電圧保護回路と、電源が電源ラインに逆方向に接続された場合は出力トランジスタの制御端子に対して電気通路を形成し、一方、正常に接続された場合はその電気通路を負荷からの逆起電圧に対しても遮断状態とする電源逆接続保護回路(114、115、121、122)を備えて構成される。

(もっと読む)

パワー半導体素子の駆動回路及びパワー半導体素子回路

【課題】パワー半導体素子回路のパワー損失を低減することができるパワー半導体素子の駆動回路を提供する。

【解決手段】ハイレベルの電圧が制御端子に印加されたときにオンになるパワー半導体素子を駆動する回路であって、ドライバーIC2と、ドライバーIC2の出力電圧がハイレベルであるときに、ドライバーIC2の出力電圧よりも高い電圧をnチャネルのパワーMOSFET1のゲート端子に印加する高電圧駆動回路3とを備えることを特徴とするパワー半導体素子の駆動回路。

(もっと読む)

過電流検出回路および半導体装置

【課題】過電流検出において精度の高い温度補償を行う。

【解決手段】制御回路20は、NMOSトランジスタNM0と出力端子OUT間を接続するワイヤ17に流れる負荷電流Iaとワイヤ17の抵抗分とによってワイヤ17の両端に生じる電位差を検出し、電位差が所定値より大きくなった場合に負過電流Iaを制限するようにNMOSトランジスタNM0を制御する。制御回路20は、一端から電流源I1によって電流を順方向に流すと共に他端をワイヤ17の一端に接続するダイオード群21と、一端から電流源I2によって電流を順方向に流すと共に他端をワイヤ17の他端に接続するダイオード群22と、を備え、ワイヤ17の抵抗分の温度変化によって生じる出力電流制限値の変化が少なくなるように、ダイオード群21、22の一端間の電位差に基づいて所定値を補正する。

(もっと読む)

1 - 20 / 28

[ Back to top ]