Fターム[5J001BB24]の内容

Fターム[5J001BB24]に分類される特許

1 - 20 / 64

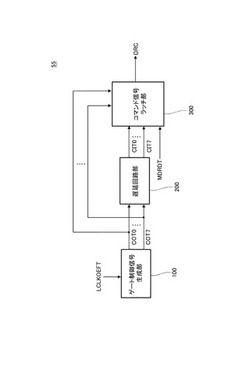

半導体装置及びデータ処理システム

【課題】外部電圧VDDの変動に伴うレイテンシカウンタのラッチマージンの低下を抑制する。

【解決手段】半導体装置は、外部クロック信号に基づいて生成される内部クロック信号LCLKOEFTと、外部から供給されるリードコマンドに応じて生成される内部リードコマンドMDRDTとを受け、内部リードコマンドDRCを生成するレイテンシカウンタ55を備え、レイテンシカウンタ55は、出力ゲート信号COT0〜COT7のそれぞれを遅延させることにより入力ゲート信号CIT0〜CIT7を生成する遅延回路部200を有し、遅延回路部200は、外部電圧VDDで動作する遅延素子と、内部電圧VPERIで動作する遅延素子とを含む。

(もっと読む)

電気短パルス発生装置およびそれを用いた光パルス発生装置

【課題】ジッタが少なく、従来よりも繰返し周波数が低い電気短パルスを発生させることが可能な電気短パルス発生装置およびそれを用いた光パルス発生装置を提供する。

【解決手段】バイアス電圧Vbが重畳された正弦波信号Sを発生させる発振手段と、正弦波信号Sの周波数を分周して、正弦波信号Sの1周期Tの時間幅に等しいパルス幅を有するパルス信号Pを生成する分周手段と、パルス信号Pを所定の遅延量だけ遅延させる遅延手段と、遅延されたパルス信号Pに応じて、正弦波信号Sを透過あるいは遮断することにより、入力パルス信号Piを生成するゲート手段と、入力パルス信号Piのパルス幅を圧縮した出力パルス信号Poを出力する非線形伝送線路と、を備える。

(もっと読む)

信号伝送回路、スキュー補正方法及び画像読取装置

【課題】様々なビットパターンのデータ信号において生じるスキューの進みと遅れのバランスを調整することができる信号伝送回路、スキュー補正方法及び画像読取装置を提供する。

【解決手段】信号伝送回路100は、クロック信号CLK及びデータ信号DATAをパラレルの信号ラインを介して個別に送受信する送信部110及び受信部120とを備え、データ信号DATAが送信される信号ラインには、信号ラインが延長されてなる遅延部125が設けられる。遅延部125の遅延量は、受信したH/Lトグル信号(HとLが交互に繰り返される信号)HLTとクロック信号CLKとの時間差平均に基づいて定められる。遅延部125の遅延量をこのように調整することで様々なビットパターンのデータ信号DATAで生じるスキューの進みと遅れのバランスを調整し、全体的なスキュー補正量を抑制する。

(もっと読む)

位相調整回路及び位相調整方法

【課題】消費電力を低減し、かつ回路面積も小さい位相調整回路を提供すること

【解決手段】位相調整回路100は、複数の遅延素子回路121〜124をリング状に結合したVCO120を有するPLL発振回路100を備える。また位相調整回路100は遅延素子回路を所望の遅延量に応じた数(125〜127)だけ有し、入力信号に前記所望の遅延量を与える位相遅延回路200、210を備える。PLL発振回路100は基準クロックの入力に応じた基準信号に、基準信号の所定周期分の遅延を与えた発振信号をVCO120において生成する。PLL発振回路100は、基準信号と、発振信号に応じた信号と、が略同位相となるように算出された遅延量に応じた遅延制御信号を遅延素子回路121〜124、及び遅延素子回路125〜127の各々に対して入力する。

(もっと読む)

局部発振器

【課題】消費電力を増大させることなく、TDCレスが可能な局部発振器を提供することを目的とする。

【解決手段】発振器制御ワードに応じた発振周波数のN倍の周波数の発振信号を出力するデジタル制御発振器と、前記発振信号をN分周して、2N相のクロックを出力する分周器と、前記クロックを前記参照信号でラッチして、第1位相情報として出力する第1のフリップと、前記参照信号を遅延させて、遅延参照信号として出力する可変遅延回路と、前記クロックを遅延参照信号でラッチして、第2位相情報として出力する第2のフリップフロップと、前記可変遅延回路の遅延量を制御する遅延制御手段と、前記1および第2の位相情報に基づいて、発振器整数位相を出力するデータ変換手段と、発振器整数位相と前記発振器分数位相とを加算し、加算値を第3位相情報として出力する加算器とを備えている。

(もっと読む)

ディレイ回路及び信号遅延方法

【課題】 安定したディレイ時間を有するディレイ回路を提供する。また、面積を小さく占めるディレイ回路を提供する。

【解決手段】 クロック信号を受信して入力信号を順次所定時間の間隔で遅延させて複数の第1ディレイ信号を生成するディレイ部と、一つ以上の選択信号によって前記複数の第1ディレイ信号のうち一つを選択して第2ディレイ信号として出力するオプション部と、を含むディレイ回路を提供する。

(もっと読む)

レジスタ制御ディレイロックループを備えた半導体デバイス

【課題】DLLクロックの無用なトグリングによる電流の消耗を低減することができるレジスタ制御ディレイロックループを備えた半導体デバイスを提供する。

【解決手段】レジスタ制御ディレイロックループから出力されたDLLクロックを用いる内部回路を備えた半導体デバイスにおいて、半導体デバイスに対する作動信号及び非作動信号に応答して、内部回路に印加されるDLLクロックをイネーブルしたりディスエーブルしたりするクロックイネーブル信号を生成する手段を備える。その場合、クロックイネーブル信号を生成する手段は、作動信号又は非作動信号に応答してプルダウン又はプルアップ動作を行う駆動手段と、半導体デバイスに対する作動信号に応答して駆動手段の出力ノードをリセットするリセット手段と、駆動手段の出力ノードに印加された信号をラッチし、バッファリングして出力する出力手段とを備えている。

(もっと読む)

多相クロック間の相間スキュー検出回路、相間スキュー調整回路、および半導体集積回路

【課題】N相クロックの相間スキューの検出を行なうための基準クロックを半導体集積回路内で生成する。

【解決手段】分周回路14は、N相(4相)クロックCLK1/CLK2/CLK3/CLK4をN+1個(6個)の分周クロックA4(−1)/A1(0)/A2(0)/A3(0)/A4(0)/A1(+1)に分周し、位相比較対象クロック生成回路12は、分周クロックA1(0)/A2(0)/A3(0)/A4(0)から位相比較対象クロックB1/B2/B3/B4を生成する。位相比較基準クロック生成回路13は、分周クロックA4(−1)/A1(0)/・・・/A1(+1)から所定の組み合わせと演算規則に従いN個(4個)の基準クロックC1/C2/C3/C4を生成する。そして、位相比較対象クロックB1/B2/B3/B4と基準クロックC1/C2/C3/C4のそれぞれの位相差を検出する。

(もっと読む)

電子機器および画像形成装置

【課題】 画像形成装置などの電子機器において、電源電圧変動、温度変動などの要因で演算回路内の遅延回路による遅延量が動的に変動しても、後段の回路がその影響を受けないようにする。

【解決手段】 この電子機器は、遅延回路を含む演算回路8と、この遅延回路による信号遅延開始時における所定の遅延回路の第1信号進行速度、および演算回路8内の遅延回路による信号遅延開始後のあるタイミングにおける所定の遅延回路の第2信号進行速度を計測する遅延速度測定回路9と、遅延速度測定回路9により計測された第1信号進行速度および第2信号進行速度に基づいて、演算回路8による演算結果を補正する補正回路10とを備える。

(もっと読む)

半導体集積回路

【課題】複数の回路ブロックを有する半導体集積回路にて、電源ノイズにより発生するクロック信号におけるジッタを低減する。

【解決手段】第1の回路ブロックに供給される第1のクロック信号のクロックパスディレイを測定する遅延測定回路と、第2の回路ブロックの動作による電源電圧の変動時間を測定する時間測定回路と、第2の回路ブロックに供給される第2のクロック信号を遅延させる遅延調整回路と、第1のクロック信号と第2のクロック信号との位相差を測定する位相差測定回路と、遅延調整回路での遅延量を制御する位相制御回路とを備え、第2の回路ブロックの動作周波数が第1の回路ブロックの動作周波数より低い場合には、位相制御回路が、ジッタが最小となる電源ノイズと第1のクロック信号との設定位相差を算出し、位相差測定回路により測定した位相差が設定位相差になるように遅延量を制御する。

(もっと読む)

クロックのデューティ・サイクルの自動制御

【課題】クロック信号の立ち下がりを調節して望ましいデューティ・サイクルを達成するデューティ・サイクル補正(DCC)回路を提供する。

【解決手段】幾つかの例では、DCC回路は、入力クロック信号の立ち下がりに応答してパルスを発生し、そのパルスを制御電圧に基づいて遅延し、遅延したパルスに基づいて入力クロック信号の立ち下がりを調節して出力クロック信号を生成し、出力クロック信号のデューティ・サイクルと望ましいデューティ・サイクルとの間の差に基づいて制御電圧を調節する。DCC回路は、望ましいデューティ・サイクルを達成するためにクロック・サイクルの立ち下がりを調節するので、クロック信号の立ち上がりを調節する既存のPLL制御ループへ、その動作に干渉することなく組み込むことができる。

(もっと読む)

位相補償用クロック同期回路

【課題】短時間で精度よく位相調整を行うことが可能な位相補償用クロック同期回路を提供する。

【解決手段】DLLは、入力レシーバ1と、遅延チェーン回路2と、遅延複製器4と、位相比較器5と、リセットパルス発生器6と、粗調整期間発生器7と、分周器8と、単位可変カウンタ9と、を備えている。まず単位可変カウンタ9の増減単位を17または1(平均で16)として粗調整を行って粗くロックさせた後に、単位可変カウンタ9の増減単位を1として微調整を行って細かくロックさせるため、短い期間で確実にクロックINTCKXとクロックEXTCKXの位相を合わせることができる。

(もっと読む)

パルス発生装置

【課題】良好な信号レベルのパルス信号を効率よく発生するのに好適なパルス発生装置を提供する。

【解決手段】パルス発生装置100を、遅延回路10と、バッファー回路20と、パルス発生回路30とを含んだ構成とし、遅延回路10を、M(Mは3以上の整数)個のインバーターI1〜IMを縦続接続した構成とし、バッファー回路20を、遅延回路10の各接続部から出力される遅延信号にそれぞれ対応するM個のバッファーB1〜BMを含み、バッファーB1〜BMによって遅延回路10からの遅延信号をバッファリングする構成とし、パルス発生回路30を、N(Nは1≦N<Mの整数)個の単位パルス発生回路31_1〜31_Nを含んだ構成とし、各単位パルス発生回路において、バッファー回路20を介して入力される複数の遅延信号に基づき、1つのパルス信号を構成する複数の単位パルス信号のうち2以上の単位パルス信号を発生するようにした。

(もっと読む)

半導体集積回路

【課題】主電源とバックアップ電源とを切り換える切換回路を内蔵しないリアルタイムクロック用の半導体集積回路において、バックアップモードにおける消費電力を低減する。

【解決手段】この半導体集積回路は、外部の主電源による第1の電源電圧又は外部のバックアップ電源による第2の電源電圧が選択的に供給されて動作する半導体集積回路であって、第1又は第2の電源電圧に基づいて第3の電源電圧を生成する定電圧回路と、第3の電源電圧が供給されて原振クロック信号を生成する発振回路と、原振クロック信号を分周し、分周されたクロック信号に基づいて計時情報を管理するロジック回路と、第1の電源電圧が供給されているか否かを表す信号に従って、第1の電源電圧が供給されていないときに、定電圧回路から出力される第3の電源電圧の値又は定電圧回路の動作期間を減少させる制御回路とを具備する。

(もっと読む)

三分周直交位相周波数分周器

【解決手段】局部発振器は、VCOの出力に結合されたプログラム可能な周波数分周器を備える。周波数分周器は、3で周波数分周するためにセットされることができる。除数に関係なく、周波数分周器は、90度で位相が互いに異なる直交位相信号(I、Q)を出力する。3で分周するために、周波数分周器は、三分周周波数分周器を備える。三分周周波数分周器は、三分周回路、遅延回路、及びフィードバック回路を備える。三分周回路は、VCOから信号を周波数分周し、それから、120度で位相が互いに異なる三つの信号C、A´、及びBを生成する。遅延回路は、信号A´の遅延バージョンAを生成するために、信号A´を遅延する。フィードバック回路は、遅延バージョンA(I)が、信号C(Q)に関して90度位相がずれるように遅延回路を制御する。 (もっと読む)

半導体集積回路

【課題】クロック信号の位相、デューティー比等の変動に対し耐性の強い、小型の半導体集積回路を提供する。

【解決手段】複数配設される回路部と、クロック信号の立ち上がりエッジから前記クロック信号を逓倍した周期の第1信号を生成する第1カウンタと、前記クロック信号の立ち下がりエッジから前記クロック信号を逓倍した周期の第2信号を生成する第2カウンタと、前記第1信号が転送される第1ラインと、前記第2信号が転送される第2ラインと、前記第1ライン及び前記第2ラインと接続され前記第1信号と前記第2信号との位相差から第3信号を生成し前記回路部に前記第3信号を出力する位相比較器と、を備え、前記位相比較器は、前記第1ライン及び前記第2ライン上に配設され且つ前記第1ライン及び前記第2ラインの末端と前記回路部との間に複数配設される。

(もっと読む)

PLL回路

【課題】面積増大や消費電流増大を伴うことなくPLLロック時の位相オフセット量により生じるクロックの位相ばらつきを極力小さし、またロック後の温度や電源電圧変動へも対応できるようにする。

【解決手段】基準クロックCLK1と帰還クロックCLK2の位相を位相周波数比較器41で比較した結果に応じて出力クロックCLK3の周波数を決定するPLL回路において、出力クロックCLK3がクロックバッファ6を介して入力する分周回路5と分周回路5の出力クロックが入力し帰還クロックCLK2を出力する可変遅延回路9と、その帰還クロックCLK2の位相と基準クロックCLK1の位相を比較する位相比較器8とを備える。可変遅延回路9は、位相比較器8における基準クロックCLK1の位相と帰還クロックCLK2の位相の位相差がキャンセルされるようにその遅延量が制御され、結果としてPLL出力クロックCLK3の位相を調整できる。

(もっと読む)

位相同期ループの出力VCOにおいて50%デューティサイクルを達成するための方法および装置

【課題】PLLの出力において所望のデューティサイクルを達成するための方法および装置を提供する。

【解決手段】本方法は、制限差動増幅器214を使用して、差動コモンモードクロック信号からデューティサイクルを有するシングルエンドクロック信号を発生させるステップと、シングルエンドクロック信号213のデューティサイクルに応じて差動バイアス電流信号229、230を発生させるステップと、差動バイアス電流信号を制限差動増幅器に与えることによって、シングルエンドクロック信号のデューティサイクルを所望のデューティサイクルに修正するステップとを含む。CML−CMOS変換器回路は、制限差動増幅器214と、シングルエンドクロック信号のデューティサイクルの測定値を発生するための低域フィルタと、(i)測定値を基準電圧と比較し、(ii)比較に応じて差動バイアス電流信号を発生するための第2の差動増幅器とを含む。

(もっと読む)

遅延回路

【課題】遅延回路の遅延時間を簡易な構成によって延長する。

【解決手段】映像信号の1走査期間あたり第1パルス数を有する第1のクロック信号を出力するクロック信号出力回路310と、第1のクロック信号が入力され、映像信号の帰線消去期間内における所定周期の間に第1のクロック信号を停止し、1走査期間あたり第1パルス数より少ない第2パルス数を有した第2のクロック信号を出力するクロック信号調整回路330と、第2のクロック信号によってサンプリングされた映像信号を、当該サンプリング開始から第2のクロック信号が第1パルス数分入力されるまでの間、遅延させて出力するサンプルホールド回路101と、を有する遅延回路。

(もっと読む)

移相回路

【課題】入力信号の周波数に依存せずに入力信号に対して所定の位相差を有する出力信号を生成する。

【解決手段】VDDから定電流を供給する定電流回路201aと、入力電流に対してn倍の出力電流を流すカレントミラー回路204a、205aと、矩形波の入力信号1Aaの論理レベルによって定電流回路に流れる電流をカレントミラー回路に流すか、出力端子1Baに流すか切り替えるスイッチ回路202a、203aとを備えた波形生成回路102aにより、立ち上がり勾配1に対してn倍の立ち下がり勾配波形を有する三角波を生成する。これと反転信号1Abを入力した波形生成回路102bにより生成した三角波の電圧をコンパレータ103で比較し出力信号を生成する。入力信号のデューティー比が50%である場合には、1/(2+2n)周期遅延した出力信号が得られる。

(もっと読む)

1 - 20 / 64

[ Back to top ]