Fターム[5J001DD04]の内容

Fターム[5J001DD04]の下位に属するFターム

抵抗又はコンデンサの値を変えるもの (127)

電圧により制御(基準電圧の可変を含む) (114)

出力パルス幅が入力パルス振幅、幅と関連 (14)

複数の制御手段を持つもの (70)

デジタル制御によるもの (469)

Fターム[5J001DD04]に分類される特許

1 - 20 / 75

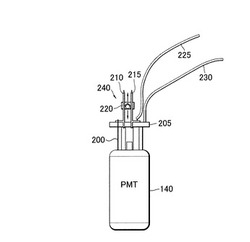

可変遅延デバイス、デバイス調整方法、及びポジトロン放出断層撮影システム

【課題】簡易な構成で時間制御を制御することができる可変遅延デバイス、デバイス調整方法、及びポジトロン放出断層撮影システムを提供する。

【解決手段】可変遅延デバイス240は、飛行時間ガンマ線検出システムの光センサ140に接続され、複数の導電性ピン210、215が搭載された基板205を含む。複数の導電性ピンのうちの第1に接続している第1の端子、及び複数の導電性ピンのうちの第2に接続している第2の端子もまた、基板205に搭載されている。ジャンパ220は、基板205に対して所定の距離で複数の導電性ピンを電気的に接続し、可変遅延デバイス240の時間遅延は、複数の導電性ピン210、215とジャンパ220とによって形成される第1及び第2の端子間の電気経路に基づいて決定される。

(もっと読む)

半導体装置

【課題】電流消費を削減する。

【解決手段】第1のクロック信号(ICLK)を受け、第1のクロック信号を可変である遅延量に応じて遅延させた第2のクロック信号(LCLK)を出力する遅延回路(31)と、第2のクロック信号を受け、遅延された第3のクロック信号(RCLK)を出力するレプリカ回路(32)と、第1および第3のクロック信号の位相差が所定時間以上であるか否かを検知し、所定時間以上である場合には遅延回路の遅延量を変化させ、所定時間未満である場合には遅延回路の遅延量を変化させないように制御する位相差検出回路(36)と、を備える。

(もっと読む)

CMOSインバータ

【課題】 入力波形が急峻な場合でも反転電位を用いずに容易にデューティを補正することができるCMOSインバータを提供する。

【解決手段】 PMOSトランジスタP1と、NMOSトランジスタN1と、入力端子NGと、出力端子NDとを具備し、前記PMOSトランジスタ側もしくは前記NMOSトランジスタ側に接続されたスイッチを有している。前記スイッチがPMOSスイッチP2の場合には前記PMOSトランジスタ側に接続され、前記スイッチがNMOSスイッチの場合には前記NMOSトランジスタ側に接続される。入力端子NGに入力信号を入力した後に、前記スイッチに設けられた制御端子G1に制御信号を前記入力信号とずらして入力することによって前記入力信号の電圧を保持させ出力信号のデューティ補正を行う。

(もっと読む)

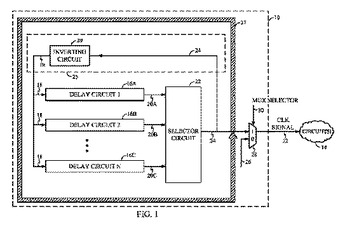

遅延クロック信号生成回路およびパルス生成回路

【課題】遅延経路を切り替えるマルチプレクサの遅延時間をキャンセルした遅延クロック信号生成回路を実現する。

【解決手段】N段直列接続の単位遅延段13からなり初段の単位遅延段13にクロック信号CLK1が入力する遅延回路10と、単位遅延段13のマルチプレクサ12と同一の遅延時間を有するN段直列接続のマルチプレクサ21からなり初段のマルチプレクサ21にクロック信号CLK1が入力する補正回路20と、遅延回路10の出力クロック信号CLKAと補正回路20の出力クロック信号CLKBとの位相差がクロック信号CLK1の1周期に等しくなるように遅延回路10の各単位遅延段13の遅延を制御するDLL制御回路30と、N段直列接続のマルチプレクサ12と同一の遅延時間を有するN段直列接続のマルチプレクサ61からなる調整回路60A、60Bとを備える。

(もっと読む)

遅延回路

【課題】遅延時間の精度を向上するとともに、回路面積の小型化を図る。

【解決手段】入力端子INを介して入力される入力信号に応じてオンオフするトランジスタ10と、トランジスタ10と電源端子VBの間に配置された抵抗20と、トランジスタ10と抵抗20の接続点の電位がハイレベルになるとオフするトランジスタ11と、トランジスタ11と接地端子VSS間に配置された抵抗21と、トランジスタ10と抵抗20の接続点の電圧を出力する出力端子OUTと、トランジスタ11と抵抗21の接続点にアノードが接続され、トランジスタ10と抵抗20の接続点にカソードが接続されたダイオード30と、を備えた。

(もっと読む)

セル・ライブラリから選択された信号スキュー調整セルを備えた集積回路

【課題】 少なくとも1つのデジタル論理セルおよび少なくとも1つのスキュー調整セルを有するデジタル回路機構を備えた集積回路を提供すること。

【解決手段】 スキュー調整セルは、集積回路のデジタル回路機構における信号のスキューを所望の量に調整するように構成される。デジタル論理セルおよびスキュー調整セルはセル・ライブラリから選択される。

(もっと読む)

アキュムレータ型フラクショナルN−PLLシンセサイザおよびその制御方法

【課題】フラクショナル分周器の分周数を周期的に切り替えることに起因するフラクショナルスプリアスを抑制したアキュムレータ型フラクショナルN−PLLおよびその制御方法を実現する。

【解決手段】アキュムレータ型フラクショナルN−PLLシンセサイザ100を、その参照信号入力側の位相検出器の前段にアキュムレータ120からの誤差信号によって上記参照信号に対し位相調整を行う位相調整回路130を介挿して構成し、出力段のVCO114の出力を前段側にフィードバックするフラクショナル分周器115の出力である帰還信号と、上記位相調整された参照信号との両信号の位相差が生じないようにして、該両信号の位相差に応じた出力を得る位相検出器111の出力によってチャージポンプ112が駆動されないようにすることによって、フラクショナル分周器115の分周数を周期的に切り替えることに起因するフラクショナルスプリアスを抑制するように構成する。

(もっと読む)

半導体装置

【課題】切り替えスイッチのオンオフに伴うノイズがバイアスラインに重畳するのを防ぐ。

【解決手段】バイアス電流が流れるバイアスラインVLと、バイアス電流の量を制御信号DDに基づいて切り替える切り替えスイッチ70と、制御信号DDが供給される制御ラインとバイアスラインVLとの間の寄生容量を介して制御信号DDの変化時に生じるバイアスラインVLの電位変動を相殺する相殺回路91〜93とを備える。本発明によれば、切り替えスイッチ70のオンオフに伴ってバイアスラインVLに生じるノイズを相殺することが可能となる。

(もっと読む)

電気短パルス発生装置およびそれを用いた光パルス発生装置

【課題】ジッタが少なく、従来よりも繰返し周波数が低い電気短パルスを発生させることが可能な電気短パルス発生装置およびそれを用いた光パルス発生装置を提供する。

【解決手段】バイアス電圧Vbが重畳された正弦波信号Sを発生させる発振手段と、正弦波信号Sの周波数を分周して、正弦波信号Sの1周期Tの時間幅に等しいパルス幅を有するパルス信号Pを生成する分周手段と、パルス信号Pを所定の遅延量だけ遅延させる遅延手段と、遅延されたパルス信号Pに応じて、正弦波信号Sを透過あるいは遮断することにより、入力パルス信号Piを生成するゲート手段と、入力パルス信号Piのパルス幅を圧縮した出力パルス信号Poを出力する非線形伝送線路と、を備える。

(もっと読む)

クロック発振回路及び半導体装置

【課題】起動時にTDCにキャリブレーション処理を加えることで、時間分解能のばらつきが発生することを防ぎ、合わせて、遅延用の素子の冗長度を減らすことで回路規模の増大を防ぐ手段を提供する。

【解決手段】電源投入時等に多相発振器型TDCであるPDC_c及びバーニア型TDCであるPDC_fのキャリブレーションを実行する。キャリブレーション時にはPDC_fに入力するタイミング入力を参照クロックCLK_REFからDCCOの出力信号のうち一つを選択する。またデータは、先のDCCOの出力信号に隣接し、位相が進んだ出力信号とし、その間の遅延を導出する。これを全出力信号繰り返すことで、DCCOの出力信号1周期を導出する。

(もっと読む)

出力信号制御装置、出力信号制御方法および出力信号制御プログラム

【課題】入力信号を遅延させて出力信号を作成する際に、入力信号の変動が原因で出力信号の遅延が規定値内に納まらない場合であっても、この出力信号によるエラーの発生の抑制が可能な出力信号制御装置、方法およびプログラムを得ること。

【解決手段】位相差許容範囲判別手段12は、位相差測定手段11が測定した出力信号の位相差がこの出力信号を入力する回路で許容範囲内であるかを判別する。出力制御手段13は、許容範囲内でないと判別する状態で出力信号の出力を遮断し、許容範囲内となった段階で出力を開始する。

(もっと読む)

クロックデータリカバリ回路および送受信半導体集積回路

【課題】高速ジッタに追従してクロック再生とデータ再生を可能とする。

【解決手段】クロックデータリカバリ回路1のパルス幅整形回路102はハイとローの期間のデューティ比が略5:5の第1多相クロックCLK’0〜9に応答して、デューティ比が略5−α:5+αの第2多相クロックCLK0〜9を生成する。サンプリング回路106は受信データ信号RXDATAを第2多相クロックでサンプリングして、複数のサンプリング信号を生成する。エッジ検出回路105は複数のエッジ検出信号を生成し、位相選択信号生成回路103は複数の位相選択信号を生成する。クロックデータ生成回路104は、複数のサンプリング信号Sample_Φ0〜9と受信データ信号RXDATAの一方の信号と複数の位相選択信号と第2の多相クロックに応答して、再生クロックRCLKと再生データRDATAを生成する。

(もっと読む)

半導体装置

【課題】回路を通常の動作していない状態からスタンバイ状態に変える、及び、回路全体は通常の動作をしていない状態だがバイアス条件を変える、という具合に条件を変化させることでストレスを緩和する。

【解決手段】スタンバイ制御信号が活性状態のとき、前記タイマー回路からのタイマー出力信号に基づき、機能回路部30の論理状態を所定時間毎に変えるMODE制御信号を生成するモード制御回路20と、機能回路部30の出力信号を受け前記出力信号の出力を制御する出力制御回路50と、を備え、出力制御回路50はMODE制御信号をDelay回路40で遅延させて生成されるDelay出力信号に基づき、機能回路部30がMODE制御信号により論理状態を変えている間、前記機能回路部出力信号を出力に伝達せずに、機能回路部30がMODE制御信号によって前記論理状態を変える直前の機能回路部出力信号を保持出力する。

(もっと読む)

適応クロック発生器、システムおよび方法

機能回路のための、性能マージンを回避し、あるいは小さくするためのクロック信号を生成するために使用することができる適応クロック発生器、システムおよび関連する方法が開示される。特定の実施形態では、クロック発生器は、機能回路内の選択された遅延経路に関連する遅延回路に提供された遅延経路に従って、自律的に、かつ、適合的にクロック信号を生成する。クロック発生器には、入力信号を受け取るように適合され、かつ、出力信号を生成するために、受け取った入力信号を機能回路の遅延経路に関連する量だけ遅延させるように適合された遅延回路が含まれている。遅延回路には、上記出力信号に応答する帰還回路が結合されており、この帰還回路は、遅延回路に発振ループ構成で戻すための入力信号を生成するように適合されている。入力信号を使用して機能回路にクロック信号を提供することができる。  (もっと読む)

(もっと読む)

半導体集積回路

【課題】複数の回路ブロックを有する半導体集積回路にて、電源ノイズにより発生するクロック信号におけるジッタを低減する。

【解決手段】第1の回路ブロックに供給される第1のクロック信号のクロックパスディレイを測定する遅延測定回路と、第2の回路ブロックの動作による電源電圧の変動時間を測定する時間測定回路と、第2の回路ブロックに供給される第2のクロック信号を遅延させる遅延調整回路と、第1のクロック信号と第2のクロック信号との位相差を測定する位相差測定回路と、遅延調整回路での遅延量を制御する位相制御回路とを備え、第2の回路ブロックの動作周波数が第1の回路ブロックの動作周波数より低い場合には、位相制御回路が、ジッタが最小となる電源ノイズと第1のクロック信号との設定位相差を算出し、位相差測定回路により測定した位相差が設定位相差になるように遅延量を制御する。

(もっと読む)

時間デジタル変換器

【課題】時間遅延量の最適値制御が行える時間デジタル変換器を提供すること。

【解決手段】入力されるクロック信号を多段に遅延する複数の遅延段を有し、該複数の遅延段の少なくとも1つが可変遅延段である遅延回路と、前記遅延回路の遅延段と同数個設けられ、参照信号の入力に応答して並列に対応する遅延段の出力を取り込む複数のフリップフロップと、前記複数のフリップフロップの各出力の立ち上がりと立ち下がりの一方または両方を検出するエッジ検出回路と、前記エッジ検出回路が検出したエッジ数をカウントするカウンタ回路と、前記カウンタ回路がカウントしたエッジ数に応じて前記可変遅延段の遅延量を制御する制御回路とを備える。

(もっと読む)

信号の周波数または周期を決定するための方法

【課題】レシプロカルカウンタの分解能を向上させる。

【解決手段】信号をタップ付き遅延線に入力し、遅延線タップの各々の出力位置に複数の遅延線タップ信号を生成する。一実施形態では、信号タイミングエッジを検出し、信号タイミングエッジまたは次のクロックタイミングエッジの位置のタイマクロックサイクルカウントに対応する初期時間値を決定した後で、遅延線タップ信号を監視し、信号タイミングエッジと次のクロックタイミングエッジの間の遅延に対応するようにタイムスタンプを決定するために初期値に対して実施すべき部分補正時間値調整を決定する。

(もっと読む)

遅延ロックループ回路

【課題】基準クロック信号の位相に対して、クロック信号の位相を制御する遅延ロックループ回路であって、回路規模の縮小化及び低消費電力化を図かったアナログDLL回路を提供する。

【解決手段】基準クロック信号の位相と、第1のクロック信号の位相とを比較し、比較結果に応じた信号を出力する位相比較器と、イニシャル信号の入力時において、位相比較器が出力する信号に応じた選択信号を発生する初期位相差検出器と、イニシャル信号の入力時において、初期位相差検出器からの選択信号に応じて、複数の位相が異なる第2のクロック信号の内から、基準クロック信号に最も近接した位相を有する第2のクロックを選択して、第3のクロック信号として出力する初期位相差設定回路と、第3のクロック信号に、位相比較器からの信号に応じた、位相遅延を付加した第1のクロック信号を出力する電圧制御可変遅延線とを備える遅延ロックループ回路を提供する。

(もっと読む)

半導体装置及びその制御方法

【課題】半導体装置の製造ばらつきや経年劣化に起因するクロックスキューを補正することができる半導体装置を提供する。

【解決手段】スキュー検出部6は、スキューを検出するための少なくとも1個のクリティカルパス7又はレーシングパス7を含む。クロック調整部5は、スキュー検出部6により検出されたスキューに基づいて、ディレイの設定値を設定する。クロックセル4は、ディレイの設定値に応じて、第1のクロックのディレイを調整して、第2のクロックとして出力する。

(もっと読む)

位相制御装置、位相制御プリント板、制御方法

【課題】出力信号の位相を微小に制御することを課題とする。

【解決手段】第1の遅延ラインでは、入力信号の入力を受け付けると、信号の位相に対して遅延量を加える遅延器各々によって当該入力信号の位相に対して遅延量を加えるとともに当該遅延器ごとの遅延信号を出力し、DLL回路では、第2の遅延ラインが、外部にて周波数の異なる信号に切り替えることが可能である外部信号の入力を受け付けると、遅延器各々によって当該外部信号の位相に対して遅延量を加え、第2の遅延ラインの複数の遅延器すべてによって遅延された遅延信号と、当該第2の遅延ラインにて遅延量が加えられていない外部信号との位相差を比較し、位相比較器によって比較される遅延信号を外部信号に同期させる電圧であって、当該位相比較器によって出力された位相差から生成された制御電圧を、第1の遅延ラインおよび第2の遅延ラインの複数の遅延器各々に入力する。

(もっと読む)

1 - 20 / 75

[ Back to top ]