Fターム[5J001DD09]の内容

Fターム[5J001DD09]に分類される特許

1 - 20 / 469

データドライバ、表示パネル駆動装置及び表示装置

パルス幅調整回路および方法

パルス幅延長回路および方法

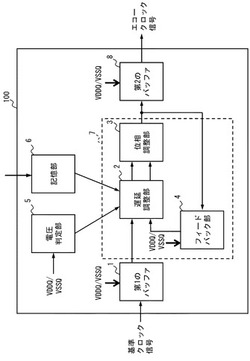

半導体装置

【課題】半導体装置の入出力クロックスキューを抑制する。

【解決手段】I/O電圧電源で駆動される第1のバッファ1及び第2のバッファ8と、I/O電圧電源の電圧レベルを示す電圧判定信号を生成する電圧判定部5と、第1のバッファ1を介して入力された入力クロック信号に基づいて出力クロック信号の位相を調整して第2のバッファへ出力するエコークロック生成部7と、電圧判定信号と位相の調整量との関係を選択するモード情報を記憶する記憶部6と、を有し、エコークロック生成部7は、電圧判定信号とモード情報とに基づいて出力クロック信号の位相の調整量を決定する。

(もっと読む)

PWM出力装置及びモータ駆動装置

【課題】PWM出力幅を細かい単位で正確に制御する。

【解決手段】正相と逆相のPWM信号に対するデッドタイム挿入処理を以下のように行う。PWM信号の出力幅が所定のデッドタイム期間よりも大きく設定された基準期間よりも小さい場合はクリア信号を出力し、大きい場合はセット信号を出力する。セット信号が出力された場合は、PWM信号を補正PWM信号として出力する。クリア信号が出力された場合は、正相のPWM信号をインアクティブとする補正を行って補正PWM信号として出力する。デッドタイム挿入ブロックは補正PWM信号に対して、正相と逆相の信号が同時にオンすることを防ぐようにデッドタイムを挿入する。

(もっと読む)

半導体装置

【課題】アナログ電圧を使用することなく、クロック信号を高精度且つ広範囲に遅延させる。

【解決手段】入力ノード110aと出力ノード110bとの間に直列接続された複数のワンショットパルス生成回路201〜20nを備える。ワンショットパルス生成回路201〜20nのそれぞれは、入力されたクロック信号の一方のエッジに応答して、ワンショットパルスを生成する。ワンショットパルスのパルス幅は、カウント値RCNTに基づいて可変である。これにより、カウント値RCNTを変化させることによって、ディレイライン110の遅延量を広範囲且つ高精度に変化させることが可能となる。しかも、アナログ電圧を使用しないことから、アナログ電圧の生成回路やその安定化回路などを設ける必要もなくなり、回路設計が容易となる。

(もっと読む)

半導体装置

【課題】サンプル間、温度等の変位に伴い発生するロック位相の変動を補正し、ロック位相を一定とすることができるDLLを備えた半導体装置を提供する。

【解決手段】位相検出回路(PD)105を構成する複数のMOSFETのうち所定のMOSFETのバックゲート電位を変更するPDバックゲート電位変更回路106と、温度センサ107と、サンプル別閾値電圧(Vt)情報を記憶したFuse(ヒューズ)108を備える。温度センサ107の温度情報、Fuse(ヒューズ)108に記憶されたサンプル別閾値電圧(Vt)情報は、PDバックゲート電位変更回路106に読み出され、閾値電圧を制御し、ロック位相の変動を補正する。

(もっと読む)

遅延ロックループ回路及びロックアップ方法

【課題】レイアウト面積の増加を抑えつつロックアップ時間の高速化を実現する。

【解決手段】本発明に係る遅延ロックループ回路1は、遅延ライン3と、初期遅延モニタリング部4と、位相比較部5と、遅延制御部6と、ファイン遅延部7とを備え、初期遅延モニタリング部4は、基準クロックと複数の単位遅延部のうちの一部の単位遅延部が出力する単位遅延クロックとの位相を比較する複数の位相比較用フリップフロップを備え、これら位相比較用フリップフロップの数を単位として当該比較を段階的に繰り返すことにより、全範囲について初期遅延モニタリングを行うものである。

(もっと読む)

遅延調整回路、遅延調整方法及び電子機器

【課題】分解能の高い遅延調整回路を提供する。

【解決手段】第1の素子と第2の素子とを有する第1の遅延調整部と、第3の素子を有する第2の遅延調整部と、前記第1の遅延調整部の出力又は前記第2の遅延調整部の出力を選択する出力選択部と、を含み、前記第2の素子の入力及び前記第3の素子の入力は前記第1の素子の出力であり、前記第1の遅延調整部の出力は前記第1の素子の出力及び前記第2の素子の出力であり、前記第2の遅延回路部の出力は前記第3の素子の出力であり、前記第3の素子は、第1の抵抗を介して第1の電源に接続されている第1の状態、及び、前記第1の抵抗を介して前記第1の電源に接続されていない第2の状態があることを特徴とする遅延調整回路。

(もっと読む)

可変遅延回路

【課題】1段ごとの遅延時間変化の誤差が小さい高精度の可変遅延回路の実現。

【解決手段】直列に接続された複数個の遅延ユニット20-0,20-iを有し、各遅延ユニットは、第1から第3論理ゲートを有し、第1論理ゲートG1は、前段の出力が後段の一方の入力になるように直列に接続され、他方の入力には、折り返し位置を指示する第1制御データCTN0,CTNiが入力され、第2論理ゲートG2は、一方の入力が第1論理ゲートの入力に接続され、他方の入力には折り返し位置を指示する第2制御データCT0,CTiが入力され、第3論理ゲートSGは、後段の出力が前段の一方の入力になるように直列に接続され、他方の入力には第2論理ゲートの出力が入力され、第3論理ゲートにおいて、一方の入力M1から出力Zまでの経路の遅延時間と、他方の入力M2から前出力Zまでの経路の遅延時間は、等しい可変遅延回路。

(もっと読む)

半導体装置、及び情報処理装置

【課題】

安定的な動作を確保できる半導体回路装置、及び情報処理装置を提供することを課題とする。

【解決手段】

半導体装置は、入力信号に遅延を与える遅延部と、前記遅延部から出力される出力信号の位相を検出する位相検出部と、前記位相検出部から出力される位相情報に基づき、前記出力信号の位相の安定動作範囲を設定する設定部と、前記安定動作範囲から位相が外れた前記出力信号の検出回数をカウントするカウンタと、前記遅延部の動作条件又は外的要因に応じて、前記カウンタのカウント数のディスカウント数を表すディスカウント信号を生成するディスカウント制御部と、前記カウンタのカウント数と前記ディスカウント信号が表すディスカウント数とに基づき、前記出力信号の位相のエラーの有無を判定するエラー判定部とを含む。

(もっと読む)

サンプリングクロック生成回路、画像読取装置及び電子機器

【課題】アパーチャディレイをより小さくするアパーチャディレイ調整機能を有するサンプリングクロック生成回路を提供する。

【解決手段】SSCG11からの出力クロック信号に対して所定の遅延量だけ遅延してサンプリングクロック信号を発生してサンプリングホールド回路に供給する、遅延回路21,22及びクロック発生器23からなるサンプリングクロック生成手段と、SSCG11の出力クロック信号に基づいて生成されたCCD駆動クロック信号と、上記サンプリングクロック信号とを位相比較して位相比較結果を出力する遅延型フリップフロップ24と、上記位相比較結果に基づいて、上記駆動クロック信号と上記サンプリングクロック信号との位相差が実質的にゼロとなるように上記サンプリングクロック生成手段の遅延量を制御する制御ロジック回路20とを備えた。

(もっと読む)

半導体装置

【課題】入力信号と出力信号の位相差の増大を抑制すること。

【解決手段】本発明の半導体装置は、縦続接続された複数の遅延素子を用いて、入力信号と出力信号の位相を合致させるロック調整動作を行うDLL回路と、リファレンス電位を基準として生成した出力電圧を、複数の遅延素子に供給する遅延素子用電源回路と、出力電圧がリファレンス電位の一定範囲内にあるか否かを検出し、出力電圧が一定範囲内にない場合、ロック調整動作を停止させるDLL動作信号をDLL回路に出力する検出回路と、を有する。

(もっと読む)

半導体集積回路

【課題】 原振クロック信号を通過させる場合の遅延時間と分周クロックを生成する場合の遅延時間を等しくするために、遅延時間の算出や遅延回路の調整を行う必要がない半導体集積回路を提供する。

【解決手段】 外部制御信号SEの論理値に基づいて、クロック信号CLKと外部入力信号SDの何れか一方を選択して内部入力信号S0とし、クロック信号CLKの立ち下がりで内部入力信号S0をラッチして第1内部出力信号S1を生成し、クロック信号CLKの立ち上がりで内部入力信号S0をラッチして第2内部出力信号S2を生成し、クロック信号CLKまたはクロック信号CLKの遅延信号を内部制御信号S3とし、内部制御信号S3の論理値に基づいて、第1内部出力信号S1または第2内部出力信号S2の何れか一方を選択出力し、選択された一方の内部出力信号は、当該選択期間中は信号レベルが変化しない。

(もっと読む)

クロック生成装置及びDLL(DigitalLockedLoop)回路及びクロック生成方法

【課題】回路規模が小さく、また設計が容易な構成にて、高精度なクロックを生成するDLL回路を実現する。

【解決手段】DLL回路は、外部から入力される動作クロックclksと前記動作クロックと周波数が異なるもしくは等しい入力クロックと所望の周波数を表す設定値kから前記動作クロック周波数の前記設定値k分の一の周波数を有する生成クロックclkcを生成するクロック生成部100と、前記生成クロックclkcと外部から入力される参照クロックclkrの位相差を比較し、その位相差を出力する位相比較部200と、前記位相比較部200の出力である位相差から、前記位相差を“0”とするように前記設定値kへ補正をする補正値を生成し、前記設定値kへ補正値を加算する補正部300とを備える。

(もっと読む)

半導体装置

【課題】クロック伝送回路3の電流消費量の増大を抑えつつ、リードデータのジッタを軽減する。

【解決手段】半導体装置10は、アクティブ期間内に内部クロック信号LCLKよりも周期の長い長周期クロック信号を供給し、アクティブ期間に続くリード期間内に内部クロック信号LCLKを供給するクロック出力制御回路73と、クロック出力制御回路73から出力された内部クロック信号LCLK及び長周期クロック信号を伝送するクロック伝送回路3と、データ入出力端子14と、クロック伝送回路3によって伝送された内部クロック信号LCLKに同期して、データ入出力端子14にリードデータを出力する入出力回路64とを備える。

(もっと読む)

TDC装置とTDCのキャリブレーション方法

【課題】遅延素子の遅延時間のばらつきに対してTDCの変換特性を一定とし線形性を実現可能なTDCの提供。

【解決手段】第1の信号DATAを順次遅延させる複数段の遅延素子111〜11Nを有するディレイライン10と、第2の信号CLKに応答して複数段の遅延素子の出力をサンプルする複数のフリップフロップ121〜12Nと、相隣るフリップフロップの出力結果が切り替わるエッジ位置を、第1の信号の第2の信号に対する位相差として検出するエッジ検出器13と、を備え、エッジ位置の検出結果に基づき、バイアス制御用の制御コードICNTを生成するキャリブレーション制御回路15と、制御コードに対応する複数段の遅延素子に対して供給するバイアス発生回路14を備え、第1の信号の周波数範囲に対応した段数の遅延素子に、第1の信号のエッジが位置するように遅延素子111〜11Nの遅延時間の校正を行う。

(もっと読む)

内部クロック周波数制御回路及びこれを利用する半導体装置

【課題】半導体装置の外部から入力されるコマンド(命令)及びアドレスのセットアップ/ホールドマージンを増加させることができる内部クロック周波数制御回路及びこれを利用する半導体装置を提供する。

【解決手段】本発明は、モードレジスタセット制御信号を受信してモードレジスタセット信号を出力するモードレジスタセットと、モードレジスタセット信号がイネーブルされて外部クロックと同一の周波数のデータ処理用クロックの予め設定された周期が経過するとイネーブル信号を生成する遅延部と、イネーブル信号がイネーブルされると外部から入力される同期命令をデコーディングして分周開始信号を生成する分周命令デコーダと、分周開始信号に応答して外部クロックと同一の周波数の選択クロックを出力するか、または、外部クロックより周波数が低いクロックを選択クロックとして出力する分周選択部とを含む。

(もっと読む)

信号伝送回路、スキュー補正方法及び画像読取装置

【課題】様々なビットパターンのデータ信号において生じるスキューの進みと遅れのバランスを調整することができる信号伝送回路、スキュー補正方法及び画像読取装置を提供する。

【解決手段】信号伝送回路100は、クロック信号CLK及びデータ信号DATAをパラレルの信号ラインを介して個別に送受信する送信部110及び受信部120とを備え、データ信号DATAが送信される信号ラインには、信号ラインが延長されてなる遅延部125が設けられる。遅延部125の遅延量は、受信したH/Lトグル信号(HとLが交互に繰り返される信号)HLTとクロック信号CLKとの時間差平均に基づいて定められる。遅延部125の遅延量をこのように調整することで様々なビットパターンのデータ信号DATAで生じるスキューの進みと遅れのバランスを調整し、全体的なスキュー補正量を抑制する。

(もっと読む)

クロック発振回路及び半導体装置

【課題】起動時にTDCにキャリブレーション処理を加えることで、時間分解能のばらつきが発生することを防ぎ、合わせて、遅延用の素子の冗長度を減らすことで回路規模の増大を防ぐ手段を提供する。

【解決手段】電源投入時等に多相発振器型TDCであるPDC_c及びバーニア型TDCであるPDC_fのキャリブレーションを実行する。キャリブレーション時にはPDC_fに入力するタイミング入力を参照クロックCLK_REFからDCCOの出力信号のうち一つを選択する。またデータは、先のDCCOの出力信号に隣接し、位相が進んだ出力信号とし、その間の遅延を導出する。これを全出力信号繰り返すことで、DCCOの出力信号1周期を導出する。

(もっと読む)

1 - 20 / 469

[ Back to top ]