Fターム[5J022AA00]の内容

アナログ←→デジタル変換 (13,545) | A/D変換器の型式 (1,573)

Fターム[5J022AA00]の下位に属するFターム

A/D非特定 (659)

逐次比較型A/D (217)

並列比較型A/D (202)

積分型A/D (277)

上位桁・下位桁分離合成型A/D (205)

Fターム[5J022AA00]に分類される特許

1 - 13 / 13

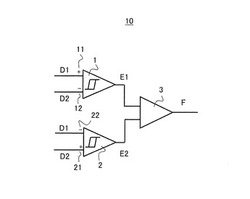

信号変換回路、その信号変換回路を備えるアイソレータ回路及び信号変換方法

【課題】高い周波数の差動信号をシングルエンドの信号に変換可能な信号変換回路、当該信号変換回路を備えたアイソレータ回路及び信号変換方法を提供すること

【解決手段】本発明にかかる信号変換回路10は、差動信号である信号D1及び信号D2が入力されるヒステリシスコンパレータ1、2及び変換バッファ3を備える。ヒステリシスコンパレータ1は、信号D1の電位V1と信号D2の電位V2との大小の比較結果を信号E1として出力する。ヒステリシスコンパレータ2は、電位V1と電位V2との大小を比較し、当該比較結果を信号E1の反転信号である信号E2として出力する。変換バッファ3は、信号E1及び信号E2をシングルエンド信号Fに変換する。

(もっと読む)

A/D変換器とその補正方法

【課題】A/D変換器においてノイズ等の異常値を除去し高精度のA/D変換結果を出力する。

【解決手段】A/D変換器は、奇数回のサンプリングでビット毎に行う多数決に基づきA/D変換結果を補正する多数決回路M4を具備する。多数決回路M4は、第1判定回路M11、M13、第1補正回路M15、M17、第2判定回路M12、M14、第2補正回路M16、M18を備える。第1判定回路はビット毎のサンプリングによるA/D変換結果の“1”出現回数が第1判定値と一致する場合、桁上げ付近且つ桁上げありと判定する。第1補正回路は、判定されたビットより下位ビットのA/D変換結果を“0”に補正する。第2判定回路はビット毎のサンプリングによるA/D変換結果の“1”出現回数が第2判定値と一致する場合、桁上げ付近且つ桁上げなしと判定する。第2補正回路は判定されたビットより下位ビットのA/D変換結果を“1”に補正する。

(もっと読む)

ΔΣADC回路

【課題】消費電力を低減することが可能なΔΣADC回路を提供する。

【解決手段】ΔΣADC回路100に、所定の周期でサンプリングされる入力信号の積分値を出力する積分器103と、前記積分値が基準値を上回った場合にパルス信号を出力するとともに、前記積分値と前記基準値との差分値を積分器103に入力する差分器と、前記差分器からのパルス信号が入力され、当該パルス信号の入力回数をカウントしてカウンタ値として出力するカウンタ回路105と、積分器103への電力供給を停止したときにおける積分器103の積分値およびカウンタ回路105のカウンタ値を保持する積分値・カウンタ値保持部と、を具備し、前記積分値・カウンタ値保持部により保持された前記積分値および前記カウンタ値を、それぞれ積分器103への電力供給を再開したときにおける積分器103の積分値の初期値およびカウンタ回路105のカウンタ値の初期値とする。

(もっと読む)

エンコーダシステム

【課題】小型のロータリーエンコーダで、高分解能かつ耐ノイズ性に優れたエンコーダシステムを提供する。

【解決手段】モータの回転軸に取付けられ、正弦波、余弦波のアナログ電圧信号1aを発生するエンコーダ3からの情報に基づき、モータをサーボアンプ8で駆動するシステムにおいて、アナログ電圧信号1aをディジタル信号に変換するADコンバータ2と、変換されたディジタルデータをシリアルデータとしてサーボアンプ8に伝送するシリアル伝送手段4と、シリアルデータから位置情報あるいは計数情報を出力するデータ処理部7とを備え、データ処理部7に、ディジタルデータに変換された正弦波、余弦波情報を高分解能化する内挿処理手段6を有し、データ処理部7をサーボアンプ8に設ける。

(もっと読む)

半導体集積回路装置

【課題】高精度化と低消費電力化及び小面積を実現したパイプライン型A/D変換回路を備えた半導体集積回路装置を提供する。

【解決手段】シリーズに結合された複数のステージを有するパイプライン型A/D変換回路を有する。上記複数のステージのうち最終段を除く各ステージは、サブA/D変換器でその入力信号を小ビットのデジタル信号に変換する。上記サブA/D変換器のデジタル出力信号をサブD/A変換器でD/A変換を行い、上記入力信号との差信号を減算器で生成し、サンプルホールドアンプで増幅して次段に伝えられるアナログ信号を形成する。上記最終段ステージは、前段のサンプルホールドアンプの出力信号を取り込むサンプルホールド回路と、上記サンプルホールド回路の出力信号と基準電圧とを比較する比較器と、上記比較器の出力信号を保持するラッチ回路とを有する。

(もっと読む)

対数圧縮型アナログ−ディジタル変換回路及び半導体光センサ装置

【課題】広範囲のアナログ入力電流をディジタル出力電圧に変換する温度特性の改善された対数圧縮型アナログ−ディジタル変換回路及び半導体光センサ装置を提供する。

【解決手段】pn接合の順方向特性を利用して入力電流を電圧に対数変換して出力する対数増幅器と、前記対数増幅器の出力電圧に基づくディジタル信号を出力する変換器と、を備え、前記変換器は、温度依存性を有する基準電圧源を用いて発生させた電圧と前記対数増幅器の前記出力電圧とを逐次比較することにより前記対数増幅器が有する温度依存性を抑制しつつ前記対数増幅器の出力電圧に基づくディジタル信号を出力することを特徴とする対数圧縮型アナログ−ディジタル変換回路が提供される。

(もっと読む)

A/D変換装置

【課題】A/D変換装置が外部装置に対してA/D変換処理結果のみを送信している最中にエラーを生じたとしても外部装置側で当該エラーの存在を認識できるようにする。

【解決手段】A/D変換装置は、16ビットの固定通信データ長でA/D変換処理結果をマイコンに対して送信する。A/D変換器は、A/D変換処理中に生じたエラー情報をメモリに保持し、マイコンから送信される準備コマンドに応答するための準備応答信号に付してマイコンに当該エラー情報を送信する(ステップS5)。

(もっと読む)

二値化回路及び二値化方法

【課題】入力信号を二値化するための二値化回路及び二値化方法に関し、ノイズに対して適切な二値化が行なえる二値化回路及び二値化方法を提供することを目的とする。

【解決手段】本発明は、入力信号を二値化する二値化回路であって、入力信号を微分し、全波整流した波形に整形する波形整形回路(111、112)と、波形整形回路(111、112)で整形された信号の最大値をホールドするホールド回路(113)と、ホールド回路(113)にホールドされた最大値に応じて閾値を生成する閾値生成回路(114)と、波形整形回路(111、112)で整形された信号と閾値生成回路(114)で生成された閾値とを比較する比較回路(115)と、比較回路(115)の比較結果に応じて入力信号を二値化した信号を生成する出力回路(116)とを有することを特徴とする。

(もっと読む)

キャリア周波数除去機能付きAD変換回路

【課題】コンパクトな構成でキャリア周波数成分を十分に除去する。

【解決手段】第1信号(S1)とフィードバック信号(S2)を比較する電圧比較器(11)およびフィードバック信号(S2)を出力する電圧フィードバック回路(12)を含むADコンバータ(1)と、フィードバック信号(S2)を入力とする1入力N出力のデマルチプレクサ(2)と、デマルチプレクサ(2)のN個の出力信号を積分するN個の積分器(3)と、N個の積分器(3)の出力信号をそれぞれ入力とするN入力1出力のマルチプレクサ(4)と、アナログ信号Aiとマルチプレクサ(4)の出力信号の差分を出力する減算器(5)と、減算器(5)の出力信号を増幅し第1信号(S1)とする増幅器(6)と、マルチプレクサ(2)の入力切替およびデマルチプレクサ(4)の出力切替をキャリア波に同期して循環的に行わせる切替制御回路(7)とを具備する。

(もっと読む)

集積回路装置、マイクロコンピュータ及び電子機器

【課題】データ解析結果をフィードバックさせてより精度の高い解析処理を可能とする集積回路装置、マイクロコンピュータ、電子機器を提供すること。

【解決手段】本集積回路装置10は、所与のパラメータ70、72、74、76、78に基づき、センサ100から受け取ったアナログ信号60に対して所定の周波数帯域を抽出してデジタル変換を行いデジタル信号を出力するアナログ信号処理回路40と、デジタル信号62に基づき、デジタルデータ列が描く波形の特徴抽出を行う特徴抽出処理手段50と、特徴情報64を受け取り、予め用意されたパラメータ調整用アルゴリズム又はパラメータ調整用テーブルを用いて、アナログ信号処理回路の前記パラメータを調整するためのパラメータ調整値を演算するパラメータ調整値演算手段20、30とを含む。前記アナログ信号処理回路40は、パラメータの調整値に基づき前記所与のパラメータの値をプログラマブルに調整する。

(もっと読む)

再生信号処理装置

【課題】サンプル値系列の量子化分解能を十分に高くすることができ、さらにサンプリングクロックの高速化が可能なPRML方式の再生信号処理装置を実現する。

【解決手段】A/D変換器2として、例えば5値程度の低分解能のものを使用する。これにより高速なA/D変換が可能になって、再生速度を向上させることができる。さらに、補間演算回路4による補間演算により、高い量子化分解能にて再生信号のサンプル系列を得る。このため、ビタビ復号における復号エラー率を十分に低い値に維持することが可能になる。

(もっと読む)

ヒステリシス特性を有するコンパレータ

【課題】ヒステリシスを有するコンパレータを提供すること。

【解決手段】一実施形態においてコンパレータは、入力電圧及び基準電圧を受け取り第1の差動出力を生成する第1の差動入力段と、差動入力を有し第2の差動出力を生成する第2の差動入力段とを有する。コンパレータ段は、第1の差動出力及び第2の差動出力に応答し、コンパレータ出力を生成する。コンパレータはヒステリシス制御回路を更に有し、ヒステリシス制御回路はその構成要素として、1)第2の差動入力段の差動入力間に接続された抵抗器及びヒステリシス調整電圧、2)第1の電圧発生器及び第2の電圧発生器、並びに3)コンパレータ出力の制御により、第1の電流発生器と第2の電流発生器の異なる組み合わせを作動させ、抵抗器を流れる第1の電流又は第2の電流を誘導する、少なくとも1つのスイッチを有する。

(もっと読む)

信号処理装置およびそれを用いた撮像装置

【課題】 正確な利得制御が可能な信号処理装置を提供する。

【解決手段】 オーディオ信号処理装置100において、可変利得増幅器10は、アナログのオーディオ信号SIG12を増幅する。A/D変換器12は、可変利得増幅器10により増幅されたオーディオ信号SIG14をアナログデジタル変換する。利得制御部14はデジタル回路により構成され、A/D変換器12から出力されるデジタルのオーディオ信号SIG16にもとづき、可変利得増幅器10の利得を制御する。

(もっと読む)

1 - 13 / 13

[ Back to top ]