Fターム[5J022CB01]の内容

アナログ←→デジタル変換 (13,545) | 基準電圧・バイアス系 (1,329) | 基準電圧発生回路 (518)

Fターム[5J022CB01]の下位に属するFターム

分圧・レベル調整回路 (222)

Fターム[5J022CB01]に分類される特許

1 - 20 / 296

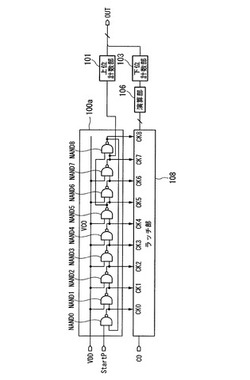

AD変換回路および撮像装置

【課題】エンコードエラーの発生を抑圧することができるAD変換回路および撮像装置を提供する。

【解決手段】VCO100aの出力信号CK0〜CK8のうち出力信号CK7が上位計数部101のカウントクロックとなる。演算部106は、出力信号CK7を基準として定義される出力信号CK0〜CK8の状態(状態0〜状態7)を検出するため、各出力信号の論理状態の変化位置を検出し、検出された変化位置に基づいて下位計数信号を生成する。演算部106がこの変化位置を検出する際の手順では、立下りエッジが略同時になる出力信号CK0と出力信号CK7の論理状態の比較は行われない。このため、エンコードエラーの発生を抑圧することができる。

(もっと読む)

AD変換回路及びAD変換方法

【課題】ビット判定時に比較部での比較時間が長くなることによりAD変換時間が長くなることを抑制する。

【解決手段】アナログ電圧生成部11が、受信したアナログ信号を外部クロック信号Φsに同期してサンプリングし、制御信号に基づいて第1のアナログ電圧及び第2のアナログ電圧を生成し、比較部12がクロック信号Φcに同期して第1のアナログ電圧と第2のアナログ電圧の大きさを比較し、制御部13が第1のアナログ電圧と第2のアナログ電圧の電圧差を縮小させていき、比較部12の比較結果に基づいて、外部クロック信号Φsに同期してサンプリングされたアナログ信号に応じたデジタル信号を生成し、中心電圧調整部15が、クロック信号Φcの信号遷移の回数が閾値以上になると、比較部12の入力トランジスタに流れる電流が増加するように、第1のアナログ電圧と第2のアナログ電圧の中心電圧を調整する。

(もっと読む)

二次電池の状態検知装置、二次電池の状態検知装置のための故障診断方法

【課題】故障診断用の電圧が変動した場合でも、精度良くADコンバータの故障診断を実施する二次電池の状態検知装置を提供する。

【解決手段】二次電池の状態検知のために検出されたアナログ値をデジタル値に変換する複数のADコンバータ(18−20)を備えた二次電池の状態検知装置において、前記複数のADコンバータの故障診断時に、故障診断用電圧を同時に前記複数のADコンバータへ入力するための故障診断用電源(15)と、前記複数のADコンバータの出力値を相互に比較して故障の判定を行う演算部(16)と、を備えた。

(もっと読む)

アナログデジタル回路及びそのアナログデジタル回路を用いた受信機

【課題】アナログ電圧を基準電圧と比較する比較器を有し、その比較器を構成するMOSトランジスタの耐圧をアナログ入力信号の信号振幅の最大電圧より低くすることが可能な逐次変換型アナログデジタル変換器を提供する。

【解決手段】共通ノードに第1端子により接続し、2の巾乗の重み付けがされた複数の第1キャパシタ50a〜50eからなるキャパシタアレイ40と、共通ノードの電圧減衰に寄与する第2キャパシタ70と、それぞれの第1キャパシタに、第1基準電圧、第2基準電圧、又は、入力信号の電圧の内の一つの供給又は切断を行う、複数の第1スイッチからなるスイッチアレイと、共通ノードに第3基準電圧を供給又は切断を行う第2スイッチ30と、共通ノードの電圧を、第3基準電圧と比較する比較器と、第1スイッチ、第2スイッチを制御する制御回路と、を備える。

(もっと読む)

タッチパネルコントローラおよびそれを用いた入力装置、電子機器

【課題】相互キャパシタ方式の入力装置の検出感度を改善し、または、センシング時間を短縮する。

【解決手段】送信回路20は、1回のセンシングごとに送信電極10に複数のパルス信号を含む送信信号S1を印加する。A/Dコンバータ44は、各パルス信号のポジティブエッジごとに、演算増幅器32の出力電圧に応じた検出電圧Vsをデジタル値に変換することにより第1データ系列DRを生成するとともに、各パルス信号のネガティブエッジごとに、検出電圧Vsをデジタル値に変換することにより第2データ系列DFを生成する。DSP102は、第1データ系列DRと第2データ系列DFそれぞれに含まれる、互いに対応するデジタル値の差分を算出し、各デジタル値の差分を積分する。

(もっと読む)

デジタル信号生成回路及びデジタルマイク

【課題】入力信号の温度変化をキャンセルするときの増幅利得の歪み及びバラツキを低減する。

【解決手段】デジタル信号生成回路10は、増幅ユニット12と、基準電圧生成回路142と、変調器140と、を備える。増幅ユニット12は、温度Tに線形依存する信号レベルを有するアナログ入力信号Ainを増幅する。基準電圧生成回路142は、温度Tに線形依存させて基準電圧Vrefを生成する。変調器140は、基準電圧Vrefに基づいて、増幅ユニット12が増幅したアナログ入力信号(増幅信号Ain´)をデジタル出力信号Doutに変換する。

(もっと読む)

AD変換装置およびDC−DC変換装置

【課題】基準となる二つのアナログ信号を必要とせずに、単相差動変換を含むAD変換装置におけるDCオフセットをキャンセルする。

【解決手段】本発明の一態様としてのAD変換装置は、参照電圧信号を受ける第1端子と、前記参照電圧信号を単相差動変換して第1差動信号を得る単相差動変換回路と、前記参照電圧信号に基づき、前記第1差動信号をAD変換して第1デジタル信号を得るAD変換器と、前記第1デジタル信号と、所定コードを表すデジタル信号との差分であるDCオフセットを検出するデジタル回路と、入力信号を受ける第2端子と、を備え、前記単相差動変換回路は、前記入力信号を単相差動変換して第2差動信号を取得し、前記AD変換器は、前記参照電圧信号に基づき、前記第2差動信号をAD変換して第2デジタル信号を取得し、前記デジタル回路は、前記第2デジタル信号から前記DCオフセットを減算してい第3デジタル信号とし、前記第3デジタル信号を出力する。

(もっと読む)

半導体装置、その検査方法および送信回路

【課題】光結合部の伝送マージンを確保して復調誤りを抑制し、高精度の信号伝送を可能とする半導体装置、その検査方法および送信回路を提供する。

【解決手段】半導体装置100は、アナログディジタル変換部3と、ディジタル信号に応じたパルスパターンである伝送信号を出力するパルス幅変調部5と、固定パルスである参照信号を生成する参照信号生成部7と、を備える。そして、前記伝送信号および前記参照信号のいずれかを選択する第1の制御部13と、前記伝送信号または前記参照信号に基づく駆動電流を出力する発光素子駆動部9と、前記伝送信号または前記参照信号基づく光信号を放出する発光素子15と、を備える。さらに、前記光信号を電圧信号に変換する光受信部21と、前記電圧信号を前記伝送信号または前記参照信号に基づくディジタル信号に復調する復調部25と、を備える。

(もっと読む)

2重比較器を利用して、信号フィードバックなしで精密な信号整流およびタイミングシステムを容易にするための方法

【課題】信号整流/タイミング回路用の方法および関連装置を提供する。

【解決手段】可変振幅入力信号12が生成される。上側閾値レベルが決定され、下側閾値レベルが決定される。可変振幅入力信号および上側閾値レベルが第1の比較器22に入力される。可変振幅入力信号および下側閾値レベルが第2の比較器42に入力される。第1のデジタル出力信号23が、ヒステリシス回路を使用して前記第1の比較器において生成され、第2のデジタル出力信号43が、ヒステリシス回路を使用して第2の比較器において生成される。第1のデジタル出力信号および第2のデジタル出力信号が、論理アレイ64に入力される。可変振幅入力信号が、閾値を通過した所でデジタル遷移を有するデジタルレベルパルス出力信号70が、論理アレイにおいて生成される。

(もっと読む)

アナログデジタル変換回路、アナログデジタル変換回路の検査方法、撮像装置、撮像装置を有する撮像システム、撮像装置の検査方法

【課題】複数のメモリ間でのショート故障の有無を検査できる構成を有するADCおよびその検査方法、ADCを有する撮像装置、撮像装置を有する撮像システムを提供する。

【解決手段】複数のメモリと複数の比較器とを含んで構成される回路部を複数有し、アナログ信号をデジタル信号に変換するアナログデジタル変換回路であって、複数の回路部の一部に含まれるメモリと複数の回路部の別の一部に含まれるメモリとで異なるデジタル信号を保持するようにテスト信号を供給するテスト信号供給部と、出力比較部と、転送部を有することを特徴とするアナログデジタル変換回路である。

(もっと読む)

AD変換器、情報処理装置

【課題】動作速度の低下や回路所要面積の増大を抑えつつノイズ増加を防ぐことのできるAD変換器、情報処理装置を提供する。

【解決手段】各々の一端が互いに接続され、それぞれ所定の比率で重み付けされた容量値を有し、容量値を低減可能な可変容量キャパシタを少なくとも1つ含む複数の重み付けキャパシタを有するAD変換器は、複数の重み付けキャパシタの互いに接続された一端が入力と接続された比較器と、複数の重み付けキャパシタの互いに接続された一端と異なる他端それぞれを、入力信号が入力される入力端子、入力信号の逐次比較に用いる参照電圧源、グランドおよび開放端子のいずれか1つと接続する複数のスイッチとを有する。また、このAD変換器は、重み付けキャパシタに入力信号をサンプリングするとともに、比較電圧を生成して処理を実行する逐次比較制御部と、可変容量キャパシタの容量値を低減させる容量制御部とを有する。

(もっと読む)

確率的A/D変換器及び確率的A/D変換器を用いる方法

【課題】高精度で低電力のアナログ−デジタル変換器回路を提供する。

【解決手段】アナログ−デジタル変換器回路は、アナログ入力信号1を受信し、変換ビットの第1のセット3と第1の完了信号7とアナログ入力信号及び変換ビットの第1のセットにより表された信号の間の差を表す残差アナログ出力信号4とを発生する第1の変換器ステージ2と、第1の完了信号を受信しクロック信号を発生するクロック発生回路8と、各々が残差アナログ出力信号及び共通参照電圧を受信するよう構成されクロック信号により動作されて複数の比較器決定を出力する複数の比較器と、複数の比較器決定を受信し変換ビットの第2のセットを発生するデジタル処理ステージとを備える第2の変換器ステージ9と、変換ビットの第1及び第2のセットを組み合わせることにより、アナログ入力信号のデジタル表現を発生する手段とを備える。

(もっと読む)

逐次比較型AD変換方法および装置

【課題】システム全体でのオフセット補償とダイナミックレンジの確保を可能とするAD変換装置を提供する。

【解決手段】ブリッジセンサB1から非測定検出信号が入力するとき、第1のサイクルにおいて、高利得差動増幅器2の基準電圧VCOMとして初期値をセットして、逐次比較型AD変換本体部3でAD変換データを求める。・・・。第m(mは3以上の正の整数)のサイクルにおいて、第m−1のサイクルで得られたAD変換データの最上位ビットに応じて、AD変換データが零値に近づくように、基準電圧VCOMとして、第m−1の電圧を所定電圧だけ上昇又は下降させた第mの電圧をセットする。センサB1から実測定検出信号が入力するとき、基準電圧VCOMとして第mの電圧をセットしてAD変換データを求める。

(もっと読む)

信号入力回路の診断方法および装置

【課題】入力信号の電圧と基準電圧を選択してデジタル値に変換し、このデジタル値から故障箇所を特定する信号入力回路の診断装置では、診断項目を増やすと構成が複雑になり、かつ異常箇所を特定できなかった。本発明は簡単な構成で異常箇所を特定できる診断装置を提供することを目的にする。

【解決手段】マルチプレクサを用いて入力信号電圧、基準電圧、基準電圧を極性反転した電圧、同じ信号の差電圧を測定し、これらの電圧値から異常を診断するようにした。簡単な構成で種々の異常を検出でき、また故障箇所を特定できる。

(もっと読む)

A/D変換回路及びそのテスト方法

【課題】コード変化による容量アレイの電位変化が規格範囲内であるか判定可能なA/D変換回路を提供すること。

【解決手段】本発明にかかるA/D変換回路は、外部からのアナログ信号又はデジタル信号に応じた電位をコンパレータ200の非反転入力端子に供給する容量アレイ201と、第1テストモードの場合に第1デジタル信号を前記容量アレイに供給した後、第2テストモードの場合に第2デジタル信号を容量アレイ201に供給するテスト制御回路306と、第1テストモードから第2テストモードにモードが変化した場合に、コンパレータ200の反転入力端子の電位を所定電圧分変化させる規格電圧発生回路305と、非反転入力端子及び反転入力端子に入力される各電位を比較して比較結果を出力する比較部と、を備え、テスト制御回路306は、第1及び第2テストモードにおけるそれぞれの比較結果に基づいて前記容量アレイの良否判定を行う。

(もっと読む)

アナログデジタル変換器および信号処理システム

【課題】面積の増大を防止でき、かつサンプリングされるコース用ADCとファイン用ADC間のアナログ信号に誤差が生じることを抑止できるAD変換器および信号処理システムを提供する。

【解決手段】アナログ入力信号をNビットのデジタル信号に変換する際に、上位mビットのデジタル信号に変換するコース(Coarse)AD変換器と、コースAD変換器の変換結果に基づきアナログ入力信号の下位nビット(n=N-m)のデジタル信号に変換するファイン(Fine)AD変換器と、アナログ入力信号をサンプリングし、コース用参照電圧との比較電圧をコースAD変換器に供給し、ファインAD変換器の変換結果に応じたファイン用参照電圧との比較電圧を上記ファインAD変換器に供給するTH回路と、を含み、TH回路は、アナログ入力信号、コース用参照電圧、ファイン用参照電圧の選択的入力経路でサンプリング容量を共有する。

(もっと読む)

フラッシュアナログ−デジタルコンバータ、方法及びシステム

【課題】動作中にバックグラウンドにおいてオフセット補償のための較正を行うことができるフラッシュアナログ−デジタルコンバータ(ADC)等を提供する。

【解決手段】フラッシュADCのコンパレータは、バックグラウンドにおいて、コンパレータをフィードバックループへ切り替え、コンパレータの現在の基準レベルを決定し、コンパレータの基準レベルを目標基準電圧へと調整するようコンパレータに結合されている基準キャパシタを充電することによって、較正される。

(もっと読む)

ディジタル保護制御装置

【課題】A/D変換手段を複数備えて並列処理を実行するときに、アナログ信号処理回路のオフセット誤差、ゲイン誤差を補正する。

【解決手段】電力系統から得たアナログ信号をフィルタリングする複数のアナログフィルタ手段と、該手段の後段に設けられアナログフィルタリングされた信号をディジタル信号に変換する複数のA/D変換手段と、A/D変換手段からのディジタル信号をフィルタリングする複数のディジタルフィルタ手段とを備え、ディジタルフィルタ手段からのディジタル信号を用いて所定の保護継電演算アルゴリズムを実行するディジタル保護制御装置において、アナログフィルタ手段の前段に既知の大きさの直流信号を加え、A/D変換手段からのディジタル信号に含まれる直流信号成分を抽出し、既知の大きさの直流信号と抽出した直流信号成分の値を用いて複数備えたA/D変換手段の出力を補正する機能を備えた。

(もっと読む)

アナログ信号の入力装置及びその入力診断方法

【課題】多チャンネルのアナログ信号の診断処理を高速に実行するアナログ信号の入力装置及びその入力診断方法を提供する。

【解決手段】アナログ信号の入力装置10は、外部入力したアナログ信号A及び発生させた基準電圧Eのうちいずれかを出力するマルチプレクサ23と、マルチプレクサ23が出力した信号をデジタル変換するA/D変換部25と、マルチプレクサ23及びA/D変換部25が設けられている複数のチャンネル12と、各々のチャンネル12においてデジタル変換された複数の基準電圧Fから最悪値Fbadを抽出する信号抽出部13と、複数のチャンネル12及び信号抽出部13が設けられているセグメント11と、複数のセグメント11の各々から出力される複数の最悪値Fbadを閾値Gと対比して各々のセグメント11を単位にアナログ信号Aの入力診断をする診断部14と、を備えている。

(もっと読む)

AD変換回路、光電変換装置、撮像システム、およびAD変換回路の駆動方法

【課題】より簡単な回路構成で高分解能な変換が実現できるAD変換回路を提供する。

【解決手段】参照信号とアナログ信号とを比較する比較部107と、増幅部106と、を有し、1段階目のAD変換によってi−bit(i≧2の整数)のデジタルコードを得、2段階目のAD変換によってj−bit(j≧2の整数)のデジタルコードを得ることで、前記アナログ信号を(i+j)−bitのデジタル信号に変換するAD変換回路であって、該AD変換回路は、前記1段階目のAD変換において、前記比較部で前記アナログ信号と前記参照信号との比較を行い、前記増幅部は、前記アナログ信号と、前記i−bitのデジタルコードに対応するアナログ信号と、の差分を増幅した増幅残差信号を出力し、前記2段階目のAD変換において、前記増幅残差信号を前記参照信号と前記比較部で比較する。

(もっと読む)

1 - 20 / 296

[ Back to top ]