Fターム[5J022CF00]の内容

アナログ←→デジタル変換 (13,545) | 周辺・部分回路構成 (2,714)

Fターム[5J022CF00]の下位に属するFターム

比較器(一致回路) (728)

増幅器(差動・演算) (534)

積分器(ランプ電圧発生) (152)

電流源 (217)

インピーダンス変換(電流・電圧変換) (72)

交流←→直流変換(整流) (5)

スイッチング回路 (649)

表示 (117)

信号検出トランスジューサ (238)

Fターム[5J022CF00]に分類される特許

1 - 2 / 2

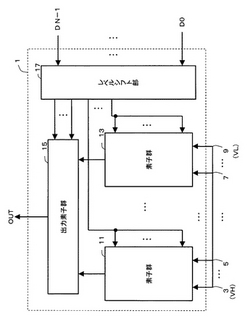

半導体装置及びレベルシフト回路

【課題】 多ビット化でもチップサイズの増大を抑える半導体装置を提供する。

【解決手段】 電位VHと電位VLの間に生じる電圧が分圧され、入力信号D0〜DN−1に基づいて分圧により生じた複数の電位3〜9のいずれかを出力可能な高耐圧デジタル/アナログ変換器1は、複数の素子群11,13と、出力素子群15と、入力信号の電位を出力素子群15と複数の素子群11,13のそれぞれが動作するために必要な電位にレベルシフトして印加するレベルシフト部17を備え、複数の電位3〜9が電位レベル順に複数にグループ化され、複数の素子群11,13のそれぞれは各グループに対応して設けられて対応するグループの電位間の電圧が印加されて動作して入力信号に基づいて対応するグループ内の電位のいずれかを出力し、出力素子群15はVHとVLの間の電圧が印加されて動作して入力信号に基づいて複数の素子群11,13が出力可能な電位のいずれかを出力する。

(もっと読む)

AD変換方法

【課題】 分解能が低いAD変換回路を用いる場合であっても分解能が高いデジタル信号を得ることができる方法を、AD変換回路のレンジ内での変換が可能であって、且つ安価で小規模な構成で実現できるAD変換方法を提供する。

【解決手段】 アナログ信号を予め決められた所定の分解能で複数の出力電圧値から成るデジタル信号に変換するAD変換回路20を用い、複数の出力電圧値の各間隔よりも小さい振幅を有するアナログ信号をデジタル信号に変換するAD変換方法において、アナログ信号に所定の電圧値を有するオフセット電圧を印加することによって、アナログ信号の電圧値を、AD変換回路20の所定の分解能に基づくデジタル信号の複数の出力電圧のうちのいずれかの出力電圧値に接近させた後、所定のオフセット電圧が印加されたアナログ信号をAD変換回路20によってデジタル信号に変換する。

(もっと読む)

1 - 2 / 2

[ Back to top ]