Fターム[5J022CF02]の内容

アナログ←→デジタル変換 (13,545) | 周辺・部分回路構成 (2,714) | 増幅器(差動・演算) (534)

Fターム[5J022CF02]に分類される特許

1 - 20 / 534

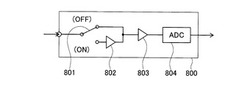

レベル調整装置、およびレベル調整のためのプログラム

【課題】ユーザに負担をかけることなく、容易にアナログ音響信号の音質劣化を抑制することが可能なレベル調整装置を提供すること。

【解決手段】入力ポートはアナログ入力ブロック800を有し、アナログ入力ブロック800は、迂回スイッチ801、固定ゲインにて信号レベルの減衰を行うパッド802、可変ゲインにて信号レベルを増幅又は減衰して調整するアンプ803を備える。迂回スイッチ801はパッド802とアンプ803により信号レベルが調整されるパッドオン状態とアンプ803のみで信号レベルが調整されるパッドオフ状態を切り替えられる。信号レベルの調整の後に、パッドオン状態で、かつパッドのオン・オフの何れの状態でもゲインの調整が可能な重複範囲ROVの範囲内である入力ポートを抽出し、該当する入力ポートのアナログ入力ブロック800に対して、パッドオフ状態への切り替え調整処理を行う。

(もっと読む)

A/D変換装置および固体撮像装置

【課題】電圧分解能を低下させることなく、高速化することができるA/D変換装置および固体撮像装置を提供する。

【解決手段】所定のアナログ・デジタル変換期間をTsとしたとき、(1−1/n)Ts(n:正の整数、n≧2)より短い第1のサンプリング期間と、(1/n)Tsの第2のサンプリング期間とを設定し、アナログ信号を出力して第1のサンプリングを行わせ、該アナログ信号をn倍に増幅し、デジタルオフセット信号で選択されたアナログオフセット信号を加えた増幅アナログ信号を出力して第2のサンプリングを行わせるA/D制御回路と、第1のサンプリング結果から第1のデジタル信号とデジタルオフセット信号とを生成し、第2のサンプリング結果から第2のデジタル信号を生成し、デジタルオフセット信号と第2のデジタル信号とに基づいて、期間Tsに対応した第3のデジタル信号を生成して出力するデジタル生成回路と、を備える。

(もっと読む)

AD変換回路及びその補正方法

【課題】精度の高いAD変換を行うことがが可能なAD変換回路を提供すること。

【解決手段】本発明にかかるAD変換回路は、プリアンプ11,12と、コンパレータ21,22,24と、スイッチ31,41と、トランジスタTr1,Tr5と、スイッチ41をオンした場合におけるコンパレータ21の比較結果に基づいてコンパレータ21のオフセット電圧を補正する第1補正部と、スイッチ31をオンし、スイッチ41及びトランジスタTr1,Tr5をそれぞれオフした場合におけるコンパレータ21の比較結果に基づいてプリアンプ11のオフセット電圧を補正する第2補正部と、を備える。

(もっと読む)

タイムインタリーブ型サンプラのアレイを有する無線周波数(RF)サンプリング装置およびシナリオベースの動的資源割り当てのための方法

【課題】RFサンプリングシステムの動的資源割り当てのための方法および装置を提供すること。

【解決手段】

受信した無線周波数(RF)信号から、タイムインタリーブされた複数のサンプルを生成し、そのタイムインタリーブされた複数のサンプルを組み合わせて信号品質を生成することにより決定された信号品質測定値に基づいた、RFサンプリングシステムの動的資源割り当てのための方法および装置。

(もっと読む)

マルチビット遂次比較型ADC

【課題】いくつかの逐次比較サイクルでサイクル当たり1つよりも多いビットに変換するアナログ/デジタル変換器(ADC)を提供する。

【解決手段】システムは、容量性サブDAC回路410及び比較器430を含み、スイッチS2は、1つ又はそれよりも多くの最初のサイクル中に容量性サブDAC回路を隔離し、かつ1つ又はそれよりも多くの最終サイクル中にサブDAC回路を融合し、逐次比較型レジスタ(SAR)440は、デジタル出力信号又はDACデジタル信号を発生させる。また、システムは、DAC回路を含み、アナログ入力信号及びDACアナログ信号のうちの少なくとも一方で入力キャパシタCinを予充電し、プログラマブル利得増幅器420は、誤差信号を増幅し、マルチビットADCは、増幅された誤差信号をマルチビットデジタル信号に変換し、SARは、マルチビットデジタル信号を使用してDACデジタル信号又はデジタル出力信号を発生させる。

(もっと読む)

半導体装置

【課題】受信特性に悪影響を及ぼすことなく、受信動作中にバックグランドキャリブレーションを実施可能とする半導体装置を提供する。

【解決手段】受信動作中に、利得や受信チャンネルの切り替えに伴って無効な受信信号が発生するタイミングを検出して、このタイミングに合わせてバックグランドキャリブレーションを行う。このとき、受信信号はもともと無効なのでキャリブレーションに伴うさらなる受信精度の悪化は表面化しない。また、バックグランドキャリブレーションを一定の周期で行う際に発生する不要信号成分も、バックグランドキャリブレーションをランダムなタイミングで行えば発生しない。

(もっと読む)

比較器、AD変換器、固体撮像装置、およびカメラシステム

【課題】一層のノイズ低減を図ることができることはもとより、低周波ノイズの低減を図ることができる比較器、AD変換器、固体撮像装置、およびカメラシステムを提供する。

【解決手段】比較器500Aは、第1の入力サンプリング容量C511と、第2の入力サンプリング容量C512と、出力ノードdと、一方の入力端子に、第1の入力サンプリング容量を介して、信号レベルが傾きをもって変化するスロープ信号を受け、他方の入力端子に、第2の入力サンプリング容量を介して入力信号を受けて、スロープ信号と入力信号との比較動作を行う差動比較部としてのトランスコンダクタンス(Gm)アンプ511と、Gmアンプの出力部cと出力ノードdとの間に配置され、Gmアンプの出力部の電圧を一定に保持するアイソレータ530とを有する。

(もっと読む)

増幅回路およびA/D変換器

【課題】最小限の構成を用いて、演算増幅器の入出力端子間の寄生容量に起因する増幅回路の演算誤差を補償し、高精度の増幅率を得る。

【解決手段】増幅回路10は、一方の端子が演算増幅器A1の反転入力端子に、他方の端子が演算増幅器A1の反転出力端子に接続された容量CP5と、一方の端子が演算増幅器A1の非反転入力端子に、他方の端子が演算増幅器A1の非反転出力端子に接続された容量CN5とを備えている。

(もっと読む)

固体撮像装置

【課題】ランプ信号の生成に容量帰還型アンプを用いても、良好なAD変換精度でAD変換を行うことができる固体撮像装置を提供することを課題とする。

【解決手段】2次元状に配列された複数の画素と、列毎に配置され画素からの信号を増幅する増幅回路と、ランプ信号を生成する参照信号発生回路と、ランプ信号及び増幅回路からの出力を用いて、画素からの信号をAD変換するAD変換回路とを備え、増幅回路が有する容量帰還型アンプ及び参照信号発生回路が有する容量帰還型アンプにて同じ構造の帰還容量を用い、かつ帰還容量と増幅器との接続関係を同じにするようにして、増幅回路及び参照信号発生回路のそれぞれの帰還容量のキャパシタンスの電圧依存性を等しくし、AD変換精度を向上させる。

(もっと読む)

アナログ入力回路またはアナログ/ディジタル変換装置

【課題】制御電源のON、OFFの状態に関係なく、また外部に放電用機材が無くてもフィルタ回路、フライングキャパシタ回路内コンデンサの放電を短時間で可能にするためのアナログ入力回路またはアナログ/ディジタル変換装置を提供する。

【解決手段】縦列接続されたフィルタ回路とフライングキャパシタ回路を複数組備え、複数組のフライングキャパシタ回路の後段を増幅器の入力端子に共通に接続し、増幅器の後段にアナログ/ディジタル変換器を備えるとともに、外部制御電源に接続された基板上に構成されたアナログ/ディジタル変換装置において、フィルタ回路とフライングキャパシタ回路は、並列コンデンサとこれに並列に接続された抵抗と常閉接点の直列回路とを備えており、常閉接点は、制御電源の端子間に接続され、制御用接点を介して励磁される補助リレーにより駆動されているアナログ/ディジタル変換装置。

(もっと読む)

A/D変換器

【課題】 キャパシタの誤差の影響を少なくし、A/D変換器の精度を高める。

【解決手段】 アナログ信号更新部100は、キャパシタC1PおよびC1Nが差動増幅器150の入力側に入力キャパシタとして接続され、キャパシタC2PおよびC2Nが差動増幅器150の入出力間に帰還キャパシタとして接続された第1の状態またはキャパシタC2PおよびC2Nが差動増幅器150に入力キャパシタとして接続され、キャパシタC1PおよびC1Nが差動増幅器150に帰還キャパシタとして接続された第2の状態に切り換え可能である。制御部400は、A/D変換サイクル単位で、A/D変換のための係数乗算処理時のアナログ信号更新部100を交互に第1の状態とし、または第2の状態とする切り換えを行う。平均化部502は、所定回数に亙るA/D変換結果が得られる毎に、A/D変換結果を平均化して出力する。

(もっと読む)

A/D変換器

【課題】 差動信号のA/D変換を行うA/D変換器においてチャージインジェクションやクロックフィードスルーに起因したA/D変換の誤差を少なくする。

【解決手段】 各A/D変換サイクルにおいて、正相アナログ入力部50Pおよび逆相アナログ入力部50Nは、正相アナログ入力信号INPおよび逆相アナログ入力信号INNをサンプリングし、正相アナログ入力信号INPを正相入力ノードC1PBまたは逆相入力ノードC1NBに、逆相アナログ入力信号INNを逆相入力ノードC1NBまたは正相入力ノードC1PBに供給する。制御部400は、このサンプリングした各信号の供給先をA/D変換サイクル単位で切り換える。A/D変換器では、正相入力ノードC1PBおよび逆相入力ノードC1NB間の電圧のA/D変換が行われる。平均化部502は、所定回数に亙るA/D変換結果が得られる毎に、A/D変換結果を平均化して出力する。

(もっと読む)

液晶表示装置の駆動装置

【課題】オフセットの影響、回路規模の増大、フリッカ等を抑制し、画質の向上に好適なドライバの提供。

【解決手段】切換制御信号が第1の論理値のとき、第1、第3の電圧が第1、第3の差動段に、第2、第4の電圧が第2、第4の差動段に入力され、第1、第3の差動段の出力が第1、第3の出力段の入力に、第2、第4の差動段の出力が第2、第4の出力段の入力にそれぞれ接続され、ガンマ抵抗1両端には第1、第2の電圧が、ガンマ抵抗2両端には第3、第4の電圧が印加され、切換制御信号が第2の論理値のとき、第1、第3の電圧が第3、第1の差動段に、第2、第4の電圧が第4、第2の差動段に入力され、第3、第1の差動段の出力が第1、第3の出力段の入力に、第4、第2の差動段の出力が第2、第4の出力段の入力にそれぞれ接続され、ガンマ抵抗1両端には第1、第2の電圧が、ガンマ抵抗2両端には第3、第4の電圧が印加される。

(もっと読む)

アナログデジタル変換装置及びアナログデジタル変換方法

【課題】変換対象であるアナログ信号の信号特性に応じた分解能でデジタル信号に変換でき、かつ、その際の消費電力が削減できるようにする。

【解決手段】入力信号G1の所定の特性を検出する信号特性検出部6と、信号特性検出部により検出された信号特性に基づき分解能を設定し、該分解能のアナログデジタル変換に必要な動作のみを指示する制御信号G10を生成し、出力する制御信号生成部7と、複数のレジスタ値が格納されて、レジスタ値に対応したレジスタ信号を出力する逐次比較レジスタと、レジスタ信号をアナログ信号に変換して、基準電圧信号として出力するデジタルアナログ変換器と、入力信号と基準電圧信号とを比較して比較結果信号を出力するコンパレータと、を備える。

(もっと読む)

パイプライン型A/Dコンバータ

【課題】ディジタルPGAを含むパイプライン型A/Dコンバータであっても、ディジタルPGAの利得に関係なく、線形性エラーが発生することを抑えて、パイプライン型A/Dコンバータで生成された信号だけを増幅することができるパイプライン型A/Dコンバータを提供する。

【解決手段】ディジタル出力信号DoutのMSB側を処理するA/Dコンバータ102−1´は、制御部105´から出力されたコンパレータ出力制御信号CP1,CP1´によって導通状態が制御される出力値固定用スイッチング素子151,152を有している。ディジタルPGA202によって所定の利得に応じてそれらのスイッチング素子の導通状態を制御することによって、A/Dコンバータ102−1´,102−2´のコンパレータ出力値を固定させておき、通常動作状態のように処理途中の信号に加減算される基準電圧が切り替わらないようにしている。

(もっと読む)

サンプリング回路

【課題】サンプリング回路の低消費電力化を図る。

【解決手段】サンプリングスイッチSW1を介してサンプリングキャパシタC1が接続される出力端子2に、トランジスタM1のソースとトランジスタM2のソースを接続する。さらに、トランジスタM1のゲートと入力端子1との電位差がトランジスタM3の閾値電圧にほぼ等しくなるように制御するダイオード接続のトランジスタM3と、入力端子1と出力端子2の電位が等しくなるよう制御し、トランジスタM1のドレイン電流とトランジスタM2のドレイン電流が等しくなるように制御する演算増幅器4とを設ける。

(もっと読む)

タッチパネルコントローラおよびそれを用いた入力装置、電子機器

【課題】相互キャパシタ方式の入力装置の検出感度を改善し、または、センシング時間を短縮する。

【解決手段】送信回路20は、1回のセンシングごとに送信電極10に複数のパルス信号を含む送信信号S1を印加する。A/Dコンバータ44は、各パルス信号のポジティブエッジごとに、演算増幅器32の出力電圧に応じた検出電圧Vsをデジタル値に変換することにより第1データ系列DRを生成するとともに、各パルス信号のネガティブエッジごとに、検出電圧Vsをデジタル値に変換することにより第2データ系列DFを生成する。DSP102は、第1データ系列DRと第2データ系列DFそれぞれに含まれる、互いに対応するデジタル値の差分を算出し、各デジタル値の差分を積分する。

(もっと読む)

デジタル信号生成回路及びデジタルマイク

【課題】入力信号の温度変化をキャンセルするときの増幅利得の歪み及びバラツキを低減する。

【解決手段】デジタル信号生成回路10は、増幅ユニット12と、基準電圧生成回路142と、変調器140と、を備える。増幅ユニット12は、温度Tに線形依存する信号レベルを有するアナログ入力信号Ainを増幅する。基準電圧生成回路142は、温度Tに線形依存させて基準電圧Vrefを生成する。変調器140は、基準電圧Vrefに基づいて、増幅ユニット12が増幅したアナログ入力信号(増幅信号Ain´)をデジタル出力信号Doutに変換する。

(もっと読む)

パイプライン型A/D変換回路

【課題】セットリング誤差を線形化でき、高速で消費電力の小さいパイプライン型A/D変換回路を提供する。

【解決手段】パイプライン型A/D変換回路において、各段のA/D変換回路部に、複数の比較器を含み、入力信号をA/D変換するサブA/D変換回路と、サブA/D変換回路からのデジタル信号を、正負の参照電圧を基準値として用いて生成したアナログ制御信号にD/A変換し、アナログ制御信号に基づき、入力信号を、複数のサンプリングキャパシタを用いてサンプリングし、ホールドし、増幅してD/A変換する乗算型D/A変換回路と、後段側の乗算型D/A変換回路でサンプリングをする前に、後段側のサンプリングキャパシタを、サブA/D変換回路に含まれる複数の比較器の出力する比較結果信号に応じて、正負の参照電圧の中間電圧値に予め充電するプリチャージ回路と、を設け、セットリング誤差を線形化する。

(もっと読む)

AD変換装置およびDC−DC変換装置

【課題】基準となる二つのアナログ信号を必要とせずに、単相差動変換を含むAD変換装置におけるDCオフセットをキャンセルする。

【解決手段】本発明の一態様としてのAD変換装置は、参照電圧信号を受ける第1端子と、前記参照電圧信号を単相差動変換して第1差動信号を得る単相差動変換回路と、前記参照電圧信号に基づき、前記第1差動信号をAD変換して第1デジタル信号を得るAD変換器と、前記第1デジタル信号と、所定コードを表すデジタル信号との差分であるDCオフセットを検出するデジタル回路と、入力信号を受ける第2端子と、を備え、前記単相差動変換回路は、前記入力信号を単相差動変換して第2差動信号を取得し、前記AD変換器は、前記参照電圧信号に基づき、前記第2差動信号をAD変換して第2デジタル信号を取得し、前記デジタル回路は、前記第2デジタル信号から前記DCオフセットを減算してい第3デジタル信号とし、前記第3デジタル信号を出力する。

(もっと読む)

1 - 20 / 534

[ Back to top ]