Fターム[5J024AA09]の内容

Fターム[5J024AA09]の下位に属するFターム

同調回路、共振回路 (113)

Fターム[5J024AA09]に分類される特許

1 - 13 / 13

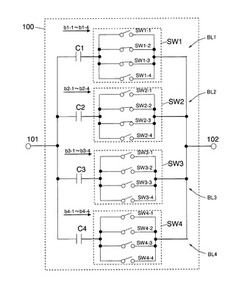

可変インピーダンス装置及び無線システム

【課題】 選択する容量の数に関わらずにそのオン抵抗を一定に保つことができる可変インピーダンス装置及びそれを用いた無線システムを提供する。

【解決手段】 一対の入出力端子101、102と、一対の入出力端子間に並列に接続された複数の回路ブロックBL1〜BL4と、を備え、回路ブロックは、一対の入出力端子の一方に一端が接続された容量性回路要素C1〜C4と、容量性回路要素の他端と一対の入出力端子の他方との間に互い並列に接続された回路ブロックの数以上の数のスイッチ素子SW1−1〜SW4−4を備えるスイッチ回路SW1〜SW4と、を備える。

(もっと読む)

可変容量素子

【課題】従来の可変容量素子は、容量値の精度が低い問題があった。

【解決手段】本発明の可変容量素子は、第1の電源端子と出力端子CTOPとの間に接続される第1の容量素子C1と、容量切替信号CSELに応じて導通状態が切り替えられる容量選択スイッチN1と、第1の容量素子C1と並列に接続され、かつ、容量選択スイッチN1と直列に接続される第2の容量素子C2と、容量選択スイッチN1が遮断状態とされる状態において、出力端子CTOPをリセット電圧にリセットする電荷リセット信号INITBに応じて、第2の容量素子C2と容量選択スイッチN1とを接続する容量切替ノードNDaの電圧と出力端子CTOPの電圧とを実質的に同じ電圧に設定する誤差補正回路10と、を有する。

(もっと読む)

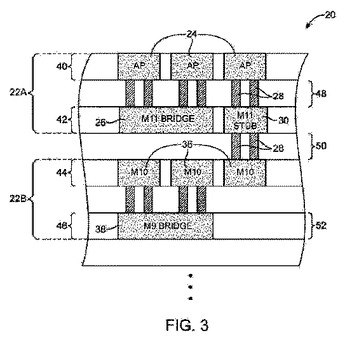

直列接続のインダクターを有する集積回路

集積回路インダクターは、直列に接続されている上部ループ形状のライン部分と下部ループ形状のライン部分とを有し得る。上部部分および下部部分は、45°曲がりを有し得、6角形または8角形のループを形成する。各ループ部分は、1つ以上のターンを有し得る。金属ルーティング層の介在する金属フリー領域が、容量性カップリングを低減させるために、2つの層の間に形成され得る。各ループ部分は、ビアによって並列にショートされた2つ以上の金属ラインのセットを有し得る。上部ループおよび下部ループは、容量性カップリングを低減させるために、横にオフセットされ、または入れ子にされ得る。  (もっと読む)

(もっと読む)

電子部品

【課題】低周波帯域で低インピーダンスを保ちつつ、高周波帯域で高インピーダンスにすることが可能な電子部品を提供する。

【解決手段】電子部品は、磁性体からなる基体1と、基体1上に形成されると共に、第1主面部2a、基体の端部に引き出されるように伸びる第1引き出し部2c、及び第1主面部2aと第1引き出し部2cとを接続する第1抵抗部2bを有する第1内部電極2と、第1内部電極2の第1主面部2aを覆う第1誘電体膜3と、第1誘電体膜3上に形成される第2主面部4a、及び当該第2主面部4aから基体1の端部に引き出されるように伸びる第2引き出し部4bを有する第2内部電極4と、を備える。第1主面部2a及び第2主面部4aは、第1誘電体膜3を間に挟んで対向することによりコンデンサ機能を呈し、第1抵抗部2b及び基体1は、協働してビーズ機能を呈する。

(もっと読む)

電子部品の実装構造

【課題】低周波帯域で低インピーダンスを保ちつつ、高周波帯域で高インピーダンスにすることが可能な電子部品の実装構造を提供する。

【解決手段】コンデンサ10及びビーズインダクタ20は、電源ライン1、2の間に直列となるように実装される。この実装構造によれば、ビーズインダクタ20の抵抗成分がコンデンサの等価直列抵抗として作用し、ビーズインダクタ20の抵抗成分は直流抵抗成分と高周波帯域で増加する損失との和で構成されるので高周波帯域でのインピーダンスを増加させることが可能になり、高周波ノイズを好適に除去することができる。又、ビーズインダクタ20は低周波帯域ではインダクタ成分が機能するため、低周波帯域でインピーダンスを小さく保つことができ、コンデンサ10を実装しているため低周波ノイズは吸収される。

(もっと読む)

分布定数型終端器

【課題】高周波領域まで良好な特性を有し、抵抗体の設計が容易である分布定数型終端器を提供する。

【解決手段】

入力信号電極009と接地用電極010との所定距離を結び、第1シート抵抗値τ1(Ω/□)の抵抗が分布する第1抵抗膜004と、第1抵抗膜004の該所定距離方向の辺と該辺に並行するアースパターン011との間に、該辺とアースパターン011に電気的に接続され、第2シート抵抗値τ2(Ω/□)の抵抗が分布する第2抵抗膜005とを備えた。

(もっと読む)

分配混合器

【課題】複数の入出力ポートを有し分配器あるいは混合器として利用でき、かつ、ノイズや反射波の影響を受けにくい分配混合器を提供する。

【解決手段】3つ以上のN個の信号入出力端子(ポート1〜6)と、ポート1〜6の何れか一に一端が接続され、他端同士が共通接続されているN本の信号伝送線路12−1〜12−6と、信号伝送線路12−1〜12−6の各々に1つずつ直列に挿入されているN個の直列抵抗14−1〜14−6と、共通接続点(分岐点13)と基準電位(GND電位)間に接続されている共通の帯域通過フィルタBPF0と、を有する。

(もっと読む)

ノイズ除去フィルタ

【課題】方向性を考慮する必要がなくまた製造上の誤差も少なく、しかも波形歪みが少ない信号を出力可能なノイズ除去フィルタを提供する。

【解決手段】ノイズ除去フィルタ1は、フェライト体2でコイル体3と抵抗体4を被覆し、外部電極5−1,5−2をフェライト体2の両端に取り付けた構成を成す。具体的には、抵抗体4をコイル体3のコイル部3A,3B間に接続し、外部電極5−1,5−2をコイル部3A,3Bの端部に接続した。そして、ノイズ除去フィルタ1のインピーダンスの抵抗成分に対するリアクタンス成分の比が0.52より大きく0.92未満になるように、抵抗体4の抵抗値を設定した。抵抗体4の抵抗値は、機器の終端にコンデンサとノイズ除去フィルタ1とで構成される直列共振回路の共振周波数における値である。10MHz〜40MHzの基本周波数で構成される信号に対して使用することが好ましい。

(もっと読む)

ノイズフィルタ

【課題】電子機器等で発生するノイズのうち、所望の周波数成分のノイズを除去することができるノイズフィルタを提供すること。

【解決手段】ノイズフィルタ1は互いに平行し対向配置された実装基板20とシャーシ30との間に配置されると共に、芯材12と当該芯材12を覆う金属メッシュ14とから形成された本体10を備えている。金属メッシュ14は、時計回り方向に向かって芯材12の第1側面12aから第2側面12bにかけて芯材12の表面に沿って設けられている。実装基板20は絶縁層40を介し本体10の金属メッシュ14に接しており、シャーシ30は直接に本体10の金属メッシュ14に接している。

(もっと読む)

フィルタ素子

【課題】広い帯域で良好なノイズ減衰効果を実現し得るコモンモード型のフィルタ素子を提供する。

【解決手段】帯状絶縁体5の一面に帯状導電体6を配設した帯状体7が複数積層された積層体8を所定方向に巻回して筒状に形成されたコイル部2と、積層体8を所定方向とは逆方向に巻回して筒状に形成されたコイル部3とを備え、両コイル部2,3は、筒状に形成された状態における内周部に位置する所定部位において各々の帯状導電体6が互いに接続されると共に、各々の帯状導電体6のうちの筒状に形成された状態における最外周に位置する帯状導電体6が接地用の帯状導電体6として機能し、かつ接地用の帯状導電体6を除く他の帯状導電体6のうちの帯状絶縁体5を挟んで隣接する複数の帯状導電体6が信号用の帯状導電体6として機能するように構成されている。

(もっと読む)

フィルタ素子

【課題】十分な耐圧を確保し得るフィルタ素子を提供することを主目的とする。

【解決手段】帯状絶縁体8a上に配設された接地用導電体9a,9bと帯状絶縁体8b上に配設された信号用導電体10a,10bとを帯状絶縁体8bを介して重ねて構成した積層体11における一端側の半分を中心部位(境界部位)Aを中心として所定方向に巻回して筒状に形成したコイル部5と、積層体11における他端側の半分を中心部位(境界部位)Aを中心としてコイル部5とは逆方向に巻回して筒状に形成したコイル部6とを備えている。

(もっと読む)

積層型ノイズフィルタ

【課題】小型化した場合にも1次の減衰極を所望の周波数帯域に生じさせることができ、かつ、加工精度に大きく依存することなく安定して製造することができ、安定した特性が実現できる積層型ノイズフィルタを提供する。

【解決手段】フィルタ本体80の側面に、側面入力端子81及び側面出力端子82を有し、フィルタ本体80が、入力端子電極31が形成された絶縁層10、積層した状態で連続して周回するコイルを構成するためのコイル形成用導体32A〜32Dが形成された複数の絶縁層10、コイル形成用導体32A〜32Dに接続されない第1の容量形成用導体33が形成された絶縁層10を有するとともに、入力端子電極31をコイル形成用導体32Aに接続し、コイル形成用導体32Dと、側面入力端子81に接続された第1の容量形成用導体33との間に第1容量C0を形成する。

(もっと読む)

電圧制御発振器

【課題】 電圧制御発振器の小型・低価格化を図りつつ、優れた発振特性が得られるようにする。

【解決手段】 電界効果型トランジスタT1、T2、可変容量素子P1、P2、バッファB1、B2および定電流源G1を半導体チップK1に形成し、インダクタL1、L2およびキャパシタC1、C2は低温焼成セラミック基板K2に形成し、低温焼成セラミック基板K2上に半導体チップK1をフェースダウン実装することにより、電界効果型トランジスタT1、T2、インダクタL1、L2およびキャパシタC1、C2にてコルビッツ差動型共振器を構成する。

(もっと読む)

1 - 13 / 13

[ Back to top ]